мой выход 22 счетного триггера JO. Контрольный регистор 8 состоит из триггеров 23.

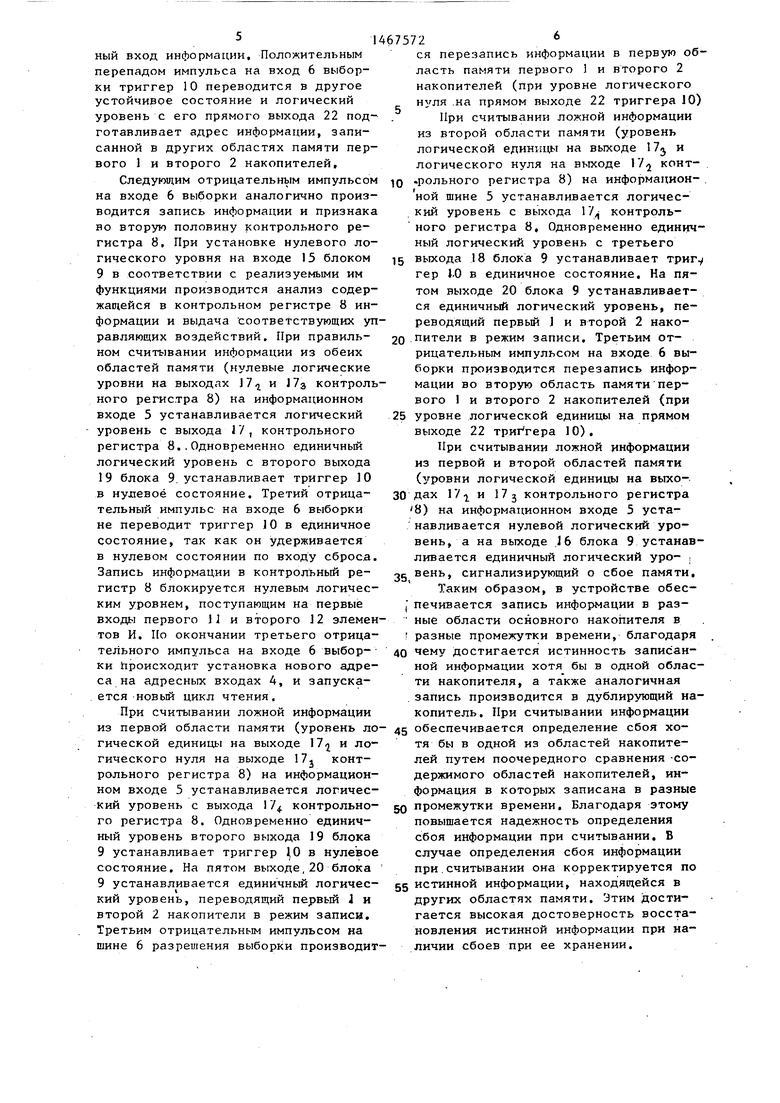

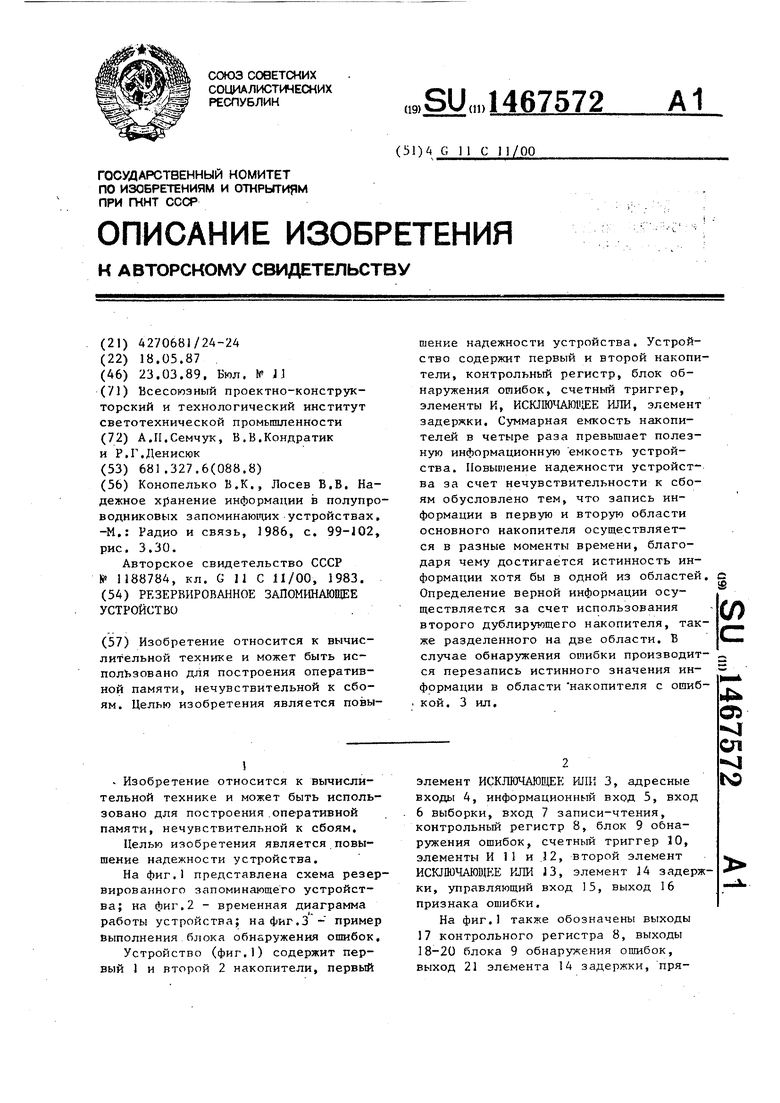

Блок 9 обнаружения ошибок (фиг,3) содержит программируемую логическую матрицу 24 и ключ 25 с тремя состояниями.

Резервированное запоминающее устройство работает следующим образом.

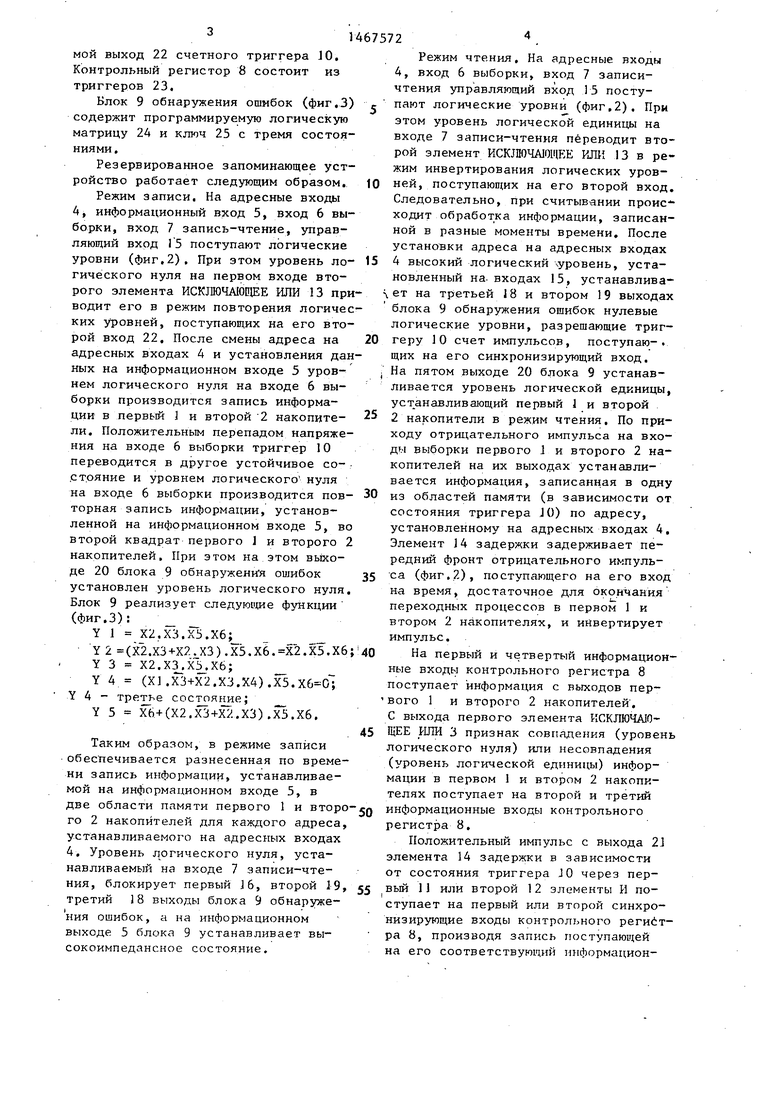

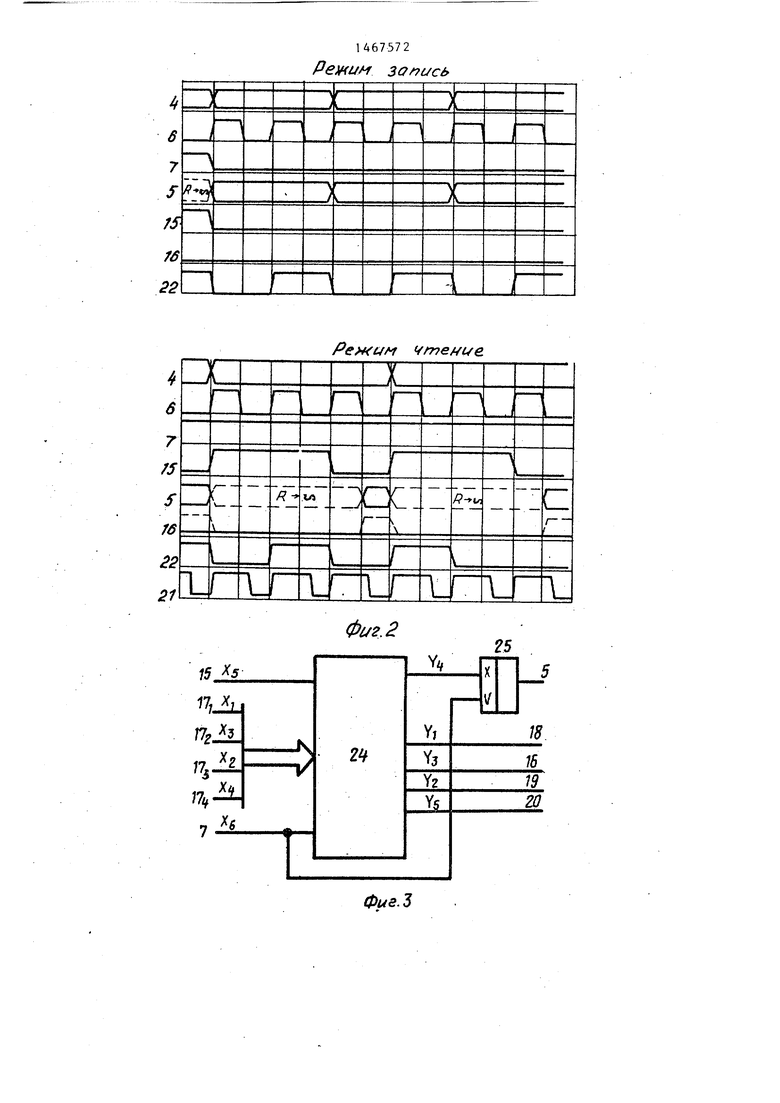

Режим записи. На адресные входы 4, информационный вход 5, вход 6 выборки, вход 7 запись-чтение, управляющий вход Г5 поступают логические уровни (фиг.2). При зтом уровень ло- гического нуля на первом входе второго элемента ИСКЛЮЧА10 ЦЕЕ ИЛИ 13 приводит его в режим повторения логических уровней, поступающих на его второй вход 22. После смены адреса на адресных входах 4 и установления данных на информационном входе 5 урон- нем логического нуля на входе 6 выборки производится запись информации в первый I и второй 2 накопители. Положительным перепадом напряжения на входе 6 выборки триггер 10 переводится в другое устойчивое состояние и уровнем логического нуля на входе 6 выборки производится повторная запись информации, установленной на информационном входе 5, во второй квадрат первого J и второго 2 накопителей. При этом на этом ВЬЁСО- де 20 блока 9 обнаружения ошибок установлен уровень логического нуля. Блок 9 реализует следуюиц1е функции (фиг.З):

Y 1 Х2.ХЗ.Х5.Х6;

Y2 (X2.X3+X2.X3).X5.X6.X2.X5.X6; Y 3 Х2.ХЗ,Х 5.Х6;

Y 4 (Х.ХЗ+Х2.ХЗ.Х4).Х5. Y 4 - третье состояние;

Y 5 Х6+(Х2.ХЗ+Х2.ХЗ).Х5.Х6.

Таким образом, в режиме записи

обеспечивается разнесенная по времени запись информации, устанавливаемой на информационном входе 5, в две области памяти первого 1 и второго 2 накопителей для каждого адреса, устанавливаемого на адресных входах 4. Уровень /логического нуля, устанавливаемый на входе 7 записи-чте

ния, блокирует первый J6, второй 19, третий 18 выходы блока 9 обнаружения ошибок, а на информационном выходе 5 блока 9 устанавливает вы- сокоимпедансное состояние.

10

25

15 20O

5

п

30

35

5

Режим чтения. На адресные входы 4, вход 6 выборки, вход 7 записи- чтения управляющий вход 15 поступают логические уровни (фиг.2). При этом уровень логической единшда на входе 7 записи-чтения переводит второй элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 13 в режим инвертирования логических уровней, поступающих на его второй вход. Следовательно, при считывании проис- ходит обработка информации, записанной в разные моменты времени. После установки адреса на адресных входах 4 высокий логический чуровень, установленный на. входах 15, устанавливачет на третьей 18 и втором 19 выходах блока 9 обнаружения ошибок нулевые логические уровни, разрешающие триггеру 10 счет импульсов, поступаю-, щих на его синхронизирующий вход.

j На пятом выходе 20 блока 9 устанавливается уровень логической единицы, уст анавливающий первый 1 и второй 2 накопители в режим чтения. По приходу отрицательного импульса на входы выборки первого 1 и второго 2 накопителей на их выходах устанавливается информация, записанная в одну из областей памяти (в зависимости от состояния триггера JO) по адресу, установленному на адресных входах 4. Элемент 14 задержки задерживает передний фронт отрицательного импульса (фиг.2), поступающего на его вход на время, достаточное для окончания переходных процессов в первом 1 и втором 2 накопителях, и инвертирует импульс.

На первый и четвертый информационные входы контрольного регистра 8 поступает информация с выходов пер вого 1 и второго 2 накопителей . С выхода первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 3 признак совпадения (уровень логического нуля) или несовпадения (уровень логической единицы) информации в первом 1 и втором 2 накопителях поступает на второй и третий информационные входы контрольного регистра 8.

Положительный импульс с выхода 2J элемента 14 задержки в зависимости от состояния триггера JO через 11 или второй 12 элементы И поступает на первый или второй синхронизирующие входы контрольного реги(:т- ра 8, производя запись поступающей на его соответствующий информационный вход информации. Положительным перепадом импульса на вход 6 выборки триггер 10 переводится в другое устойчивое состояние и логический уровень с его прямого выхода 22 подготавливает адрес информации, записанной в других областях памяти первого 1 и второго 2 накопителей.

Следующим отрицательнь1м импульсом на входе 6 выборки аналогично производится запись информации и признака во вторую половину контрольного регистра 8, При установке нулевого логического уровня на входе 15 блоком 9 в соответствии с реализуемыми им функциями производится анализ содержащейся в контрольном регистре 8 информации и выдача соответствующих управляющих воздействий. При правильном считывании информации из обеих областей памяти (нулевые логические уровни на выходах J7 и 7з контрольного регистра 8) на информационном входе 5 устанавливается логический уровень с выхода Г/, контрольного регистра 8,,Одновременно единичный логический уровень с второго выхода 19 блока 9. устанавливает триггер 10 в нулевое состояние. Третий отрицательный импульс на входе 6 выборки не переводит триггер 0 в единичное состояние, так как он удерживается в нулевом состоянии по входу сброса. Запись информации в контрольный регистр 8 блокируется нулевым логическим уровнем, поступающим на первые входы первого 1J и второго 12 элементов И, По окончании третьего отрицательного импульса на входе 6 выборки происходит установка нового адреса на адресных входах 4, и запускается новый цикл чтения.

При считывании ложной информации

1467572

ся перезапись информации в первую область памяти первого 1 и второго 2 накопителей (при уровне логического J. нуля .на прямом выходе 22 триггера 10)

При считывании ложной информации из второй области памяти (уровень

логической единицы на выходе 17j и логического нуля на выходе IV конт 0 -рольного регистра 8) на информацион- ной шине 5 устанавливается логический уровень с выхода 17 контрольного регистра В, Одновременно единичный логический уровень с третьего

15 выхода 18 блока 9 устанавливает триг гер Ш в единичное состояние. На пятом выходе 20 блока 9 устанавливается единичный логический уровень, переводящий первый 1 и второй 2 нако20 пители в режим записи. Третьим отрицательным импульсом на входе 6 выборки производится перезапись информации во вторую область памяти первого 1 и второго 2 накопителей (при

25 уровне логической единицы на прямом выходе 22 триг гера 10),

При считывании ложной информации из первой и второй областей памяти (уровни логической единицы на выхо30 дах 17-j и 17 3 контрольного регистра 8) на информационном входе 5 устанавливается нулевой логический уровень, а на выходе 16 блока 9 устаиав ливается единичный логический уро- i

25 вень, сигнализирующий о сбое памяти. Таким образом, в устройстве обес- печивается запись информации в раз- ные области основного накопителя в разные промежутки времени, благодаря

40 чему достигается истинность записанной информации хотя бы в одной области накопителя, а также аналогичная .запись производится в дублирующий иа копитель. При считывании информации

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с самоконтролем | 1989 |

|

SU1718276A1 |

| Устройство для контроля оперативной памяти | 1988 |

|

SU1531177A1 |

| Запоминающее устройство на цилиндрических магнитных доменах | 1990 |

|

SU1737510A1 |

| Запоминающее устройство с самоконтролем | 1983 |

|

SU1104588A1 |

| Процессор полупроводниковой внешней памяти высокопроизводительной вычислительной системы | 1987 |

|

SU1539789A1 |

| Устройство для сопряжения процессора с памятью | 1982 |

|

SU1059560A1 |

| Запоминающее устройство на цилиндрических магнитных доменах | 1990 |

|

SU1737511A1 |

| Динамическое запоминающее устройство с коррекцией ошибок | 1983 |

|

SU1133625A1 |

| Запоминающее устройство с исправлением ошибок | 1982 |

|

SU1128294A1 |

| Запоминающее устройство с самоконтролем | 1988 |

|

SU1522292A1 |

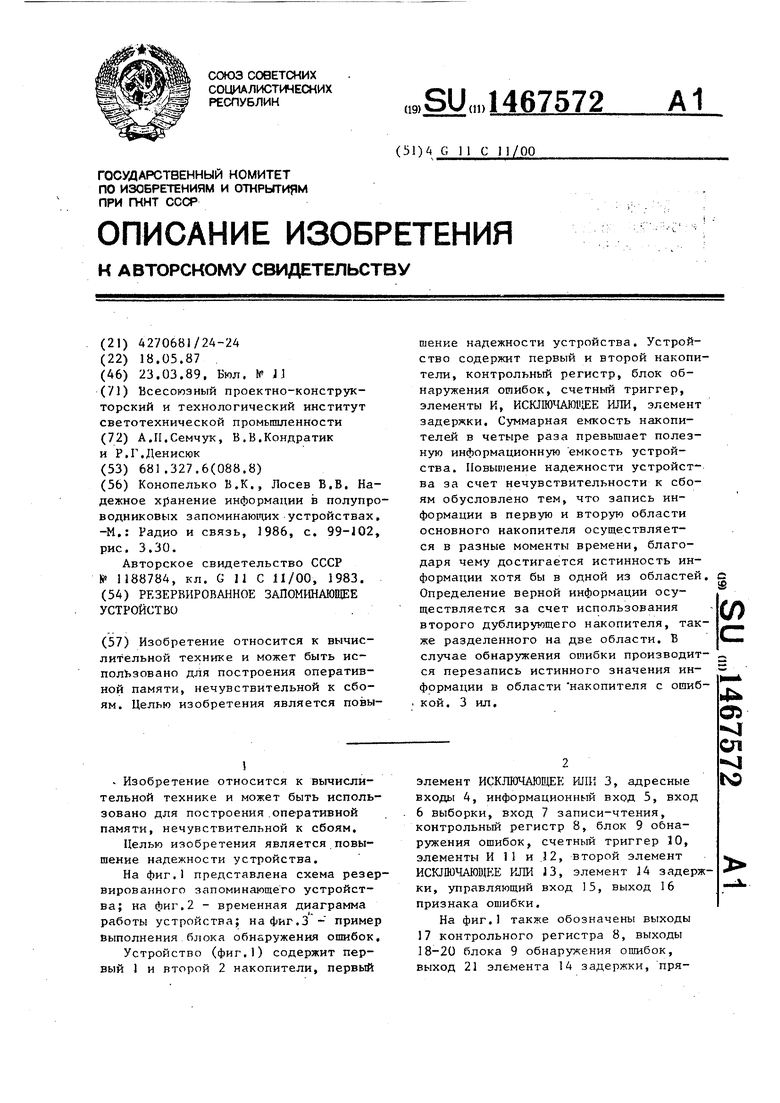

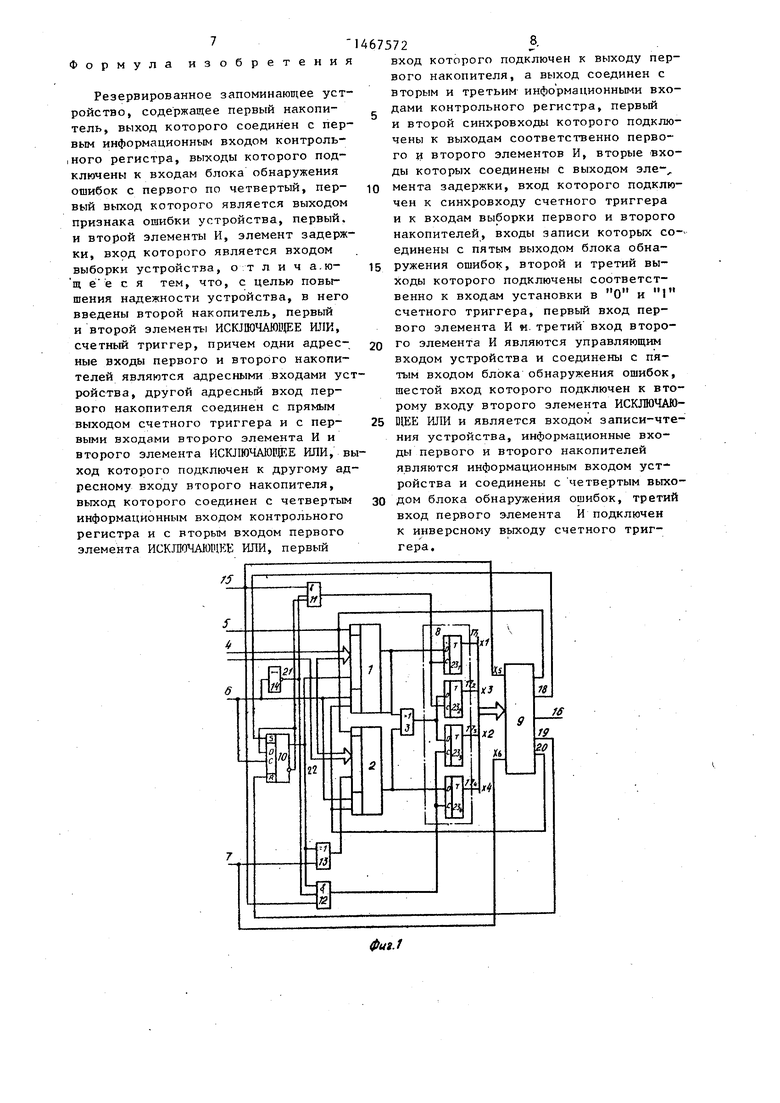

Изобретение относится к вычислительной технике и может быть ис- полЬзовано для построения оперативной памяти, нечувствительной к сбоям. Целью изобретения является повы - Изобретение относится к вычислительной технике и может быть использовано для построения.оперативной памяти, нечувствительной к сбоям. Целью изобретения является повышение надежности устройства. На фиг,1 представлена схема резервированного запоминающего устройства; на фиг.2 - временная диаграмма работы устройства; на фиг.3 - пример Выполнения блока обнаружения ошибок. Устройство (фиг.1) содержит первый 1 и второй 2 накопители, первый шение надежности устройства. Устройство содержит первый и второй накопители, контрольный регистр, блок обнаружения ошибок, счетный триггер, элементы И, ИСКЛЮЧАЮ1ЦЕЕ ИЛИ, элемент задержки. Суммарная емкость накопителей в четыре раза превышает полезную информационную емкость устройства. Цовыв ение надежности устройства за счет нечувствительности к сбоям обусловлено тем, что запись информации в первую и вторую области основного накопителя осуществляется в разные моменты времени, благодаря чему достигается истинность информации хотя бы в одной из областей. Определение верной информации осуществляется за счет использования второго дублирующего накопителя, также разделенного на две области. В случае обнаружения ошибки производится перезапись истинного значения информации в области накопителя с ошибкой. 3 ил. i элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 3, адресные входы 4, информационный вход 5, вход 6 выборки, вход 7 записи-чтения, контрольный регистр 8, блок 9 обнаружения ошибок, счетный триггер 10, элементы И 11 и .12, второй элемент ИСКЛЮЧАЮВЩЕ ИЛИ 13, элемент 14 задержки, управляющий вход 15, выход 16 признака ошибки. На фиг.1 также обозначены выходы 17 контрольного регистра 8, выходы 18-20 блока 9 обнаружения ошибок, выход 21 элемента 14 задержки, пря(Л 4 О М ел - to

и ло- контиз первой области памяти (уровень ло- 45 обеспечивается определение сбоя хотя бы в одной из областей накопителей путем поочередного сравнения -содержимого областей накопителей, информация в которых записана в разиые

Кий уровень с выхода 17 контрольно- 50 промежутки времени. Благодаря этому

гической единицы на выходе 17/ гического нуля на выходе 17j рольного регистра 8) на информациои- ном входе 5 устанавливается логичесго регистра 8. Одновременно единичный уровень второго выхода 19 блока 9 устанавливает триггер 0 в нулевое состояние. На пятом выходе,20 блока 9 устанавливается единичньй логический уровень, переводящий первый I и второй 2 накопители в режим записи, Третьим отрицательным импульсом на шине 6 разрешения выборки производитповышается надежность определения сбоя информации при считывании, В случае определения сбоя информации при.считывании она корректируется по 55 истинной информации, находящейся в других областях памяти. Этим достигается высокая достоверность восстановления истинной информации при иа- личии сбоев при ее хранении.

повышается надежность определения сбоя информации при считывании, В случае определения сбоя информации при.считывании она корректируется по 55 истинной информации, находящейся в других областях памяти. Этим достигается высокая достоверность восстановления истинной информации при иа- личии сбоев при ее хранении.

VfTfCA/i e

Фиг. 2

25

| КонопеЛько В.К., Лосев В.В | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| -М.: Радио и связь, 1986, с | |||

| Прибор, замыкающий сигнальную цепь при повышении температуры | 1918 |

|

SU99A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Запоминающее устройство с самоконтролем | 1983 |

|

SU1188784A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1989-03-23—Публикация

1987-05-18—Подача