(54) ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С БЛОКИРОВКОЙ НЕИСПРАВНЫХ ЗАПОМИНАЮЩИХ ЯЧЕЕК

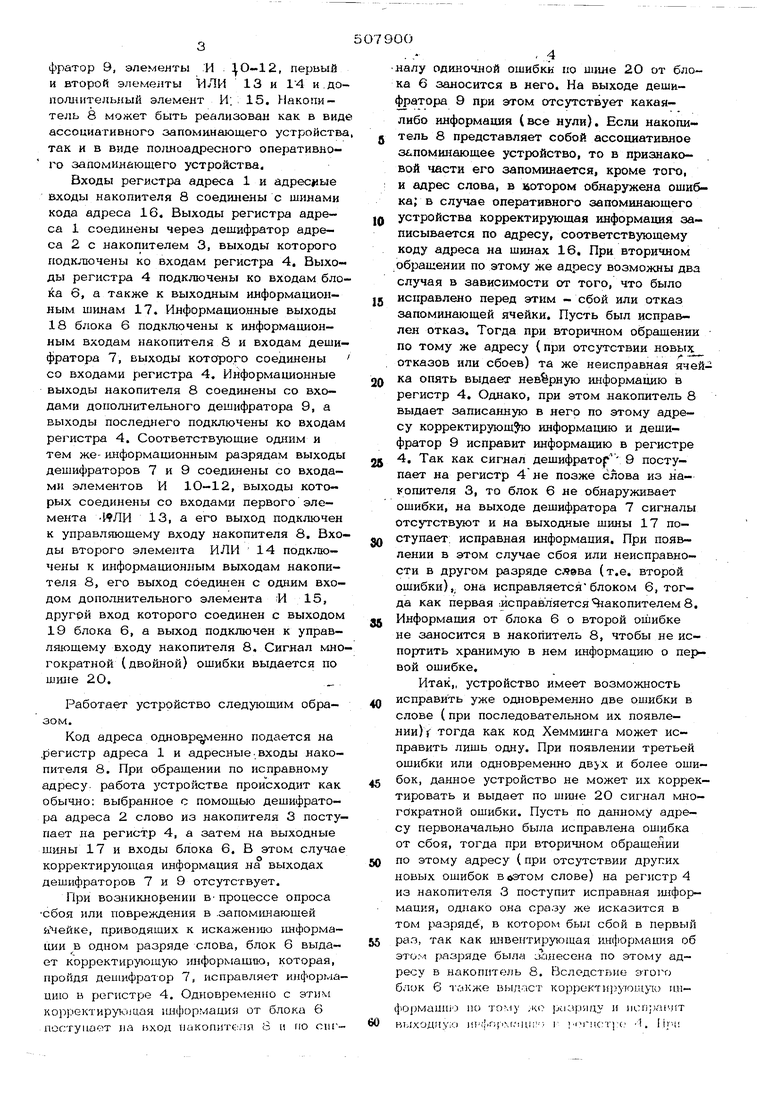

фратор 9, элементы И , первый и второй элемелты Т-1ЛИ 13 и 14 и.дополиительлый элемент И; : 15. Накопитель 8 может быть реализован как в виде ассоциативного запоминающего устройства, так и в виде поляоадресного оперативного запоминающего устройства.

Входы регистра адреса 1 и адрес ые входы накопителя 8 соединены с щинами кода адреса 16. Выходы регистра адреса 1 соединены через дешифратор адреса 2 с накопителем 3, выходы которого подключены ко входам регистра 4. Выходы регистра 4 подключены ко входам блоlia 6, а также к выходным информационным шинам 17. Информационные выходы

18блока 6 подключены к информационным входам накопителя 8 и входам дешифратора 7, выходы которого соединены со входами регистра 4. Информационные выходы накопителя 8 соединены со входами дополнительного дешифратора 9, а выходы последнего подключены ко входам регистра 4. Соответствующие одним и тем же- -шформационным разрядам выходы дешифраторов 7 и 9 соединены со входами элементов И 1О-12, выходы которых соединены со входами первого элемента 13, а его выход подключен к управляющему входу накопителя 8. Входы второго элемента ИЛИ 14 подключены к информационным выходам накопителя 8, его выход соединен с одним входом дополнительного элемента MIS, другой вход которого соединен с выходом

19блока 6, а выход подключен к управляющему входу накопителя 8. Сигнал многократной (двойной) ошибки выдается по шине 2О.

Работает устройство следующим образом.

Код адреса одновр енно подается на регистр адреса 1 и адресные. входы накопителя 8. При обращении по исправному адресу работа устройства происходит как обычно: выбранное с помощью дешифратора адреса 2 слово из накопителя 3 поступает на регистр 4, а затем на выходные щины 17 и входы блока 6. В этом случае корректирующая информация на выходах дешифраторов 7 и 9 отсутствует.

При возникно5 ении в процессе опроса сбоя или повреждения в .запоминающей 51чейке, приводящих к искажению 1шформации в одном разряде слова, блок 6 выдает корректирующую информацию, которая, пройдя дешифратор 7, исправляет информацию Б регистре 4. Одновременно с этим корректир К11цая информация от блока 6 постуиа:-: Т ла вход иакопитеЛя 8 и гю ciirналу одиночной ошибки по шине 20 от блока 6 заносится в него. На выходе дешифратора 9 при этом отсутствует какаялибо информация (все нули). Если накоаитель 8 представляет собой ассоциативное а помш1ающее устройство, то в признаковой части его запоминается, кроме того, и адрес слова, в иотором обнаружена ошибка; в случае оперативного запоминающего

устройства корректирующая информация записывается по адресу, соответствующему коду адреса на шинах 16. При вторичном обращении по этому же адресу возможны два случая в зависимости от того, что было

исправлено перед этим - сбой или отказ запоминающей ячейки. Пусть был исправлен отказ. Тогда при вторичном обращении по тому же адресу (при отсутствии новых отказов или сбоев) та же неисправная ячейка опять выдает неверную информацию в регистр 4. Однако, при этом накопитель 8 выдает записанную в него по этому адресу корректирующею информацию и дещифратор 9 исправит информацию в регистре

. Так как сигнал дещифрато 9 поступает на регистр 4 не позже Слова из накопителя 3, то блок 6 не обнаруживает ощибки, на выходе дешифратора 7 сигналы отсутствуют и на выходные шины 17 поступает; исправная информация. При появлении в этом случае сбоя или неисправности в другом разряде слева (т.е. второй ощибки),, она исправляетсяблоком 6, тогда как первая управляется Накопителем 8.

Информация от блока 6 о второй ошибке не заносится в накопитель 8, чтобы не испортить хранимую в нем информацию о ошибке.

Итак,, устройство имеет возможность исправить уже одновременно две ошибки в слове (при последовательном их появле- нии)у тогда как код Хемминга может исправить лишь одну. При появлении третьей ошибки или одновременно и более оши-

бок, данное устройство не может их корректировать и выдает по шине 20 сигнал многократной ошибки. Пусть по данному адресу первоначально была исправлена ошибка от сбоя, тогда при вторичном обращении

по этому адресу (при отсутствии других новых ошибок в «этом слове) на регистр 4 из накопителя 3 поступит исправная информация, однако она сразу же исказится в том разряде, в котором был сбой в первый

раз, так как инвентируклцая информация об этом разряде была зЪ.песана по этому адресу Б накопитель 8. Вслодстьне этого бл.)к 6 также выдаст корректи))у/ои1 1о пи-

(iiopMauMJ.) по тому /ко р113ряцу и iicnjwfMiT втлходиую црфг;р(, г i.i niC-Tj: -1. llpc.

этом на выходах дешифраторов 7 и 9, относ$шшхся к этому разряду, возникнут одинаковые состояния, которые поступят на один из элементов И 10,11,12 и далее на элемент ИЛИ 13, сигнал от которого осуществляет стирание корректирующей информации по данному адресу. Таким образом накопитель 8 освобождается от слу; чайной информации сбоев и в нем хранит- ся только информация об отказах. Если же ; после первого исправления информации от сбоя при вторичном обращении по этому адресу возникает еще одна ошибка, то блок 6 реагирует как и в случае многократной (двойной) ошибки и выдает сигнал об этом по шине 20.

Итак, данное устройство дает возможность одновременно автоматически исправлять до двух ошибок в слове. В случае необходимости увеличения корректирующей способности устройства в него нужно ввести несколько накопителей (типа накопителя 8) со своими дешифраторами, обеспечив схемным путем поочередную запись корректирующей информации в них от блока 6, а также необходимо построить соответствующую схему стирания случайной информации от сбоев.

В случае применения предложенного

устройства в составе оперативного запо-

минаюшего устройства приведенную на черьтеже блок - схему необходимо дополнить

соответствующими схемами записи; длина

слов в блоке 6 должна быть увеличена г один разряд для хранения информации, заносимой при оперативной записи в испорченный разряд слова.

Формула изобретения

Запоминающее устройство с блокировкой неисправных запоминающих ячеек, содержащее адресный олок, соединенный с накопителем, регистр, выходы которого подключены к блоку кодирования, соедиi ненному с дешифратором, элементы И и

|1ИЛИ , о т л и ч а ю щ е е с я тем, j что, с целью повышения надежности рабоI ты устройства, оно содержит дополнитель ; ный дешифратор и дополнительный накопи, тель, адресные входы которогй подключе; ны ко Входам адресного блока, информационные входы - к выходам блока кодирования, а информационные выходы - ко входам дополнительного дешифратора, выходы которого соединены со ходами регистра, выходы дешифраторов соединены со входами элементов И , выходы которых через первый элемент ИЛИ подключены к одному управляющему входу дополнительного накопителя, информационные выходы кото- рого через второй элемент ИЛИ соединены с одним входом дополнительного элеI мента И , другой вход которого подклюi чен к выходу блока кодирования, а выход ; соед1шен с другим управляющим входом до полнительного накопителя.

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с блокировкой неисправных элементов памяти | 1976 |

|

SU641503A1 |

| Запоминающее устройство с блокировкой неисправных ячеек | 1974 |

|

SU492000A1 |

| Запоминающее устройство с самоконтролем | 1989 |

|

SU1718276A1 |

| Оперативное запоминающее устройство с блокировкой неисправных запоминающих элементов | 1975 |

|

SU556502A1 |

| Оперативное запоминающее устройство с самоконтролем | 1974 |

|

SU516101A1 |

| Запоминающее устройство | 1981 |

|

SU1014042A1 |

| Запоминающее устройство | 1975 |

|

SU560255A2 |

| Запоминающее устройство с самоконтролем | 1978 |

|

SU746744A1 |

| Постоянное запоминающее устройство | 1972 |

|

SU527742A1 |

| Запоминающее устройство | 1985 |

|

SU1295456A1 |

Авторы

Даты

1976-03-25—Публикация

1974-08-13—Подача