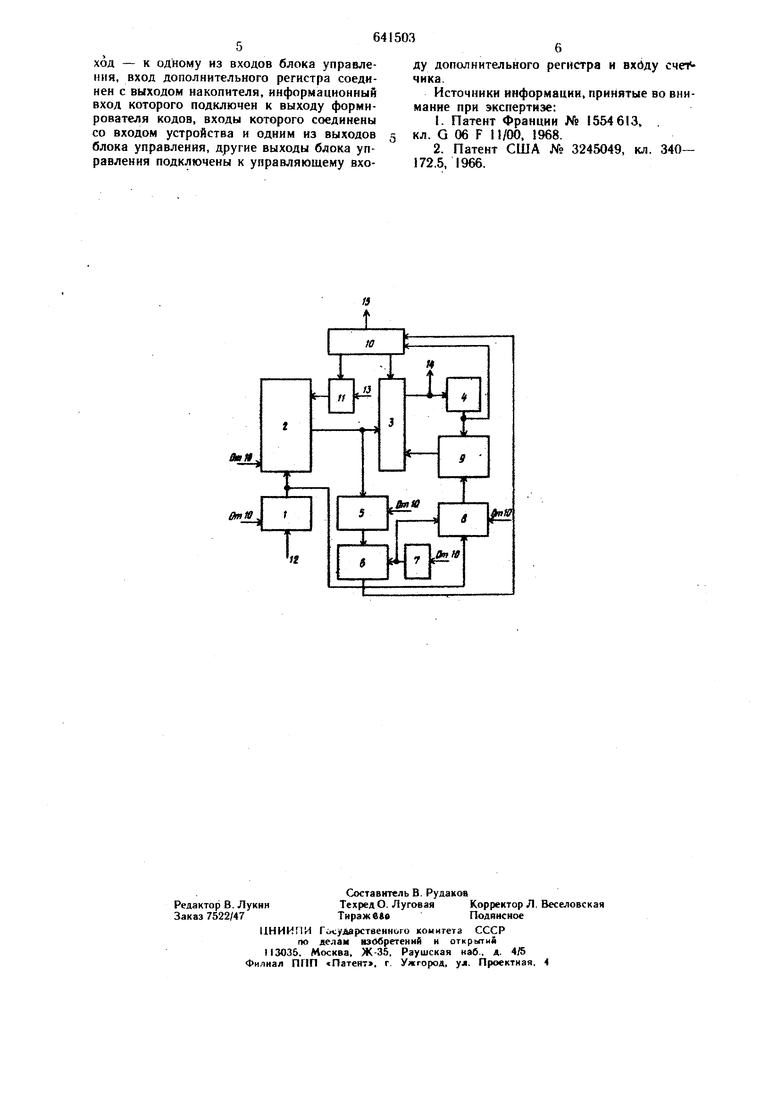

ля 4, дополнительный регистр 5, выпояиенный на триггерах со счетным вх-одол5, коммутатор 6, счетчик 7, 11онш1нительный накопитель 8, дешифратор 9, блок управления 10. формирователь колов П, шины адреса 12, вход устройства 13, шины 14 и 15.

Входы регистра 1 соединены с шинами адреса 12, а выходы - с адресными входами накопителей 8 и 2. Инфо{)мационные выходы накопителя 2 подключены к входам регистров 3 и 5. Выходы регистра 3 подключены ко входам блока контроля 4, выход которого подключен к входу управления дешифратора 9 и одному из входов блока управления iO.

. Первый вход коммутатора 6 подключен к выходу счетчика 7 и информационному входу накопителя 8, второй вход выходу регистра 5, а выход - к одному из входов блока управления 10. Информационный вход накопителя 2 подключен к выходу формирователя кодов И, входы которого соединены со входом устройства 13 и одним из выходов блока управления 10, другие выходы блока управления 10 подключены к управляющему входу регистра 5 и входу счетчика 7.

Устройство работает следующим образом. При считывании код адреса по шинам 12 поступает на регистр I и далее на накопитель 2. Считанное по данному адресу слово принимается регистром 3 и проверяется блоком контроля 4. Если слово исправно, то оно поступает на входные шины 14. При обнаружении блоком контроля 4 ошибки блок управления 10 производит анализ, который выявляет, произошел сбой или отказ ЭП (например, многократным считыванием по данному адресу). 1Если произошел сбой, то при повторных считываниях информация восстановится и будет выдана на шины 14.

Если выясняется, что произошел отказ ЭП, то блок управления 10 реализует следующую программу.

Сигналами от блока 10 фиксируется код адреса на регистре 1 и считанная из накопителя искаженная информация на регистре 3. Формирователь f 1 под воздействием сигналов управления от блока 10 выдает в накопитель 2 либо информацию шин 13 {при обычной работе ЗУ), либо «1 или. «О по всем разрядам {в случае отказа ЭП). При обнаружении отказа ЭП в накопитель 2 по фиксированному адресу заносятся все «О. Затем информация считывается и принимается в регистр 5 (который до этого был в нулевом состоянии), после чего по данному адресу записываются все «1. После считывания информация данного адреса суммируется по модулю 2 с содержимым регистра 5. В разрядах регистра 5, соответствующих исправным ЭП данного адреса, после этой программы будут храниться «1, а в неисправном разряде - «О. Полученная в регистре 5 .информация фиксируется, а на счетчик 7 от блока 10 начинают поступать счетные импульсы. Под управлением сигналов на выходах счетчика 7 коммутатор 6 последовательно выдает в блок 10 содержимое каждого разряда регистра 5. Если очередной разряд содержит «1, то на счетчик 7 поступает следующий счетный импульс и проверяется содержимое следующего разряда. Так происходит до тех пор, пока не окэжется, что очередной проверяемый разряд содержит «О.

При этом блок 10 фиксирует состояние счетчика 7 и его выходную информацию записывает в дополнительный накопитель 8, одновременно запоминая в нем код неисправного адреса.

После этого на счетчик 7 вновь поступают счетные сигналы до тех пор, пока не будет проверено содержимое всех остальных разрядов. Если в слове еще обнаружены отказавшие разряды, то блок 10 выдает сигнал о невозможности коррекции по шине 15.

Если неисправных разрядов больше нет, то информация, записанная в накопитель 8, выдается иа дешифратор 9, который корректирует информацию в регистре 3, и ЗУ продолжает работать.

В дальнейшем, при обращении к данному адресу и при наличии сигнала ошибки от блока 4 накопитель 8 автоматически исправит информацию неисправного адреса.

Таким образом, предложенное устройство позволяет автоматически исправлять искаженную отказом ЭП информацию и в-дальнейшем блокировать неисправный ЭП.

При необходимости можно повысить корректирующую способность устройства, увеличив число накопителей 8 и соответствующих им дешифраторов 9.

Формула изобретения

Заяоминаюш1ее устройство с блокировкой неисправных элементов памяти, содержащее накопитель, адресный вход которого подключен к адресному входу дополнительного накопителя и выходу регистра адреса, а выход - к одному из входов регистра числа, дешифратор, входы которого соединены соответственно с выходами дополнительного накопителя и блока контроля, а выход - с

другим входом регистра числа, выход которого подключен ко входу блока контроля, и блок управления, отличающееся тем, что, с целью повышения надежности устройства, оно содержит дополнительный регистр, формирователь кодов, счетчик и коммутатор,

первый вход которого подключен к выходу счетчика и информационному входу дополнительного накопителя, второй вход - к выходу дополнительного регистра, а выход - к одному из входов блока управления, вход дополнительного регистра соединен с выходом накопителя, информационный вход которого подключен к выходу формирователя кодов, входы которого соединены со входом устройства и одним из выходов блока управления, другие выходы блока управления подключены к управляющему входу дополнительного регистра и вхбду счет чика.

Источники информации, принятые во внимание при экспертизе:

1.Патент Франции Nt 1554613, кл. G 06 F 11/00, 1968.

2.Патент США № 3245049, кл. 340- 172.5, 1966.

| название | год | авторы | номер документа |

|---|---|---|---|

| Оперативное запоминающее устройство с блокировкой неисправных запоминающих элементов | 1975 |

|

SU556502A1 |

| Оперативное запоминающее устройство с самоконтролем | 1974 |

|

SU516101A1 |

| ЗАПОМИНАНМЦЕЕ УСТРОЙСТВО С БЛОШРОВКОЙ НЕИСПРАВНЫХ ЯЧЕЕК ПАМЯТИ | 1979 |

|

SU826425A1 |

| Динамическое запоминающее устройство с коррекцией ошибок | 1988 |

|

SU1587600A2 |

| Запоминающее устройство с блокировкой неисправных ячеек | 1974 |

|

SU492000A1 |

| Устройство для имитации неисправностей | 1987 |

|

SU1444775A1 |

| Оперативное запоминающее устройство | 1974 |

|

SU495712A1 |

| Запоминающее устройство с автономным контролем | 1980 |

|

SU903990A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1973 |

|

SU368647A1 |

| Микропрограммный процессор | 1981 |

|

SU980095A1 |

Авторы

Даты

1979-01-05—Публикация

1976-09-17—Подача