1

Изобретение относится к облает вычислительной техники и может быть иоюльзовано в цифровых вычислительных машинах.

.Известно постоянное запоминающее устройство (ПЗУ) с исправлением информации дефектных запоминающих элементов (разрядов), содержащее регистр адреса, дешифратор кода адреса, накопитель, в котором каждое слово (информация) представляется дважды, в прямом и дополнительном кодах. При обращении к адресу с неисправными разрядами специальным детектором эти ошибки обнаруживаются, выдается сигнал, запрещающий постзпление неисправной информации на выход ПЗУ и осуществляется обращение по новому адресу, в котором хранится информация в дополнительном коде. Считанная вновь информация инвертируется и передается на выход ПЗУ в прямом коде.

При такой организации ПЗУ не обнаруживается, а следовательно, не исправляется четное число неисправностей, увеличивается оборудование, так как информация хранится в прямом и дополнительном кодах, затрудняется изменение информации в каком-либо адресе и снижается надежность ПЗУ.

Цель изобретения - повышение надежности ПЗУ.

Для этого оно содержит по одному на каждьш

разряд блоку сложения по модулю два, один вход

которого соединен с выходом элемента ИЛИ,

указывающего на неисправность, а другой вход - с

соответствующим выходом накопителя.

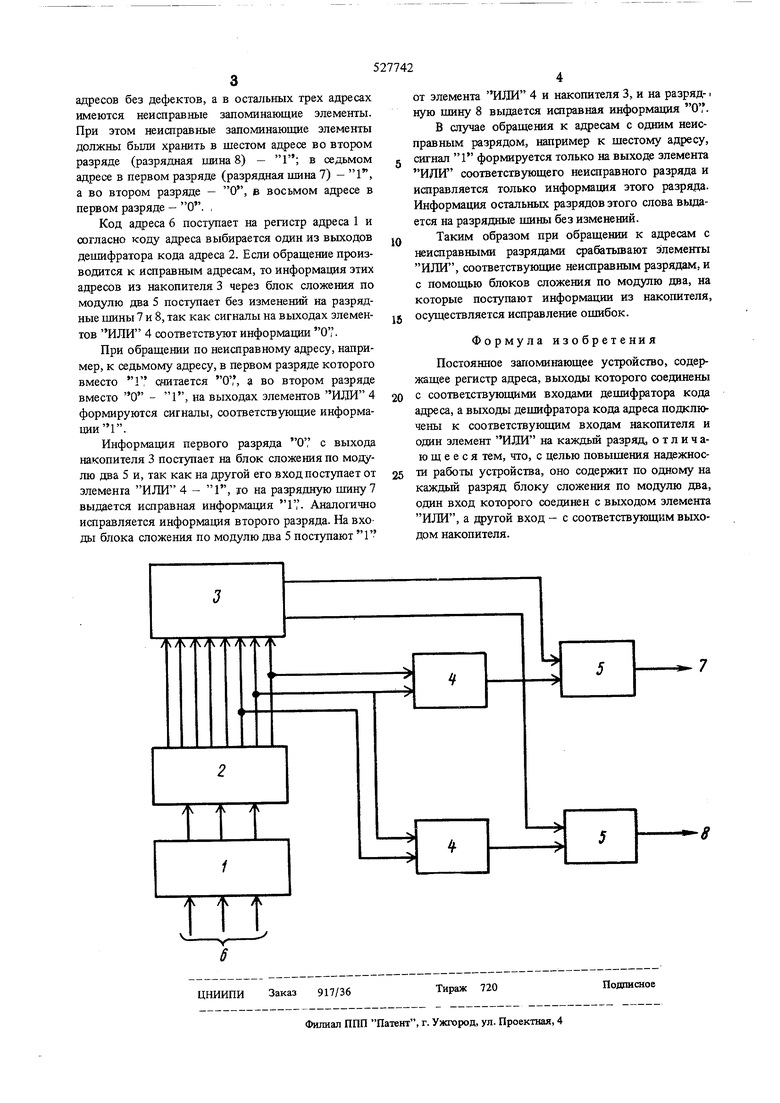

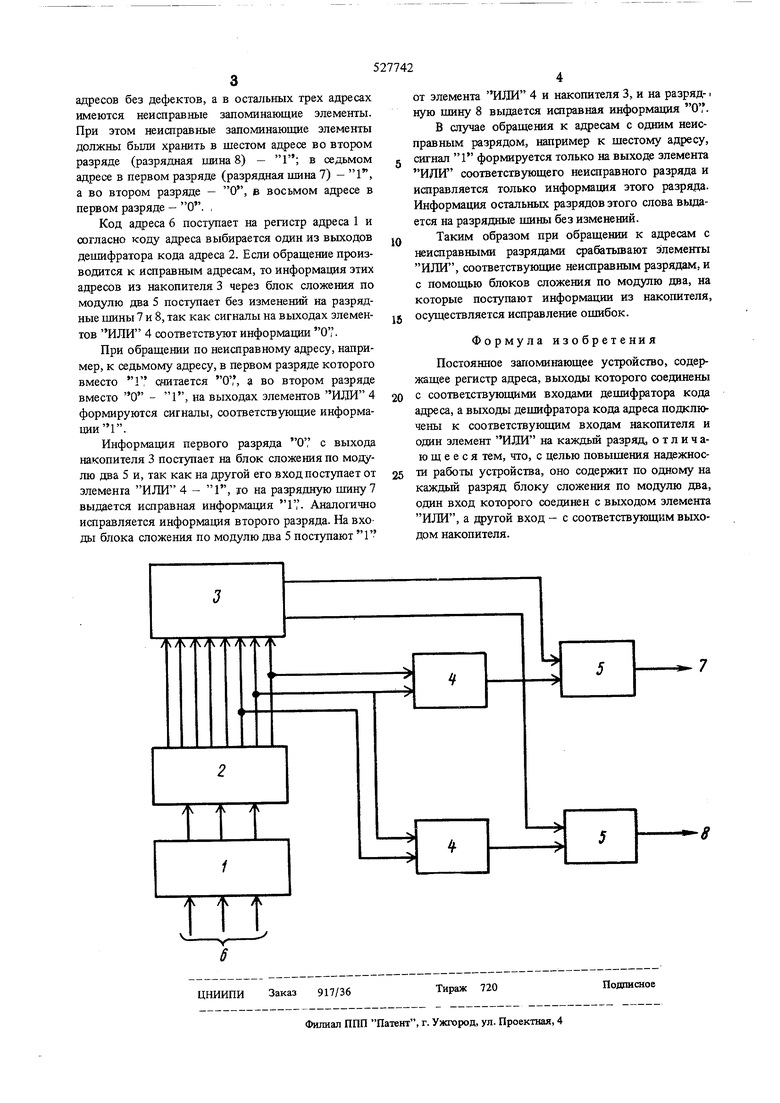

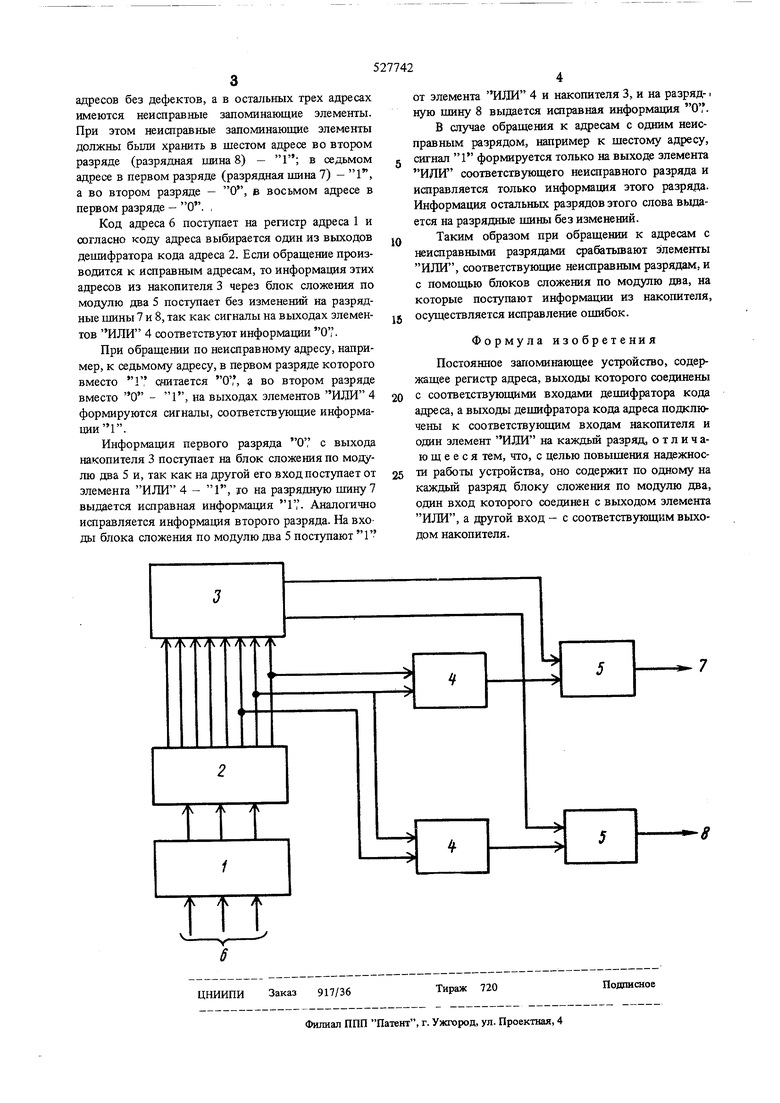

На чертеже приведена блок-схема предлагаемого постоянного запоминающего устройства.

Устройство содержит регистр адреса 1, деашфратор 2 кода адреса, накопитель 3, элементы ИЛИ 4, блоки сложения по модулю два 5.

Входы регистра адреса 1 соединены с адресными щинами 6, а выходы - с соответствующими входами дешифратора кода адреса 2. Выходы дешифратора кода адреса 2 подключены к соответствующим входам накопителя 3. Входы элементов ИЛИ 4 связаны с теми выходами дешифратора кода адреса адресах которых имеются неисправные разряды. Выходы накопителя 3 подключены к входам соответствующего блока сложения по модулю два 5, другой вход которых соединен с выходом соответствующего элемента ИЛИ 4. Выходы блоков сложения по модулю два 5 соединенв с соответствующими разрядными щинами 7 и 8.

В рассматриваемом ПЗУ на восемь адресов по два разряда в каждом считается, что первые пять адресов без дефектов, а в остальных трех адресах имеются неисправные заполшнающие элементы. При этом неисправные запоминающие элементы должны были хранить в шестом адресе во втором разряде (разрядная шина 8) - в седьмом адресе в первом разряде (разрядная шина 7) - 1, а во втором разряде - О, в восьмом адресе в первом разряде - О. , Код адреса 6 поступает на регистр адреса 1 и согласно коду адреса выбирается один из выходов дешифратора кода адреса 2. Если обращение производится к исправным адресам, то информация этих адресов из накопителя 3 через блок сложения по модулю два 5 поступает без изменений на разрядные шины 7 и 8, так как сигналы на выходах элементов ИЛИ 4 соответствуют информации О ,. При обращении по неисправному адресу, например, к седьмому адресу, в первом разряде которого вместо 1 считается О ,, а во втором разряде вместо О - 1, на выходах элементов ИЛИ 4 формируются сигналы, соответствующие информации. Информация первого разряда О , с выхода накопителя 3 поступает на блок сложения по модулю два 5 и, так как на другой его вход поступает от элемента ИЛИ 4 - 1, то на разрядную шину 7 выдается исправная информация Г,. Аналогично исправляется информация второго разряда. На входы блока сложения по модулю два 5 поступают Г от элемента ИЛИ 4 и накопителя 3, и на разряд-1 ную шину 8 выдается ишравная информация О ,. В случае обращения к адресам с одним неисправным разрядом, например к шестому адресу. сигнал 1 формируется только на выходе элемента ИЛИ соответствующего неисправного разряда и исправляется только информация этого разряда. Информация остальных разрядов этого слова выдается на разрядные шины без изменений. Таким образом при обращении к адресам с неисправными разрядами срабатьшают элементы ИЛИ, соответствующие неисправным разрядам, и с помощью блоков сложения по модулю два, на которые поступают информации из накопителя, осуществляется исправление ошибок. Формула изобретения Постоянное загюминающее устройство, содержащее регистр адреса, выходы которого соединены с соответствующими входами дешифратора кода адреса, а выходы дешифратора кода адреса подключены к соответствующим входам накопителя и один элемент ИЛИ на каждый разряд, отличающееся тем, что, с целью повышения надежности работы устройства, оно содержит по одному на каждьш разряд блоку сложения по модулю два, один вход которого соединен с выходом элемента ИЛИ, а другой вход - с соответствующим выходом накопителя.

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с блокировкой неисправных запоминающих ячеек | 1974 |

|

SU507900A1 |

| Запоминающее устройство с блокировкой неисправных элементов памяти | 1976 |

|

SU641503A1 |

| Оперативное запоминающее устройство с самоконтролем | 1974 |

|

SU516101A1 |

| Оперативное запоминающее устройство | 1975 |

|

SU559282A1 |

| Оперативное запоминающее устройство с блокировкой неисправных запоминающих элементов | 1975 |

|

SU556502A1 |

| Оперативное запоминающее устройство | 1975 |

|

SU653624A1 |

| Запоминающее устройство с блокировкой неисправных ячеек | 1974 |

|

SU492000A1 |

| Запоминающее устройство с самоконтролем | 1989 |

|

SU1718276A1 |

| Запоминающее устройство с самоконтролем | 1986 |

|

SU1424060A1 |

| Запоминающее устройство с контролем и коррекцией ошибок | 1983 |

|

SU1117715A1 |

ч/

/

/ V

/

Авторы

Даты

1976-09-05—Публикация

1972-10-30—Подача