1

Изобретение относится к запоминающим устройствам.

известно запоминающее устройство, содержащее регистр слова и счетчик, подключенные к блоку кодирования, соединенному с иервым входом накопителя, и блоку декодирования, вход которого через буферный ре1-истр подключен к первому выходу накопителя, и дополнительный блок кодирования - декодирования, входы которого соединены с выходом счетчика и вторым выходом накопителя, а вььходы - с вторым входом накопителя и входом счетчика. В указанном запоминающем устройстве при отказах элементов памяти ошибки корректируются блоком декодирования, управляемым счетчиком. Информация каждой ячейки кодируется в зависимости от максимального числа отказов и случайных сбоев в данной ячейке 1.

Недостатком этого запоминаюпдего устройства является влияние на величину мощности корректирующего кода случайных сбоев, что ведет к нерациональному использованию технического ресурса оборудования и снижает надежность устройства.

Цель изобретения - повышение надежности устройства.

Это достигается тем, что запоминающее устройство содержит блок регистров, второй счетчик, два блока элементов И, элемент

2И--ИЛИ, два элемента И и элемент сравнения, первый вход которого соединен с выходо.м регистра адреса и входом первого блока элемептов т1, выходом подключенного к адресному входу блока регистров, адресный выход которого связан с вторым входом элемента сравнения. Выход элемента сравнения подсоединен к входам второго блока элементов И, элемента 2И-ИЛИ и двух элементов И, вторые входы которых соединены соответственно с вторым входом первого блока элементов И, первым и вторым выходом блока декодирования. Третий выход блока декодирования подключен к входу элемента 2И- ИЛИ и входу сброса второго счетчика, счетный вход которого связан с выходом второго элемента 1-1, вход установки - с выходом второго блока э.тементов И. Выход второго счетчика соединен с информационным входом блока регистров, иервыи вход сброса последнего - с выходом элемента 2И-ИЛИ, второй вход сброса - с выходом первого элемента И, а информационный вход - с другим входом второго блока элементов И.

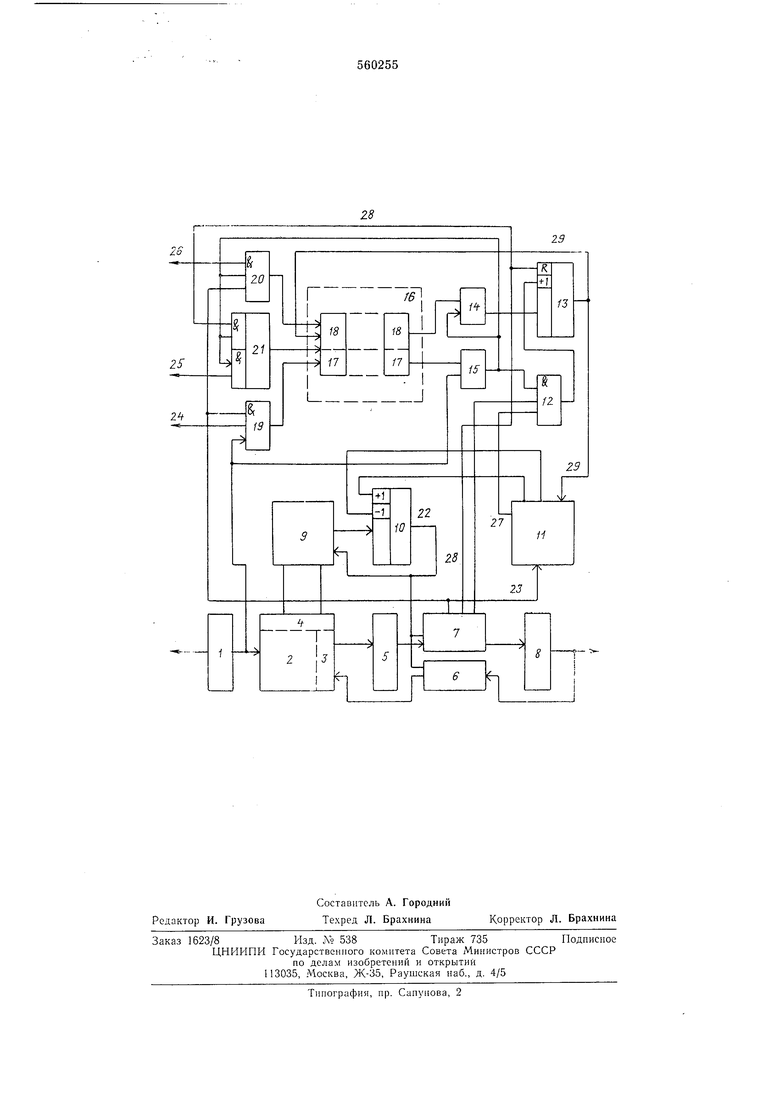

Иа чертеже представлена блок-схема запоминающего устройства.

Предлагаемое устройство содержит регистр 1 адреса, накопитель 2 с первыми 3 и вторыми 4 входами-выходами, буферный регистр 5, блоки кодирования 6 и декодирования 7, регистр 8 слова, дополнительный блок 9 кодирования - декодироваиия, счетчик 10, блок 11 местного управления, элемент И 12, счетчик 13, блок элементов И 14, элемент 15 сравнения, блок 16 регистров, состоящий из адресной 17 и информационной 18 частей, блок элементов И 19, элементы И 20 и 2PI- ИЛИ 21.

Выход регистра 1 адреса нодключеп к адресному входу накопителя 2 и к входам блока элементов И 19 и элемента 15 сравнения, первые вход и выход 3 накопителя - соответствено к блоку 6 кодирования и через буферный регистр 5 к блоку 7 декодирования. Вторые вход и выход 4 накопителя 2 соединены с дополнительным блоком 9 кодирования-декодирования, выход блока 9 - со счетчиком 10, счетные входы которого подключены к блоку И местного управления. Выход счетчика 10 шиной 22 связал с входами блоков 9, 6 и 7, выход блока 7-с входом регистра 8 слова, соединенного своим выходом с входом блока 6. Выход элемента 15 сравнения нодключел к входам блока элементов И 14, элемента 2H--liJili 21 и элементов PI 12 и 20. Второй вход элемента И 20 цепью 23 соединен с вторььм входом первого блока элементов Р1 19, входом блока 11 местного уиравленияи нервым выходом блока 7 декодирования, второй выход которого подключен к второму входу второго элемента И 12, блок элементов И 19, элемент 2И-ИЛИ 21 и элементы И 20 и 12 цепями 24-27 - с блоком И местного управления. Четвертый вход элемента 2И- IblPI 21 ценью 28 соединен с третьим выходом блока 7 декодирования и входом сброса второго счетчика 13, счетный вход которого подключен к выходу второго элемента И 12, а вход установки - к выходу второго блока элементов Pi 14. Второй вход блока элементов И 14 связан с информационным выходом блока 16 регистров, два входа сброса которого нодключены к выходам элементов И 20 и 2И-ИЛИ 21, адресиый вход блока 16 регистров - с выходом блока элементов Р1 19, информационный вход гииной 29-с блоком 11 местного управления и выходом счетчика 13. Адресный выход блода регистров соединен с вторым входом элемента 15 сравнения.

Запоминающее устройство работает следующим образом.

В унравляющей части (вторые вход и выход i накопителя 2) каждый i-й ячейки накопителя записано число пг+1 (т-число отказавших элементов памяти в данной ячейке), для хранения которого используется корректирующий код ностоянной мощности, достаточной для обеспечения требуемой достоверности хранения. В информационной части (первые вход и выход 3 накопителя) данной ячейки хранится полезная информация, для хранения ее используется корректирующий код, мощность которого равна /n-f 1.

Цикл обращения к запоминаюплему устройству состоит из тактов чтения и заниси.

В такте чтения код ячейки, адрес которой запнсан на регистре 1, поступает на первый 3 и второй 4 выходы накопителя 2, при этом информационная часть слова записывается на

буферной регистр 5, управляющая часть декодируется блоком 9 и проходит на счетчик 10. Блок 7 декодирования ио шине 22 настраивается на декодирование корректирующего кода, мощность которого равна числу, записанному на счетчике 10, т. е. числу т+1. Информационная часть слова с буферного региclpa 5 декодируется и корректируется блоком 7 и выдается ,иа регистр 8 слова.

При этом возможны три варианта работы

блока 7 декодирования:

а)исправлена m-pl ошибка (m-j-1-чиCv o, записаиное на счетчике) 10);

б)исправлено число ошибок меньше /п;

в)исправлено т ошибок.

Одновременно с выборкой информации из накопителя 2 на регистр 8 слова код адреса на регистре 1 сравнивается элементом 15 с содержимым адресной части 17 всех регистров блока 16.

В такте записи содержимое счетчика 10 и регистра 8 слова через блок 9 кодирования- декодирования и блок 6 кодирования поступает на второй 4 и nepBbiii 3 входы накопителя 2 и записывается Б выбранную ячейку.

Pacc.vioTpH.i все три варианта работы VCTpoiicTRa в такте чтения.

а). Бло1-;ом 7 декодирования исправлена т.--г1 ошибка. Пусть в блоке 16 регистров не оказалось данного адреса. На выходе элемента 15 сравнения - запрегцающий сигнал. На первом выходе (цепь 23) блока 7 декодирования появился сигнал о ма ;симальиом испо.гьзовании мощности корректирующего кода, по которому блок 11 местного управления

выдает сигнал+1 в счетчике 10, а по цепи 24-разреБ1ение па запись через блок элемеитоа И 19 содержимого регистра 1 адреса в адресную чаеть 17 одного из свободных регистров блока 16.

б). Блок декодирования исправил число ошибок меньше т. На втором выходе блока 7 декодирования разрешающий сигнал. Возможны два случая:

1)в блоке 16 регистров нет данного адреса, на выходе элемента 15 сравнения запрещающий сигнал и цикл обращения идет обычным образом;

2)в блоке регистров есть данный адрес, следовательно, в одном из предыдущих обраимений к ячейке было максимальное использование мощности корректирующего кода и в счетчик 10 прибавлена «1 (вариант а). В счетчике 10 записано число in+l .

Во BTOpo:vi случае одновременно с выборкой слова на регистр 8 содержимое информационной части блока 16 регистров по разрешающему сигналу на выходе элемента 15 сравнения через блок элементов И 14 записывается на счетчик 13. Затем к содержимому

счетчика 13 прибавляется «+ сигналом, поступающим по цепи 27 из блока 11 местного управления через элемент И 12, на двух других входах которого разрешающие сигналы с элемента сравнения и второго выхода блока 7 декодирования. Новое содержимое счетчика 13 по щине 29 записывается в информационную часть 18 соответствующего выбранному адресу регистра блока 16.

Если в процессе работы при обращении к данной ячейке произойдет определенное количество и описанных случаев (2), можно сделать вывод, что мощность m+l m + 2 примененного корректирующего кода не является оптимальной, т. е. завыщепа. По сигналу и из счетчика 13 блок местного управления после выборки информации на регистр 8 слова выдает сигнал «-1 на счетчик 10 и по цепи 25 через элемент 2И-ИЛИ 21 сигнал сброса соответствующего данному адресу регистра блока 16.

в). Блок 7 декодирования исправил т-1 ощибок. На третьем выходе (цепь 28) блока 7 декодирования разрещающий сигнал. Возможны два случая:

1)в блоке 16 регистров не оказалось данного адреса, цикл обращения к запоминающему устройству идет обычным образом;

2)в блоке регистров есть данный адрес, следовательно, при одном из предыдущих обращений к данной ячейке имело место максимальное использование мощности корректирующего кода и в счетчик 10 прибавлена «1. При этом увеличение мощности корректирующего кода данной ячейки вызвано отказом, а не случайным сбоем. Сигналом на третьем выходе блока 7 декодирования (цепь 28) устанавливаются Б «О счетчик 13 и через элемент 2Pi-ИЛИ 21 соответствующий данному адресу регистр блока 16.

Если же в блоке 16 регистров при варианте а) окажется данный адрес, то в счетчик 10 прибавляется «1, а информационная часть соответствующего данному адресу регистра блока 16 устанавливается в «О сигналом, поступающим из блока 11 местного управления по цепи 26 через элемент И 20.

В предлагаемом запоминающем устройстве при возникновении отказа или случайного сбоя в i-й ячейке мощность корректирующего кода для данной ячейки увеличивается на «1.

В дальнейщем, если при N обращениях к г-й ячейке отказ не повторился, т. е. число исправленных ощибок при каждом обращении на две и более единиц меньще числа, записанного в управляющей части слова, этот отказ расценивается как случайный сбой. Из содержимого управляющей части слова вычитается «1. Таким образом, в предлагаемом устройстве

устраняется влияние на величину мощности корректирующего кода случайных сбоев, что позволяет в режиме постоянной длины кодового слова более рационально использовать технический ресурс оборудования и увеличить

эффективную емкость устройства.

Формула изобретения

Запоминающее устройство по авт. св.

jYg 514342, отличающееся тем, что, с целью повыщения надежности устройства, оно содержит блок регистров, второй счетчик, два блока элементов И, элемент 2И-ИЛИ, два элемента И и элемент сравнения, первый

вход которого соединен с выходом регистра адреса и входом первого блока элементов И, выход которого соединен с адресным входом блока регистров, адресный выход которого соединен с вторым входом элемента сравнения, выход элемента сравнения соединен с входами второго блока элементов И, элемента 2И-ИЛИ и двух элементов И, вторые входы которых соединены соответственно с вторым входом первого блока элементов И,

первым и вторым выходами блока декодирования, трет:ий выход которого соединен с входом элемента 2И-ИЛИ и входом сброса второго счетчика, счетньп вход которого соединен с выходом второго элемента -И, вход установки - с выходом второго блока элементов И, выход второго счетчика соединен с информационным входом блока регистров, первый вход сброса которого соединен с выходом элемента 2И-I-IJill, второй вход сброса - с

выходом первого элемента И, а информационный вход - с другим входо.м второго блока элементов И.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР jV 514342, кл. G ПС 11/00, 29.01.75 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство | 1975 |

|

SU529481A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО„. -..,-•. ."р л С^аог^'-.---'^--:: '•^k^Vfi''-'- | 1973 |

|

SU375675A1 |

| Запоминающее устройство | 1988 |

|

SU1531175A1 |

| Запоминающее устройство с автономным контролем | 1982 |

|

SU1048520A1 |

| Запоминающее устройство с блокировкой неисправных запоминающих ячеек | 1974 |

|

SU507900A1 |

| Запоминающее устройство с исправлением ошибок | 1979 |

|

SU920845A1 |

| Запоминающее устройство с самоконтролем | 1981 |

|

SU964737A1 |

| Запоминающее устройство | 1972 |

|

SU470866A1 |

| Запоминающее устройство с коррекцией ошибок | 1986 |

|

SU1381605A1 |

| Запоминающее устройство с обнаружением и исправлением ошибок | 1980 |

|

SU898509A1 |

Авторы

Даты

1977-05-30—Публикация

1975-03-21—Подача