1

Изобретение отнсх;ится к вычислительной технике.

Известные - буферные регистры, содержащие Rg -триггеры, входы установки которых соединены с выходами Ьдноименных пероых элементов И-НЕ , первые входы которых подключены к разрядным шинам, и .второй многовходовой элемент И-НЕ , не-. достаточно надежны при приеме информации.

11елыо изобретения является повышение надежности работы буферного регистра.

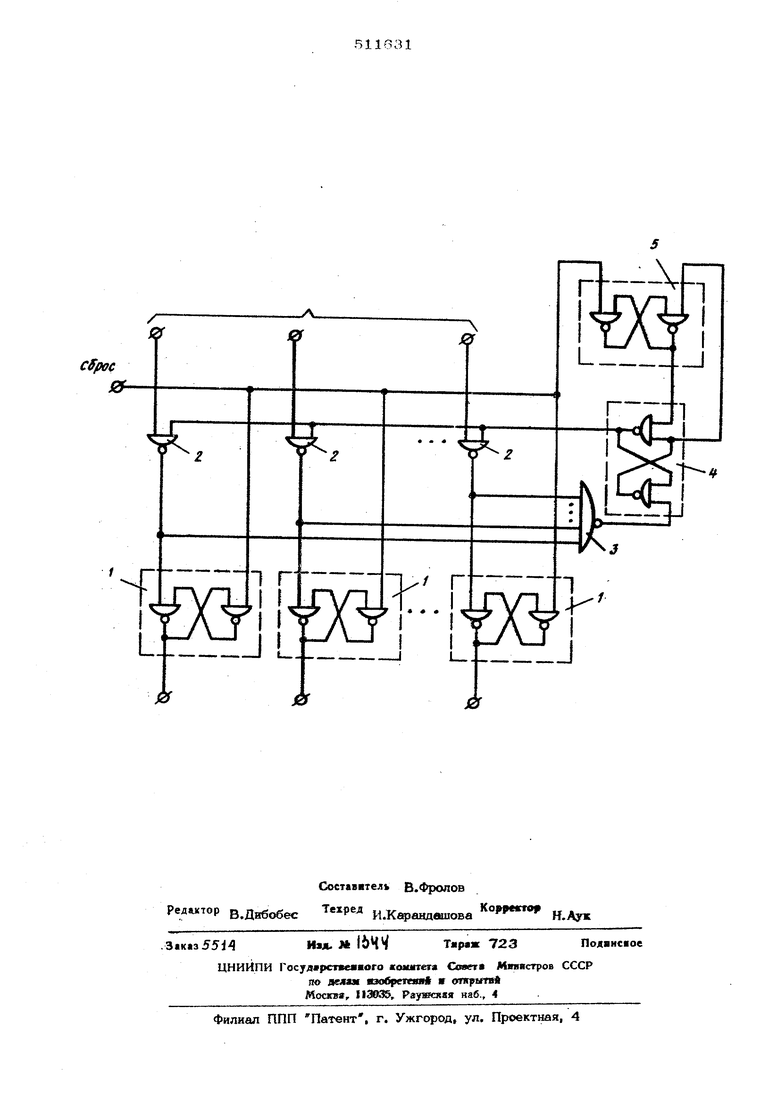

Поставленная цель достигается тем, что буферный регистр содержит триггеры блокировки и задержки, вход установки которого соединен с шиной, сброса, вход сброса и ин ве дксвыЙ выход подключены ;соответствен-. но к :;, инверснрь выходу и ко входу установки триггера блокировки, прямой выход которого соединен с шинсЛ блокировки, а Ьход сброса черва многовходовой элемент H-iHE связан с установочными входами Rg триггеров.

На чертеже дана схема буферного регистра, который содержит Rg - триггер 1, эпемент И-НЕ 2, многовходовсй элемент

И-НЕ 3, триггер 4 блокировки, триггер 5 задержки. Исходное состояние устройств триггеры задержки 5 и блокировки 4 нахо дятся в нулевом состоянии, иа общей швнв одноименных элементов И существует нулевой потенциал; таким образом, RS триггеры 1 буферного регистра заблокирЬ ваны. Работа начинается с подачи сигнала по шине сброса, при этом RS « триггеры 1 буфернсго регистр устанавливаются в нулевое состояние, а триггер 5 задержки в -единичное состояние.

Триггер 4 блокировки под воздействием нулевых сигналов на Установочном н сбросном входах установится в состояние, когда на его прямом и инверсном выходах будут единичные сигналы. Единичный сигнал с прямого выхода триггера 4 блокировки подготавливает одноименные элементы 2 для : прием а данных, то есть R8 триггеры 1 буферного регистра деблсжируюте я.

Прием информации буферным регистром в виде параллельного импульсного коде осуществляется через одноименные элемент ты 2. При этом импульсы отрицательной полярности с выхода одноименных элементов 2 устанавливают соответствующие RS -триггеры 1 буферного регистра в единичное состояние и одновременно по-ступают на входы многовходового логиче СКОРО элемента 3. Единичный сигнал на выходе много входового элемента 3 сформируется в момент появления первого информационного импульса и будет существовать до момен та окончания импульса, имеющего максимальную задержку в пинии связи. При этом на инверсном выходе триггера 4 блокиров ки установится нулевой потенциал, который передним фронтом переключит триггер 5 задержки в нулевое состояние. Триггер 4 блокировки останется . в единичном состоянии до окончания последнегр из пришедших информационных импульсов. По окончании приема информации 4а выходе многовходсжого элемента 3 сформи руется нулевой сигнал, передний фронт которого установит триггер 4 блокировки в нулевое состояние, то есть произойдет блокировка RS «триггеров 1 буферного регистра до прихода следующего импульса сброса. Таким образом, буферный регистр отли ется высокой надежностью приема информа ии, так как разброс времен переключения RS -триггеров не влияет -ш формирован: игнала блокировки, при этом асинхронное.., оявления информационных импульсов, опрееляемая различным времзнем задержек в епях связи, компенсируется схемой блокиовки. Формула изобретения Буферный регистр, содержаший RS триггеры, входы установки которых соединены с выходами одноименных первых элементов И-НЕ , первые входы которых подключены к разрядным шинам, и второй многовходовой элемент И-НЕ , отличающийся тем, что, с целью повы шения надежности работы буферного регист. ра, он содержит триггеры блокировки и задержки, вход установки которого соединен с шиной сброса, вход сброса и инвероный выход подключены соответственно к инверсному выходу и ко входу установки триггера блокировки, прямой выход которого соединен с шиной блокировка, а вхой сброса через многовходовой элемент ИНЕ связан с установочными входами RS -триггеров.

| название | год | авторы | номер документа |

|---|---|---|---|

| Буферное запоминающее устройство | 1980 |

|

SU881855A1 |

| Буферное запоминающее устройство | 1980 |

|

SU926711A1 |

| Счетное устройство с предварительной уставкой кода | 1982 |

|

SU1027832A1 |

| Устройство для сравнения двух чисел | 1986 |

|

SU1314335A1 |

| Делитель частоты с переменным коэффициентом деления | 1976 |

|

SU657619A1 |

| Измеритель временных интервалов | 1983 |

|

SU1155990A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ПЕРЕДАЧЕЙ ДАННЫХ В КАНАЛЕ МНОЖЕСТВЕННОГО ДОСТУПА | 2000 |

|

RU2179787C1 |

| Матричный распределитель | 1987 |

|

SU1580377A1 |

| Буферное запоминающее устройство | 1990 |

|

SU1714684A1 |

| УСТРОЙСТВО АНАЛИЗА ПЕРЕКРЫТИЙ КАНАЛОВ ПРИ РАЗМЕЩЕНИИ ПАРАЛЛЕЛЬНЫХ ПОДПРОГРАММ В МНОГОПРОЦЕССОРНЫХ СИСТЕМАХ | 2011 |

|

RU2460126C1 |

Авторы

Даты

1976-04-25—Публикация

1974-08-26—Подача