1

Изобретение относится к вычислитедьной -технике и прейназначено для использования в качестве буферных запоминающих устройств (БЗУ) систем обработки информации.

Известно БЗУ, обладающее свойствами самоблокировки по окончании ввода информации и содержащее статический регистр и логические элементы 1 .

Недостатком известного регистра является невысокое быстродействие.

Наиболее близким к предлагаемому по технической сущности является буферное запоминающее устройство, содержащее триггеры, входы установки единичного состояния которых соединены с выходами первых элементов И-НЕ, первые входы которых подключены к информационным шинам, а вторые входы объединены и подключены к шине блокировки, триггер блокировки и триггер задержки, вход установки единичного состояния которого подключен к шине

сброса, как и соответствующие входы RS-триггеров, вход установки нулевого состояния и инверсный выход подключены соответственно к инверсному выходу и ко входу установки единичного состояния триггера блокировки, прямой выход которого соединен с шиной блокировки, а вход установки нулевого состояния через многовходовой элемент И связи с выходами первых элементов И-НЕ 21.

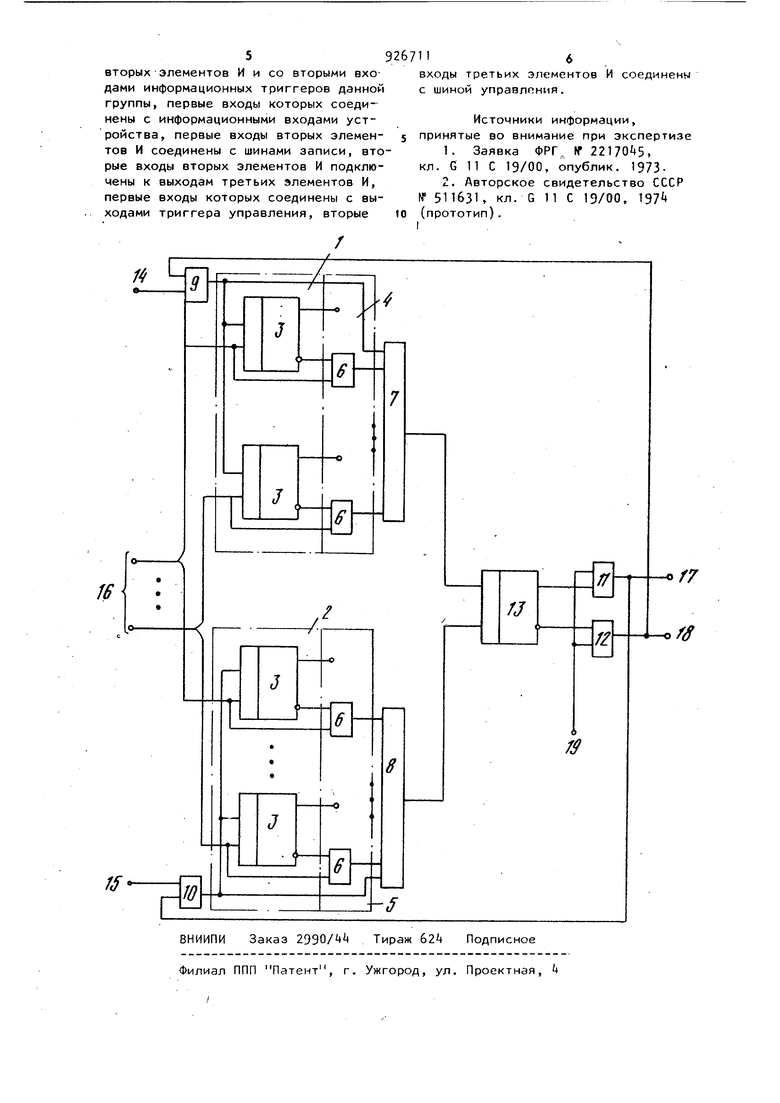

Недостатком описаннного буферного запоминающего устройства является ограниченное быстродействие, так как частота поступления информации определяется темпом поступления сигнала на шину сброса (деблокировки). Эта частота определяется из оговоренного в технических условиях максимального времени задержки переключения элементов, однако реальное время задержки может существенно отличаться от цифр указанных в технических условиях в меньшую сторону на интег 39 ралькые микросхемы серии К 155 или К Г/б. Поэтому быстродействие, вычис ленное для указанных микросхем,всегда оказывается ниже реального быстро действия, допустимого в конкретных условиях эксплуатации. 1|ель изобретения - повышение быст родействия буферного запоминающего устройства. Поставленная цель достигается тем что в буферное запоминающее устройство, содержащее группы информационных триггеров, первые элементы И, вы ходы которых соединены со входами триггера управления, вторые и третьи элементы И, шины записи и шину управ ления, введены группы элементов неравнозначности, входы каждого элемента неравнозначности данной группы соединены соответственно с выходом и первым входом каждого триггера дан ной группы, выходы элементов неравно значности соединены с одними входами соответствующего первого элемента И, другой вход каждого из которых соединен с выходами вторых элементов И и со вторыми входами информационных триггеров данной группы, первые входы которых соединены с информационны ми входами устройства, первые входы вторых элементов И соединены с шинами записи, вторые входы вторых элементов И подключены к выходам третьих элементов И, первые входы которых соединены с выходами триггера управления, вторые входы третьих, элементов И соединены с шиной управления. На чертеже изображена функциональ ная схема предлагаемого устройства. Устройство содержит группы 1 и 2 триггеров 3, группы и 5 элементов 6 неравнозначности, элементы И , триггер 13 управления, шины И и 15 записи, .входы 16 устройства, выходы 17 и 18 элементов И 11 и 12 и шину 19 управления. Буферное запоминающее устройство работает следующим образом. Сигнал управления записью поступа ет на шину 19. при этом единичный уровень напряжения формируется на од ном из выходов 17 и 18 элемента И 11 или 12, например на выходе элемента И 11 (если триггер находился,в единичном состоянии) . Этот- потенциал дает команду на поступление кодовой информации на информационные входы 16, на входы триггеров 3 обоих групп 1 и 2 и нл формирование команды запи I4 си на шине 15- Эта команда через открытый элемент И 9 или 10 поступает на синхровходы статических триггеров 3 и на многовходовой элемент И 7 или 8 соответствующей группы триггеров 3- На выходах элементов 6 неравнозначности данной группы единичные потенциалы формируются при равенстве информации на входах и выходах одноименных триггеров .3- Таким образом, на выходе элемента И 7 или 8 единичный уровень напряжения появляется только по окончании записи в данную группу триггеров 3 всего кодового слова. Этот единичный уровень напряжения изменяет состояние триггера 13 управления, блокирует через соответствующие элементы. И 9 или 10 и IIили 12 синхровходы триггеров 3 и формирует единичный потенциал разрешения записи по выходу 18 элемента и 12. Второе кодовое слово записыва- ется аналогично первому. : Предлагаемое буферное запоминающее устройство содержит два идентичных канала, имеющих общие информационные шины и единую систему управления записью, что позволяет не выделять специально .время для считывания информации, которое может производиться во время записи в соседний канал. Такая организация БЗУ позволя ет в максимальной степени использовать реальное физическое быстродействие логических элементов, определяющее быстродействие предлагаемого устройства. Формула изобретения Буферное запоминающее устройство, содержащее группы информационных триггеров, первые элементы И, выходы которых соединены с входами триггера упрайления, вторые и третьи элементы И, шины записи и шину управления, отличающееся тем, что, с целью повышения быстродействия устройства, в него введены группы элементов неравнозначности, входы каждого элемента неравнозначности данной группы соединены соответственно с выходом и первым входом каж-.. дого триггера данной группы, выходы элементов неравнозначности соединены с одними входами соответствующего первого элемента И, другой вход каждого из которых соединен с выходсчми

| название | год | авторы | номер документа |

|---|---|---|---|

| Буферное запоминающее устройство | 1980 |

|

SU881855A1 |

| Буферное запоминающее устройство | 1977 |

|

SU651412A1 |

| Буферное запоминающее устройство | 1981 |

|

SU1003145A1 |

| Буферное запоминающее устройство | 1978 |

|

SU942132A1 |

| Устройство для ввода информации | 1987 |

|

SU1432544A1 |

| Буферное запоминающее устройство | 1984 |

|

SU1226530A1 |

| Многоканальное устройство для ввода аналоговых данных и буферная память | 1984 |

|

SU1238054A1 |

| Устройство для приема последовательного кода | 1986 |

|

SU1390625A2 |

| Буферное запоминающее устройство | 1978 |

|

SU750568A1 |

| Устройство для сопряжения источника и приемника информации | 1984 |

|

SU1310827A1 |

Авторы

Даты

1982-05-07—Публикация

1980-06-25—Подача