(54) БУФЕРНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Буферное запоминающее устройство | 1980 |

|

SU926711A1 |

| Буферное запоминающее устройство | 1977 |

|

SU651412A1 |

| Буферное запоминающее устройство | 1984 |

|

SU1163357A1 |

| Буферное запоминающее устройство | 1978 |

|

SU942132A1 |

| Буферный регистр | 1974 |

|

SU511631A1 |

| Буферное запоминающее устройство | 1984 |

|

SU1226530A1 |

| Устройство для приема последовательного кода | 1986 |

|

SU1390625A2 |

| УСТРОЙСТВО ТЕСТОВОГО КОНТРОЛЯ | 2014 |

|

RU2565474C1 |

| Буферное запоминающее устройство | 1978 |

|

SU750568A1 |

| Электропривод с устройством обнаружения отказов | 1990 |

|

SU1781811A1 |

1

Изобретение относится к вычислительной технике и предназначено для использования в качестве входных буферных запоминающих устройств (БЗУ) систем обработки информации.

Известно БЗУ, обладающее свойствами самоблокировки по окончании ввода информации, содержащее статический регистр и логические элементы и имеющее простую структуру 1.

Однако данное устройство не может блокироваться при приеме нулевого кода и, следовательно, имеет низкую помехозащищенность.

Наиболее близким к предлагаемому по технической сущности является буферное запоминающее устройство, содержащее RS-триггеры, входы установки единичного состояния которых соединены с выходами первых элементов И-НЕ, первые входы которых подключены к информационным шинам, а вторые входы объединены и подключены к шине блокировки, триггер блокировки и задержки, вход установки единичного состояния которого подключен к шине сброса, как и соответствующие входы RS-триггеров, вход установки нулевого состояния и инверсный выход подключены соответственно к инверсному

выходу и ко Входу установки единичного состояния триггера блокировки, прямой выход которого соединен с шиной блокировки, а вход установки нулевого состояния через многовходовой логический элемент связан с выходами первых элементов И-НЕ 2.

Недостатками.этого БЗУ являются сложная схема формирования сигнала

10 блокировки, низкая помехозащищенность за счёт отсутствия самоблокировки при записи нулевого кода, необходимость каждый раз стирать информацию при снятии блокировки.

15

Цель изобретения - повышение помехозсшщщенности устройства и его упрощение.

Поставленная цель достигается тем, что в буферное запоминающее устройст20во, содержащее элементы памяти, например RS-триггеры, R-входы которых соединены с выходами элементов И-НЕ первой группы, триггер блокировки, первый вход которого соединен с выходом элемента И, входы первой группы которого подключены к выходам элементов И-НЕ первой группы, информационные шины, соединенные с первыми входами элементов И-НЕ первой

30 группы, выходы RS-триггеров подключень к выходам устройства, другие входы элементов И-НЕ первой группы соединены с шиной стробирования, элемент И-НЕ и шину сброса, введены элементы И-НЕ второй группы, первые входы которых соединены с информационными шинами, вторые входы элементов И-НЕ второй группы соединены с шиной стробирования, третьи входы элементов И-НЕ первой и второй групп соединены с выходом элемента И-НЕ, входы которого подключены соответственно к выходу триггера блокировки и выходу элемента И, входы второй группы которого соединены с выходами элементов И-НЕ второй группы, второй вход триггера блокировки подключен к шине сброса.

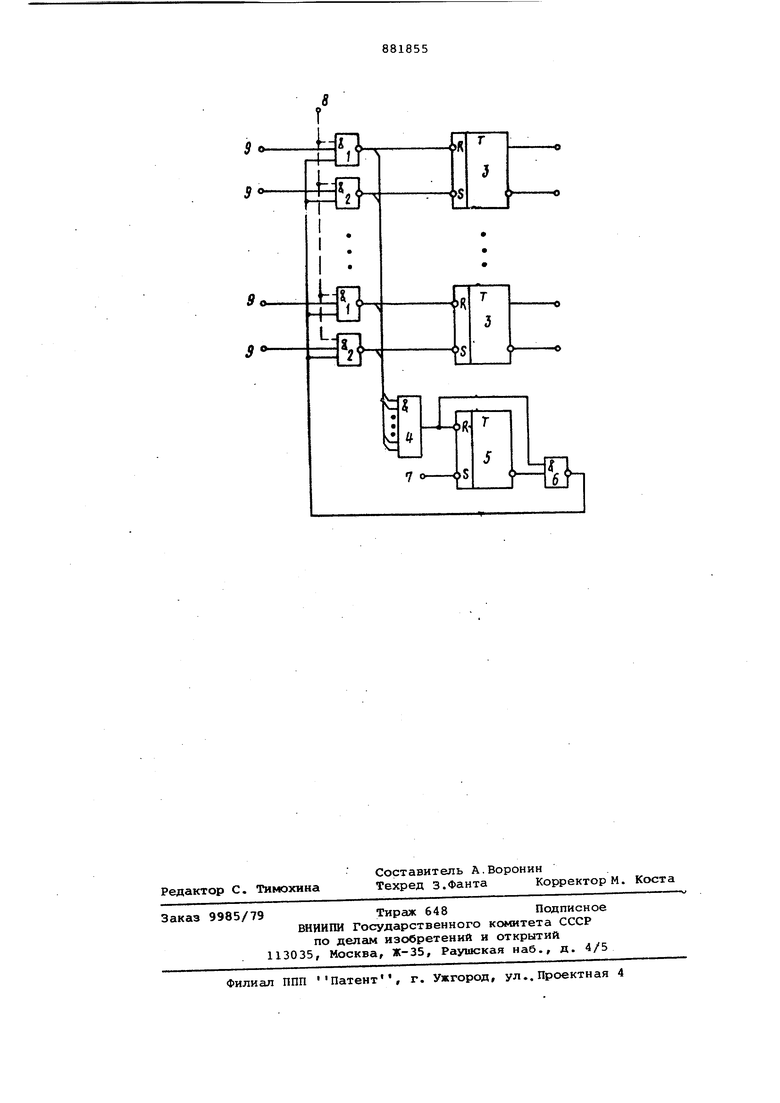

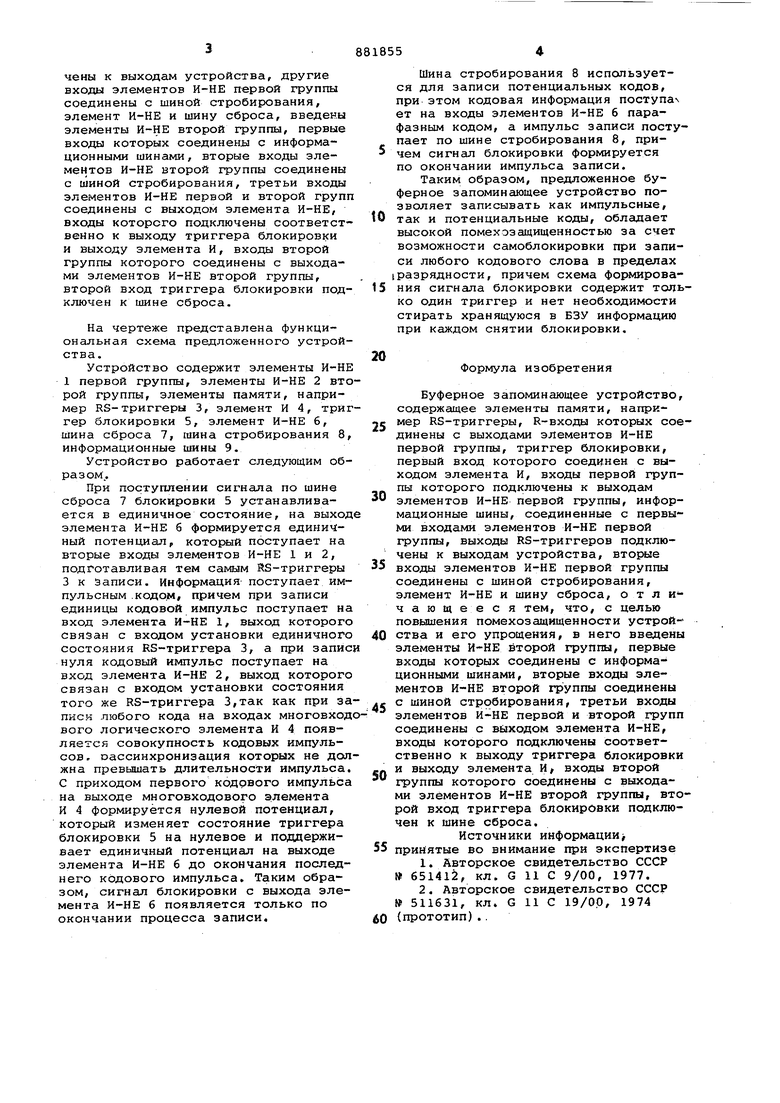

На чертеже представлена функциональная схема предложенного устройства.

Устройство содержит элементы И-НЕ 1 первой группы, элементы И-НЕ 2 второй группы, элементы памяти, например RS-триггеры 3, элемент И 4, триггер блокировки 5, элемент И-НЕ 6, шина сброса 7, шина стробирования 8, информационные шины 9.

Устройство работает следующим образом..

При поступлении сигнала по шине сброса 7 блокировки 5 устанавливается в единичное состояние, на выход элемента И-НЕ б формируется единичный потенциал, который поступает на вторые входы элементов И-НЕ 1 и 2, подготавливая тем самым RS-триггеры 3 к Записи. Информсщия поступает импульсным .кодом, причем при записи единицы кодовой импульс поступает на вход элемента И-НЕ 1, выход которого связан с входом установки единичного состояния RS-триггера 3, а при запис нуля кодовый импульс поступает на вход элемента И-НЕ 2, выход которого свяэан с входом установки состояния того же RS-триггера 3,так как при за писи любого кода на входах многовходвого логического элемента И 4 появляется совокупность кодовых импульсов , оассинхрониэация которых не должна превышать длительности импульса. С приходом первого кодового импульса на выходе многовходового элемента И 4 формируется нулевой потенциал, который изменяет состояние триггера блокировки 5 на нулевое и поддерживает единичный потенциал на выходе элемента И-НЕ 6 до окончания последнего кодового импульса. Таким образом, сигнал блокировки с выхода элемента И-НЕ 6 появляется только по окончании процесса записи.

Шина стробирования 8 используется для записи потенциальных кодов, при этом кодовая информация поступа ет на входы элементов И-НЕ 6 парафаэным кодом, а импульс записи поступает по шине стробирования 8, причем сигнал блокировки формируется по окончании импульса записи.

Таким образом, предложенное буферное запомингиощее устройство позволяет записывать как импульсные, так и потенциальные коды, обладает высокой помехозащищенностью за счет возможности самоблокировки при записи любого кодового слова в пределах разрядности, причем схема формирования сигнала блокировки содержит только один триггер и нет необходимости стирать хранящуюся в БЗУ информацию при каждом снятии блокировки.

Формула изобретения

Буферное запоминающее устройство содержащее элементы памяти, например RS-триггеры, R-входаа которых соединены с выходами элементов И-НЕ первой группы, триггер блокировки, первый вход которого соединен с выходом элемента И, входы первой группы которого подключены к выходам элементов И-НЕ первой группы, информационные шины, соединенные с первыми входами элементов И-НЕ первой группы, выходы RS-триггеров подключены к выходам устройства, вторые входы элементов И-НЕ первой группы соединены с шиной стробирования, элемент И-НЕ и шину сброса, отличающееся тем, что, с целью повышения помехозащищенности устройства и его упрощения, в него введены элементы И-НЕ второй группы, первые входы которых соединены с информационными шинами, вторые входы элементов И-НЕ второй группы соединены с шиной стробирования, третьи входы элементов И-НЕ первой и второй групп соединены с выходом элемента И-НЕ, входы которого подключены соответственно к выходу триггера блокировки и выходу элемента И/ входы второй группы которого соединены с выходами элементов И-НЕ второй группы, второй вход триггера блокировки подключен к шине сброса.

Источники информацииj принятые во внимание при экспертизе

Авторы

Даты

1981-11-15—Публикация

1980-01-21—Подача