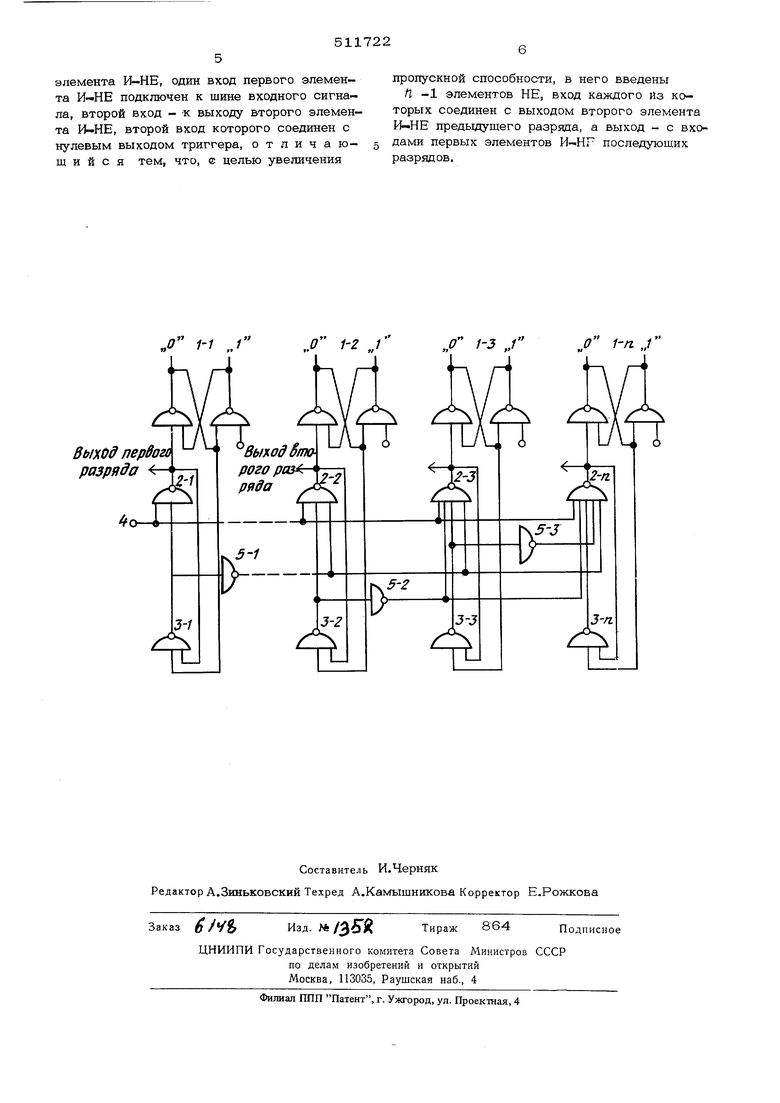

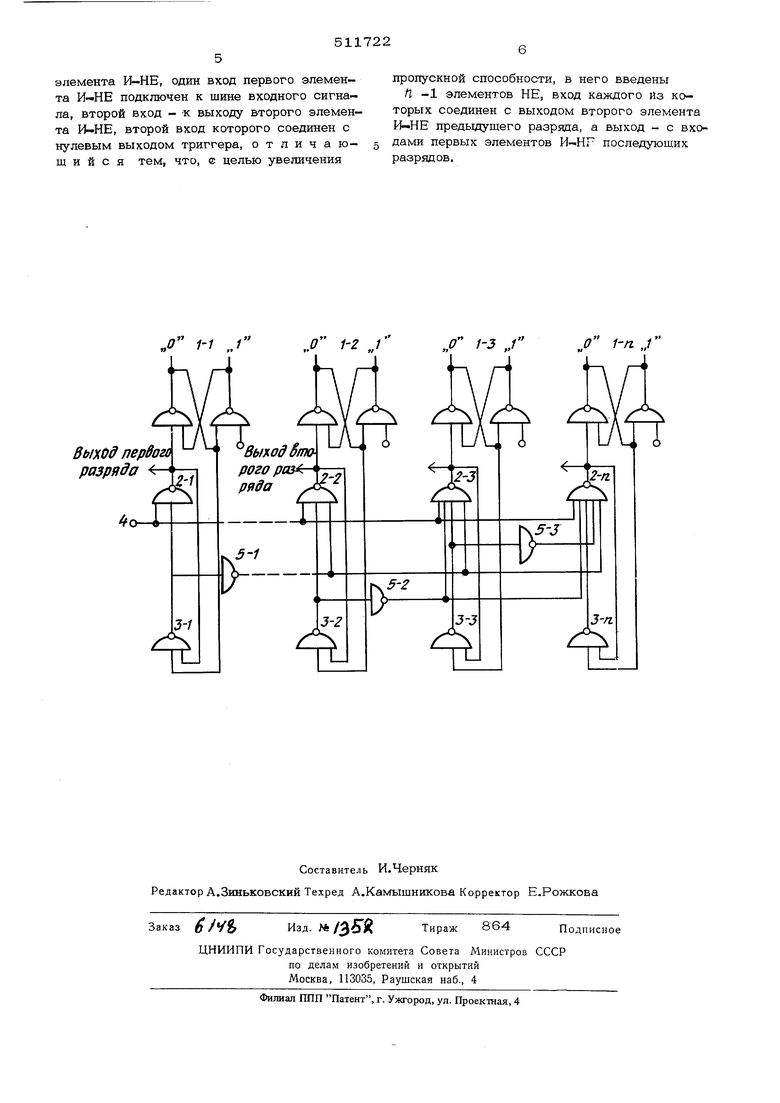

Изобретение относится к цифровой технике и может быть использовано в качестве формирователя опрашивающих сигналов в многоканальных системах, предназначенных для обработки информации. Известен распределитель импульсов, каж дый из п разрядов которого содержит триггер с раздельными входами и управля ющий блок на двух элементах И-НЕ, причем выход первого элемента И-НЕ соединен с нулевым входом триггера и первым входом второго элемента И-НЕ, один вход первого элемента И-НЕ подключен к щине входного сигнала, второй вход к выходу второго элемента И-НЕ, второй вход которого соеди нен с нулевым выходом триггера. Однако постоянство цикла формирования совокупности сигналов в П каналах известного распределителя не позволяет умень щать время формирования в случае, когда полезная информация находится только в П каналах из П ( т ft ) и нет необходимости опращивать все каналов расп делителя, что ограничивает пропускную способность распределителя импульсов. Целью изобретения является увеличение пропускной способности распределителя. Для этого в него введеныЯ -1 элементов каждого из которых соединен с выходом второго элемента предыдущего разряда, а выход - с входами первых элементов И-НЕ последующих разрядов. На чертеже приведена структурная электрическая схема распределителя импульсов. Распределитель импульсов состоит из П разрядов, каждый из которых содержит триггер 1-1 - 1 Л с раздельными входами и управляющий блок, собранный на двух элементах 2-1 - 2-П и 3-1 -З-П, причем выход первого элемента И-НЕ 2 соединен с нулевым входом триггера 1 и первым входом второго элемента И-НЕ 3, один вУод первого элемента И-НЕ 2 подклн чен к щине 4 входного сигнала, второй вход - к выходу второго элемента И-НЕ 3. второй вход которого соединен с нулевым выходом триггера 1. Вход каждого элемента НЕ 5 (всегоП -1 элементов) соединен с выходом второго элемента И-НЕ 3

предыдущего разр$ща, а выход - с входами первых элементов И-НЕ 2 последующих разрядов.

Распределитель импульсов работает следющим образом.

В начальный момент времени триггеры 1 всех разрядов устанавливаются в положение 1, Вследствие этого на выходе вторых элементов И-НЕ 3 формируется логическая единица, а на выходе элемента НЕ 5-1 логический нуль. Это, в свою очередь, веде к тому, что на выходах первого элемента - 2- tt назависимо от присутствия тактового импульса ( Т ) - логическая единица,

Поскольку в начальный момент времени входной сигнал (Т ), подаваемый на шину 4, отсутствует, т. е. равен нулю, на выходе первых элементов И-НЕ 2 будет действовать логическая единица.

С приходом входного сигнала ( Т ) на выходе первого элемента И-НЕ появляется логический нуль, который устанавливает триггер 1-1 в нулевое положение и который может быть направлен по одной из П выходных щин (Выход первого разряда На выходах элементов И-НЕ 2-2 - 2-ft логический нуль не появится, так как его появлению препятствует логический нуль на выходе элементов НЕ 5-1.

По окончанию действия входного импульса ( Т ) на выходах первых элементов И-НЕ 2-1 - 2- rt, снова появляется логическая единица.

С поступлением следующего входного импульса (Т ) на выходе первого элемента И-НЕ 2-2 появится логический нуль, который устанавливает триггер 1-2 в положение нуль и который может быть напревлен по следующей из выходных шин (Выход второго разряда). Появлению логического нуля на выходе первого элемента И-НЕ препятствует логический нуль на выходе второго элемента И-НЕ 3-1.

Появлению логического нуля на выходах первых элементов И-НЕ 2-3 - 2- - логический нуль на выходе элемента НЕ 5-2. Аналогично выходной сигнал будет формироваться на выходах первых элементов И-НЕ 2-3 - 2- П .

Основное назначение устройства - использование его для обнаружения признака присутствия полезной информации, указывающего в каких каналах необходимо формиро™ вать опрашивающие импульсы (управляющие импульсы). Для этой цели исходное состояние триггеров 1-1 - 1- задается в соответствии с заданным признаком.

Если, например, нужно сформировать импульсы по первому и третьему разрядам, то в начальный момент времени устанавливаются в положение единица триггеры 1-1 и 1-3. Триггеры 1-2 и 1- /t находятся в состоянии нуль. Поскольку в начальный момент времени входной сигнал ( Т ), подаваемый на шину 4, отсутствует, т. е. равен нулю, на выходе всех первых элементов И-НЕ 2 действует логическая единица.

С поступлением входного сигнала ( Т на выходе первого элемента И-НЕ 2-1 формируется сигнал (логический нуль), который установит триггер 1-.1 в положение нуль и который может быть направлен по выходной шине Выход первого разряда. Появление сигнала (логического нуля) на выходах первых элементов И-НЕ 2-2 - 2-ft будет препятствовать логический нуль на выходе элемента НЕ 5-1.

С поступлением следующего входного импульса ( Т ) логический нуль сформируется только на выходе первого элемента И-НЕ 2-3. Появление сигнала (логического нуля) на выходе первого элемента И-НЕ 2-1 будет препятствовать логический нуль на выходе второго элемента И-НЕ 3-1, появлению сигнала на выходе первого элемента И-НЕ 2-2 - логический нуль на выходе второго элемента И-НЕ 3-2, а появлению сигнала на выходе первого элемента И-НЕ 2- fi - логический нуль на выходе элемента НЕ 5-3.

Если все триггеры 1 находятся в состоянии нуля, то выходной сигнал не сформируется ни по одному из разрядов, так как на выходах вторых элементов И-НЕ 3-1 3- П будет логический нуль.

Таким образом, изменяя состояние триггеров 1, можно в любой последовательности осуществлять обработку исходной ин- формации, формируй опрашивающие (управляющие) импульсы в соответствующих каналах распределителя импульсов.

При этом в присутствии полезной информации только в tn каналах из

И ( fn П ) общее время формирование сигналов распределителем уменьшается

в Л т раз.

Формула изобретения

Распределитель импульсов, каждый из П разрядов которого содержит триггер с раздельными входами и управляющий блок на двух элементах И-НЕ, причем выход первого элемента И-НЕ соединен с нулевым входом триггера и первым входом второго

элемента И-НЕ, один вход первого элемента И-НЕ подключен к шине входного сигнала, второй вход - К выходу второго элемента И-НЕ, второй вход которого соединен с нулевым выходом триггера, отличающийся тем, что, е целью увеличения

пропускной способности, в него введены

П -1 элементов НЕ, вход каждого из которых соединен с выходом второго элемента И-НЕ предыдущего разр5ща, а выход - с входами первых элементов И-HF последующих разрядов.

| название | год | авторы | номер документа |

|---|---|---|---|

| РАСПРЕДЕЛИТЕЛЬ ИМПУЛЬСОВ | 1972 |

|

SU350179A1 |

| Распределитель импульсов | 1975 |

|

SU581594A2 |

| Распределитель импульсов | 1978 |

|

SU771873A1 |

| Распределитель | 1974 |

|

SU491221A1 |

| Буферное запоминающее устройство | 1977 |

|

SU651412A1 |

| Перестраивающий делитель частоты | 1977 |

|

SU661813A1 |

| Устройство для исследования сетей | 1977 |

|

SU717787A1 |

| Распределитель импульсов | 1982 |

|

SU1045407A2 |

| УСТРОЙСТВО для ЦИФРОВОГО РЕГУЛИРОВАНИЯ СКОРОСТИ | 1973 |

|

SU374580A1 |

| Цифровой фазовый дискриминатор | 1975 |

|

SU602881A1 |

-( Оя

рого раз ряда

«Г-.г-Л

-J-/

Авторы

Даты

1976-04-25—Публикация

1974-08-02—Подача