Изобретение относится к области вычислительной техники.

Известен распределитель импульсов, каждый разряд которого выполнен ща четырех потенциальных логических элементах «И-НЕ/ ИЛИ-НЕ, содержащий триггеры с раздельными входами и схему управления па двух элементах «И-НЕ, осуществляющую последовательную перепись единицы из одного триггера в другой под действием входного сигнала.

Недостатком известного устройства является ограниченность его функциональных возможностей и его недостаточно высокое быстродействие.

Целью изобретения является расщирение функциональных возмож1ностей распределителя и повышение его быстродействия. Это достигается тем, что выход каждого из логическйх элементов «И-НЕ/ИЛИ-НЕ, осуществляющих сдвиг единицы в триггерах, соединен с нулевым входом триггера данного разряда, с единичным входом смежного с ним триггера с той стороны, в которую необходимо осуществить сдвиг единицы, со входом следующего логического элемента «И-НЕ/ИЛИ-НЕ, организующего сдвиг единицы, и со входом логического элемента, другой вход которого соединен с нулевым плечом триггера данного

разряда, а выход - со входом данного логического элемента.

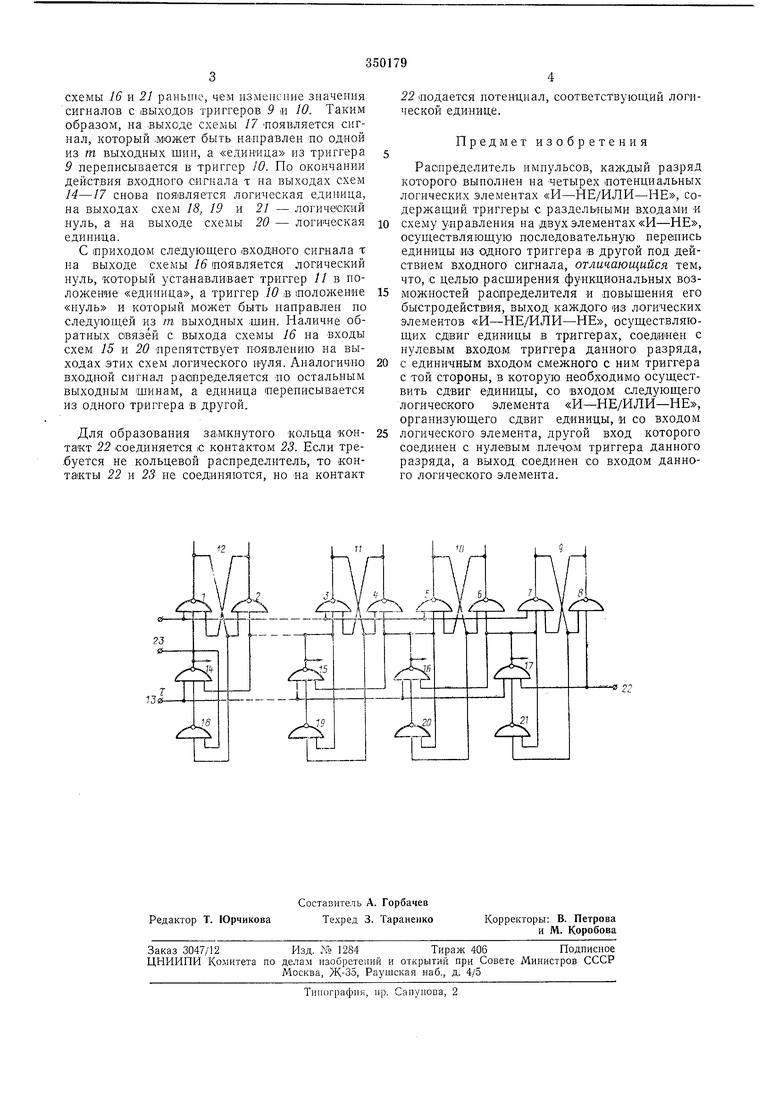

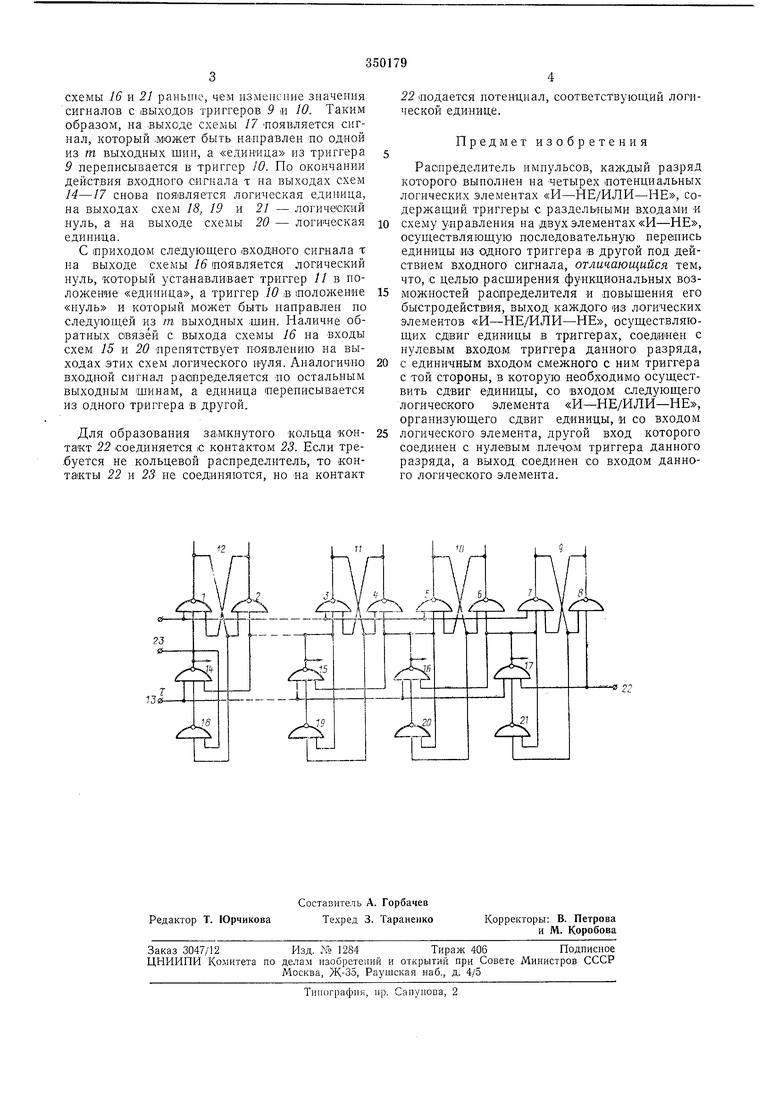

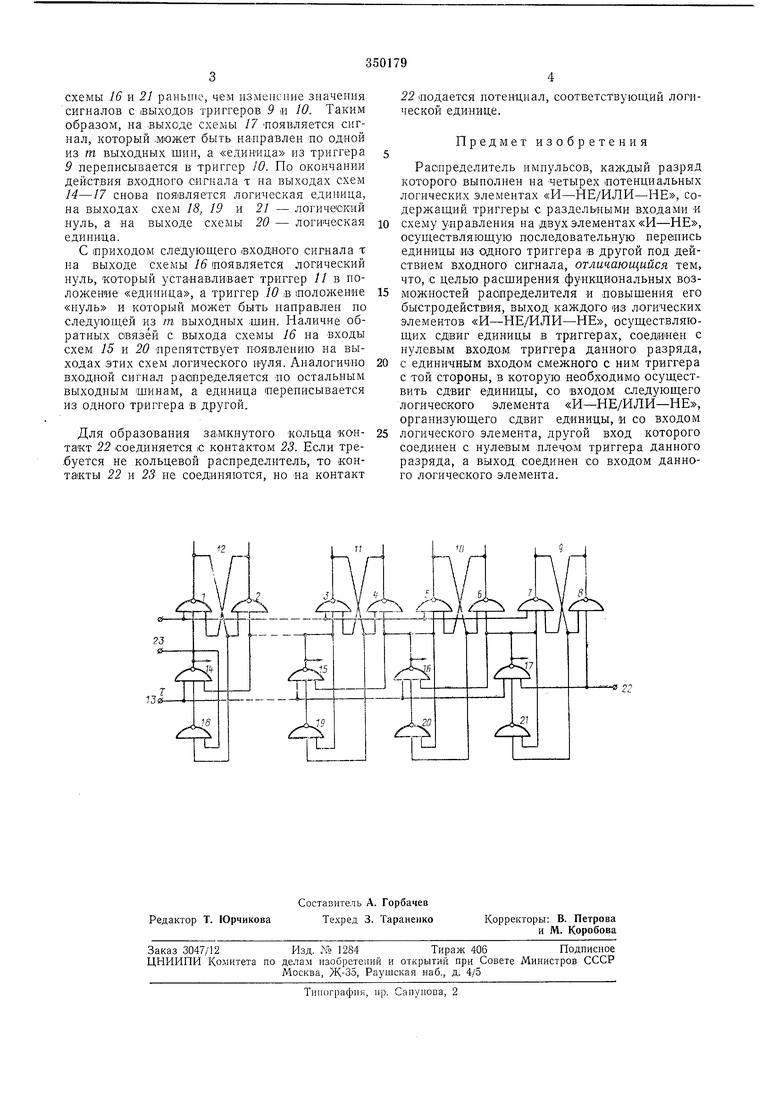

На чертеже для прнмера изображена схема предлагаемого распределителя импульсов на потенциальных элементах с числом разрядов, равным четырем. Число разрядов может быть леограничено (равно т).

Схемы /-8 «И-НЕ образуют элем&пты па:мяти триггеров 9-12. В начальный момент времени триггер 9 устана1влнвается в положение «единица. Остальные триггеры находятся в состоянии «нуль. В этом случае на выходе схем 1, 3 и 5 - логическая единица, на выходе схемы 7 - логический нуль. Носкольку в начальный момент -времени входной сигнал т, подаваемый на клемму 13, отсутствует, т. е. равен нулю, на выходе схем 14-17 «И-НЕ - логнческая единица. Вследствие этого на выходе схем 18, 19 п 20 «И-НЕ - логический нуль, а на выходе схемы 21 «И-НЕ - логическая единица.

С приходом входного сигнала т на выходе схемы 17 появляется логнческий нуль, который устана1вливает триггер 10 в положение «единица, а триггер 9 в положение «нуль. Поскольку выход схемы 17, кроме того, заведен на схемы 16 и 21, то на выходах схем 16 и 21 логический нуль не появляется, хотя триггеры 9 -и 10 изменяют свое состояние. Действительно, снгнал со схемы 17 иостунает на

схемы 16 и 21 раныпе, чем изменение значения сигналов с (ВЫХОДОВ триггеров 9 и 10. Таким образом, на выходе схемы 17 появляется сигнал, который .может быть направлен ло одной из т выходных шин, а «единица из триггера 9 переписывается в триггер 10. По окончании действия входного сигнала т на выходах схем 14-17 снова ноя1вляется логическая единица, на выходах схем 18, 19 и 21 - логический нуль, а на выходе схемы 20 - логическая единица.

С приходом следующего входного сигнала т на выходе схемы 16 появляется логический нуль, который устанавливает триггер 11 в положение «единица, а триггер 10 в положение «нуль и который может быть направлен по следующей из т выходных шин. Наличие обратных связей с выхода схемы 16 на входы схем 15 и 20 препятствует появлению на выходах этих схем логического н-уля. Аналогично входной сигнал раопределяется -по остальным выходным шинам, а единица юереписывается из одного триггера в другой.

Для образования замкнутого кольца контакт 22 соединяется ic контактом 23. Если требуется не кольцевой распределитель, то контакты 22 и 23 не соединяются, но па контакт

22 подается потенциал, соответствующий логической едипице.

Предмет изобретения

Распределитель импульсов, каждый разряд которого выполнен на четырех потенциальных логических элементах «И-НЕ/ИЛИ-НЕ, содержащий триггеры с раздельными входами и схему управления на двух элементах «И-НЕ, осуществляющую последовательную перепись единицы из одного триггера IB другой под действием входного сигнала, отличающийся тем, что, с целью расширения функциональных возможпостей распределителя и повышения его быстродействия, выход каждого из логических элементов «И-НЕ/ИЛИ-НЕ, осуществляющих сдвиг единицы в триггерах, соединен с нулевым ВХОДО.М триггера данного разряда, с единичным входом смежного с ним триггера с той стороны, в которую необходимо осуществить сдвиг единицы, со входом следующего логического элемента «И-НЕ/ИЛИ-НЕ, организующего сдвиг единицы, и со входом логического элемента, другой вход которого соединен с нулевым ллечо.м триггера данного разряда, а выход соединен со входом данного логического элемента.

| название | год | авторы | номер документа |

|---|---|---|---|

| Распределитель импульсов | 1974 |

|

SU511722A1 |

| Распределитель | 1974 |

|

SU491221A1 |

| РАСПРЕДЕЛИТЕЛЬ ИМПУЛЬСОВ НА ПОТЕНЦИАЛЬНЫХ ЭЛЕД1ЕНТАХ | 1973 |

|

SU364109A1 |

| Следящий аналого-цифровой преобразователь | 1988 |

|

SU1580555A1 |

| Распределитель импульсов | 1972 |

|

SU451074A1 |

| ДЕСЯТИЧНЫЙ СЧЕТЧИК | 1973 |

|

SU395988A1 |

| Многопрограммный делитель частоты | 1980 |

|

SU924866A1 |

| Следящий аналого-цифровой преобразо-ВАТЕль | 1979 |

|

SU797064A1 |

| Следящий аналого-цифровой преобразо-ВАТЕль | 1979 |

|

SU805489A1 |

| Управляемый делитель частоты импульсов | 1977 |

|

SU736381A1 |

Даты

1972-01-01—Публикация