Изобретение относится к вычислительной технике и предназначено для использования в качестве входных буферных регистров систем обработки информации.

Известно буферное запоминающее устройство БЗУ, содержащее разрядный статический регистр и логические элементы.

Такое БЗУ имеет простую структуру, но недостаточно надежно .

Из известных БЗУ наиболее близким по технической сущности к изобретению является устройство, содержащее статический регистр и логические элементы 2.

Это устройство отличается высокой надежностью работы, но содержит дополнительно два триггера и имеет сложную схему.

Целью изобретения является упрощение устройства при сохранении его высокой надежности.

Для достижения поставленной цели в БЗУ,содержащее статический регистр, один вход которого подключен к шине сброса,

другие входы статического регистра съедйнены с выходами элементов И и со входами элемента ИЛИ-НЕ. Первые входы элементов И соединены с информационными щинами, выходы статистического регистра подключены ко входам первого элемента И-НЕ, введен второй элемент И-НЕ, входы которого соединены с выходамиГ первого элемента И-НЕ, и элементы ИЛИ-НЕ, а выход - со вторыми входами элементов И.

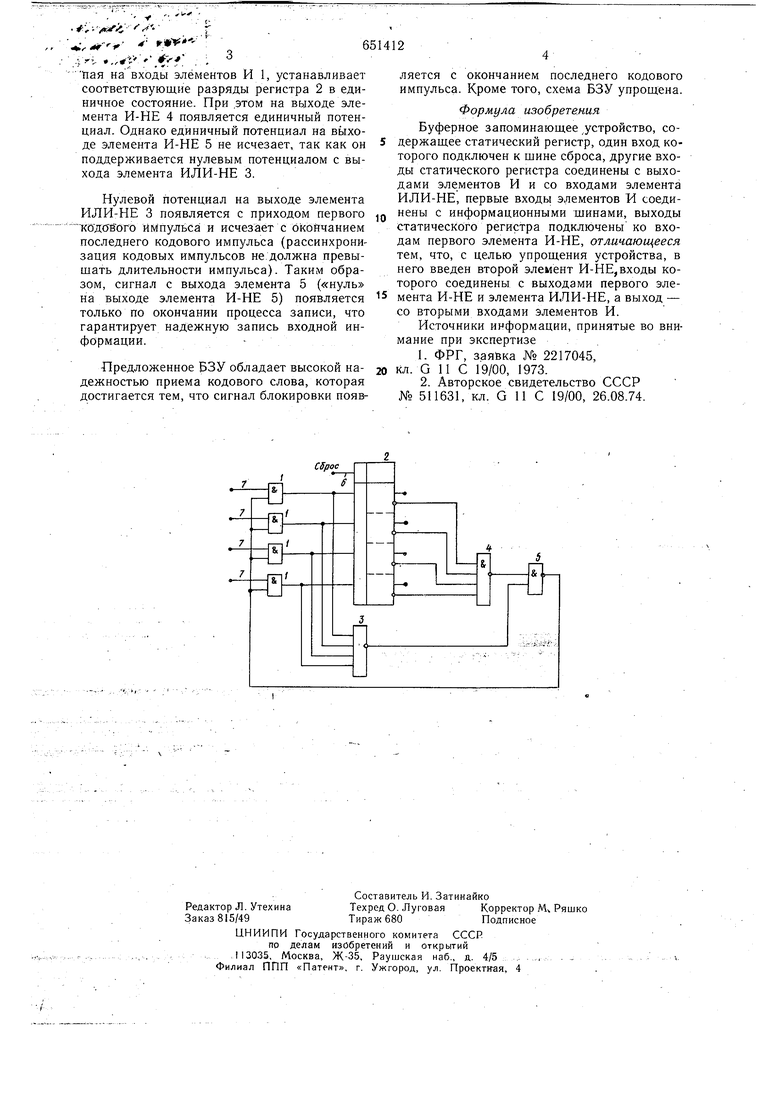

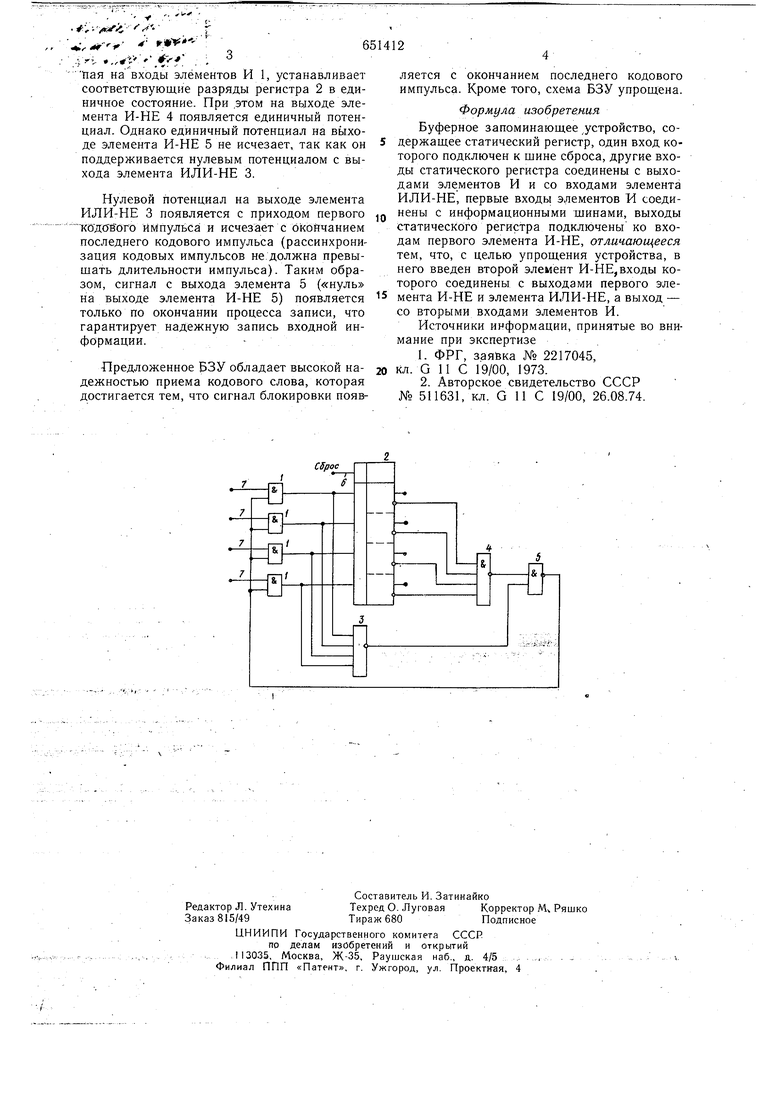

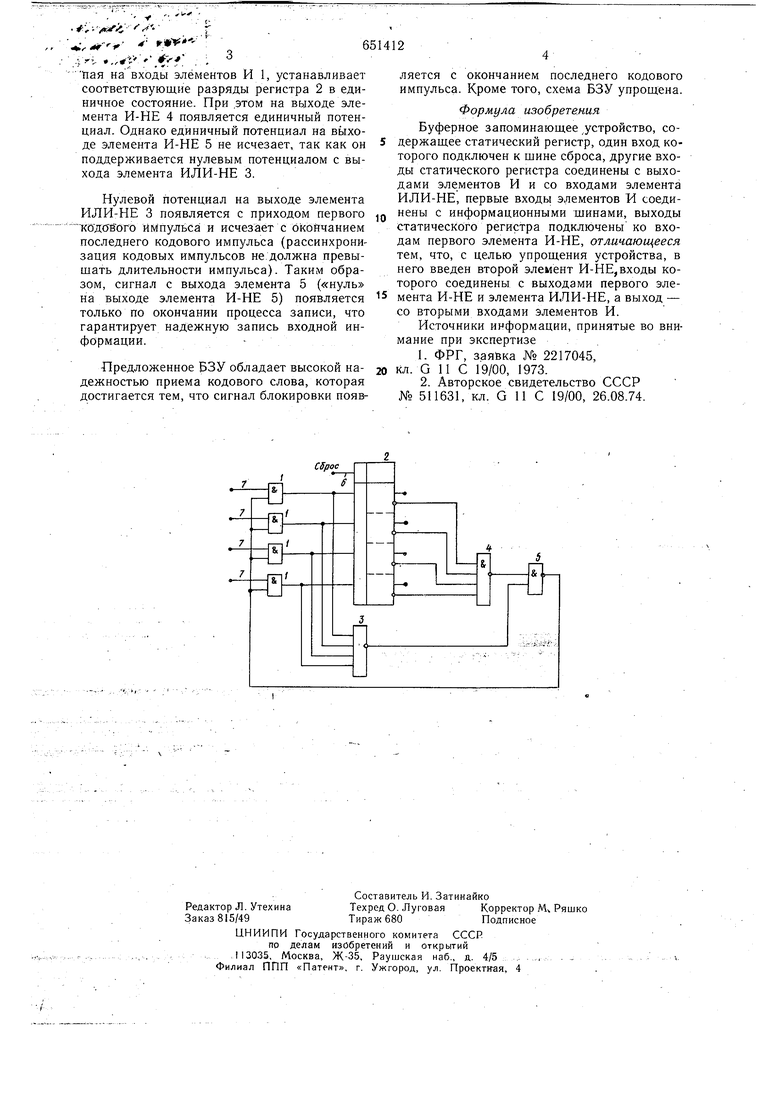

На чертеже представлена функциональная схема устройства.

Устройство содержит элементы И 1, статический регистр 2, элемент ИЛИ-НЕ 3, элементы И-НЕ 4, 5, шину сброса 6, информационные щины 7.

Работает устройство следующим образом.

При поступлении сигнала на щину сброса 6 все триггеры регистра 2 устанавливаются в нулевое состояние, и на выходе элемента И-НЕ 4 формируется нулевой потенциал, который определяет единичный потенциал на выходе элемента И-НЕ 5 (в это время на выходе элемента ИЛИ-НЕ 3 присутствует единичный потенциал, определяемый нулями на сигнальных шинах устройства). С выхода элемента 5 единичный потенциал открывает элементы И 1, подготавливая устройство к записи. Входной код в виде импульсов единичного уровня, посту.#;. vx-i- r 6514 ..jrt- ... . : 3 Пая на входы элементов И 1, устанавливает соответствующие разряды регистра 2 в единичное состояние. При .этом на выходе элемента И-НЕ 4 появляется единичный потенциал. Однако единичный потенциал на выходе элемента И-НЕ 5 не исчезает, так как он поддерживается нулевым потенциалом с выхода элемента ИЛИ-НЕ 3. Нулевой потенциал на выходе элемента ИЛИ-НЕ 3 появляется с приходом первого д кодового импульса и исчезает с окончанием последнего кодового импульса (рассинхронизация кодовых импульсов не должна превыщать длительности импульса). Таким образом, сигнал с выхода элемента 5 («нуль на выходе элемента И-НЕ 5) появляется только по окончании процесса записи, что гарантирует надежную запись входной информации.Предложенное БЗУ обладает высокой на- 20 дежностью приема кодового слова, которая достигается тем, что сигнал блокировки появ2ляется с окончанием последнего кодового импульса. Кроме того, схема БЗУ упрощена. Формула изобретения Буферное запоминающее устройство, содержащее статический регистр, один вход которого подключен к щине сброса, другие входы статического регистра соединены с выходами элементов И и со входами элемента ИЛИ-НЕ, первые входы элементов И соединены с информационными шинами, выходы статического регистра подключены ко входам первого элемента И-НЕ, отличающееся тем, что, с целью упрощения устройства, в него введен второй элемент И-НЕ,входы которого соединены с выходами первого элемента И-НЕ и элемента ИЛИ-НЕ, а выход-- со вторыми входами элементов И. Источники информации, принятые во внимание при экспертизе 1. ФРГ, заяька № 2217045, кл. G 11 С 19/00, 1973. 2. Авторское свидетельство СССР № 511631, кл. G 11 С 19/00, 26.08.74.

| название | год | авторы | номер документа |

|---|---|---|---|

| Буферное запоминающее устройство | 1980 |

|

SU881855A1 |

| Буферное запоминающее устройство | 1980 |

|

SU926711A1 |

| Перестраивающий делитель частоты | 1977 |

|

SU661813A1 |

| Буферное запоминающее устройство | 1984 |

|

SU1226530A1 |

| Буферное запоминающее устройство | 1978 |

|

SU942132A1 |

| Буферное запоминающее устройство | 1978 |

|

SU750568A1 |

| Делитель частоты с переменным коэффициентом деления | 1976 |

|

SU657619A1 |

| Буферный регистр | 1974 |

|

SU511631A1 |

| Буферное запоминающее устройство | 1980 |

|

SU920834A1 |

| Буферное запоминающее устройство | 1981 |

|

SU1003145A1 |

Авторы

Даты

1979-03-05—Публикация

1977-09-09—Подача