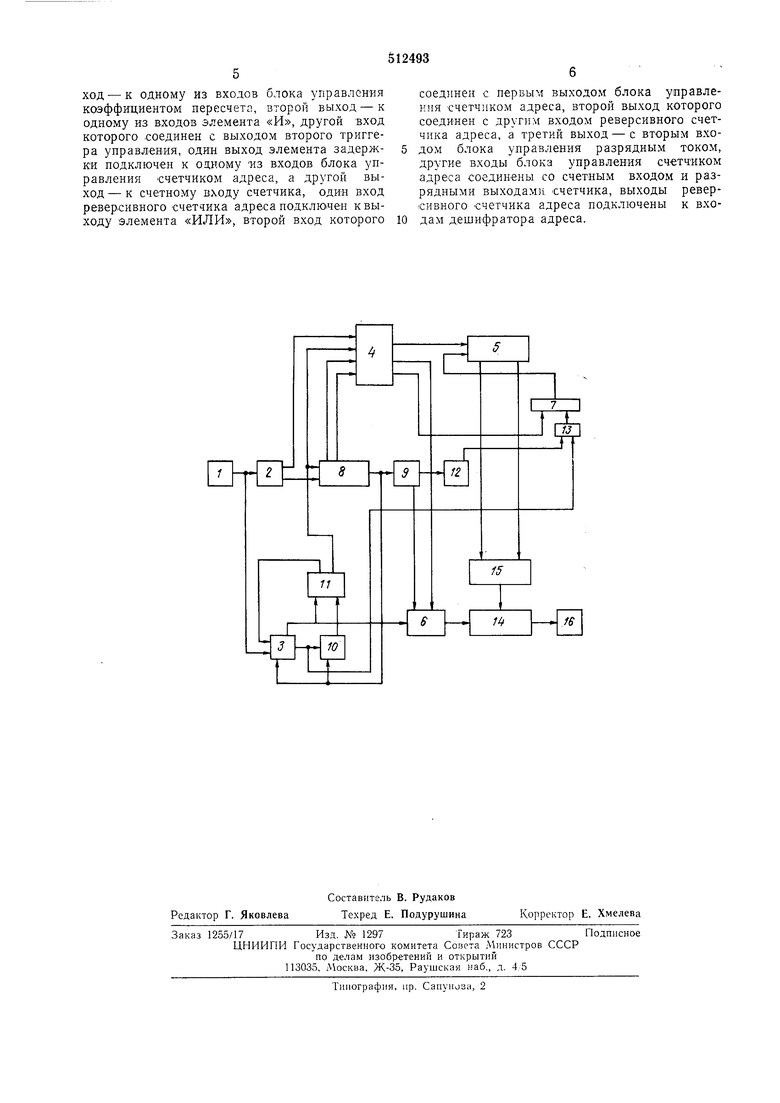

блок управЛбния счетчиком адреса 4, реверсивный счетчик адреса 5, блок управления разрядным током 6, элемент «ИЛИ 7, счетчик 8, триггер контроля 9, пересчетный триггер 10, блок управления коэффициентом пересчета 11, второй триггер управления 12, элемент «И 13. Проверяемая матрнца 14 подключена к выходу дешифратора адреса 15 и к входу блока контроля 16.

Вход элемента задержки 2 соединен с выходом генератора 1 и счетным входом триггера 3, вход которого нодключен к входу триггера 9 и выходу счетчика 8, первый выход - к одному из входОВ блока 11, второй выход - к одному из входов элемента «И 13, другой вход которого соединен с выходом триггера 12. Один выход элемента задержки 2 подключен к одному из входов блока 4, а другой выход - к счетному входу счетчика 8. Один вход счетчика 5 подключен к выходу элемента «ИЛИ 7, второй иход которого соединен с первым выходом блока 4, второй выход которого соединен с другим входом счетчика 5, а третий выход - -с вторым входом блока 6, другие входы блока 4 .соединены со счетным входом и разрядными выходами счетчика 8, выходы счетчика 5 подключены к входам дешифратора адреса 15.

Устройство работает следующим образом. В исходном положении все триггеры находятся в нулевом состоянии, и с выхода второго триггера управления 12 на вход элемента «И 13 подается запирающий потенциал. Зацирающий потенциал подается также па входы счетчика 8 и блока управления счетчиком адреса 4, а на вход первого триггера управления 3 подается отпирающий потенциал.

Во время первого такта первый триггер управления 3 устанавливается в единичное состояние, и производится считывание по нулевому адресу. Во время второго такта первый триггер управления 3 устанавливается в нулевое состояние, а пересчетный триггер 10 - в единичное состояние, и производится занись «О по нулевому адресу Первый импульс третьего такта устанавливает первый триггер управления 3 в единичное состояние. При этом на входы счгччика 8 и блока управления счетчиком адреса 4 подается отпираюш,ий потеициал, а на вход первого триггера управления 3 -запирающий потенциал. Этот же импульс через элемент задержки 2 подается на вход блока управления счетчиком адреса 4. В результате вычитается одна единица из содерл.имого счетчика адреса 5. Дальще производится запись «.1, и прибавляется одна единица в счетчик 8. Каждый импульс третьего такта прибавляет одну единицу в счетчик 8. Второй импульс третьего такта прибавляет одну единицу з счетчик 5, выбирается нулевой адрес, и производится считывание. Третий импульс третьего такта прибавляет еще одну единицу в счетчик 5, выбирается первый адрес, и производится запись «Ь. Четвертный импульс третьего такта вычитает одну единицу из содержимого счетчика 5, выбирается нулевой адрес - производится считывание.

Таким образом, в течение третьего такта производится многократное чередование разрушающих сигналов, до заполнения счетчика 8. Последний импульс третьего такта устанавливает счетчик 8, а также пересчетный триггер 10 и первый триггер управления 3 в нулевое состояние, а триггер контроля 9 - в единичное состояние, гем самым меняется полярность разрядного тока записи.

Во время четвертого такта производится считывание информации «О -по нулевому адресу и контроль считанной информации.

Если информация считана правильно, то в течение пятого, шестого и седьмого тактов производится npOJiCpKa разряда на хранение информации «1. В конце шестого такта второй триггер управления 12 устанавливается в единичное состояние, и на вход элемента «И 13 нодается отпирающий потенциал.

Во время восьмого такта импульс с выхода первого триггера управления 3 прибавляет единицу в счетчик 5, выбирается первый адрес, и производится его .проверка. В конце восьмого такта второй триггер управления 12 снова устанавливается в нулевое состояние, и запирается вход элемента «И 13.

Аналогичным образом производится последовательная проверка всех адресов проверяемого разряда. Переход от одного проверяемого разряда к другому осуществляется автоматически.

Для точного определения характера неисправности устройство можно вернуть к проверке по адресу, на котором обнаружена ошибка. В предложенном устройстве возможна проверка отдельных частей матрицы в заранее заданном диапазоне адресов и разрядов.

Формула изобретения

Устройство для ко}1троля запоминающих матриц на магнит1яых пленках, содержащее генератор, счетчик, вход которого соединен

с одним выходом блока управления коэффициентом пересчета, а выход-с входом пересчетного триггера, два триггера управления, триггер контроля, выход которого подключен к первому входу блока управления разрядным током, дешифратор адреса, элемент «ИЛИ, первый вход которого соединен с выходом элемента «PI, отличающееся тем, что, с целью повышения надежности работы устройства и точности контроля, оно содержит реверсивный счетчик адреса, блок управления счетчиком адреса и элемент задержки, вход которого соединен с выходом генератора и со счетным входом первого триггера управления, вход которого подключен к входу триггера контроля и выходу счетчика, первый выход--к одному из входов блока управления коэффициентом пересчета, второй выход-к одному из входов элемента «И, другой вход которого -соединен с выходом второго триггера управления, один выход элемента задержки подключен к одному из входов блока управления Счетчиком адреса, а другой выход - к счетному входу счетчика, один вход реверсивного счетчика адреса подклю чен к выходу элемента «ИЛИ, второй вход которого

соединен с первым выходом блока управления счетчиком адреса, второй выход которого соединен с другим входом реверсивного счетчика адреса, а третий выход - с вторым входом блока улравления разрядным током, другие входы блока управления счетчиком адреса соединены со счетным входом и разрядными выходам) счетчика, выходы реверсивного счетчика адреса подключены к входам дешифратора адреса.

| название | год | авторы | номер документа |

|---|---|---|---|

| Буферное запоминающее устройство | 1988 |

|

SU1583980A1 |

| Устройство для диагностики логических блоков | 1988 |

|

SU1672452A1 |

| Устройство для контроля логических блоков | 1986 |

|

SU1319035A1 |

| Устройство для измерения среднего числа импульсов в случайной импульсной последовательности | 1976 |

|

SU661388A2 |

| Умножитель частоты следованияиМпульСОВ | 1979 |

|

SU845290A1 |

| Многоканальный генератор импульсов | 1984 |

|

SU1167709A2 |

| Устройство для медианной фильтрации двумерных массивов | 1987 |

|

SU1524067A1 |

| Многоканальный статистический анализатор | 1980 |

|

SU959092A1 |

| Устройство для реализации быстрых преобразований в базисах дискретных ортогональных функций | 1985 |

|

SU1292005A1 |

| Умножитель частоты следования импульсов | 1980 |

|

SU923002A2 |

Авторы

Даты

1976-04-30—Публикация

1974-06-26—Подача