(21)4606591/24-24

(22)11.08.88

(46) 07.08.90. Бюл. № 29

(72) Э. Л. Джанджулян, Р. А. Мирзоян

и Г. А. Ягджян

(53)681.327.6 (088.8)

(56)Патент Франции № 2440058, кл. G 11 С 19/00, опублик. 1985.

Авторское свидетельство СССР № 1200335, кл. G 11 С 19/00, 1984.

(54)БУФЕРНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

(57)Изобретение относится к вычислительной технике, а именно к регистровым запоминающим устройствам, и может быть применено в вычислительных комплексах для обмена информацией между оперативной памятью ЭВМ и внешними запоминающими устройствами (ВЗУ). Целью изобретения является расширение области применения БЗУ за счет независимых записи и чтения данных. БЗУ содержит три коммутатора, два накопителя, элементы И, счетчик адресов записи, счетчик адресов чтения, два реверсивных счетчика, блок управления, элементы НЕ, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ. Цель достигается путем организации возможности записи или чтения из накопителя до завершения текущего режима работы БЗУ и блокировки записи в накопитель или чтения из накопителя во время работы с высокоскоростными ВЗУ. 1 з. п. ф-лы, 2 ил

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения между ЭВМ, оперативной памятью и внешним запоминающим устройством | 1988 |

|

SU1531103A1 |

| Буферное запоминающее устройство | 1985 |

|

SU1257704A1 |

| Буферное запоминающее устройство | 1987 |

|

SU1444893A1 |

| Буферное запоминающее устройство | 1982 |

|

SU1111202A1 |

| Устройство для сопряжения ЭВМ с телеграфными аппаратами | 1984 |

|

SU1251092A1 |

| Канал обмена | 1986 |

|

SU1410045A1 |

| Устройство для сопряжения источника и приемника информации | 1985 |

|

SU1290339A1 |

| Устройство для ввода информации | 1987 |

|

SU1432544A1 |

| Буферное запоминающее устройство | 1984 |

|

SU1163357A1 |

| Процессор для мультипроцессорной системы | 1985 |

|

SU1295410A1 |

Изобретение относится к вычислительной технике, а именно к регистровым запоминающим устройствам, и может быть применено в вычислительных комплексах для обмена информацией между оперативной памятью ЭВМ и внешними запоминающими устройствами (ВЗУ). Целью изобретения является расширение области применения БЗУ за счет независимых записи и чтения данных. БЗУ содержит три коммутатора, два накопителя, элементы И, счетчик адресов записи, счетчик адресов чтения, два реверсивных счетчика, блок управления, элементы НЕ, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ. Цель достигается путем организации возможности записи или чтения из накопителя до завершения текущего режима работы БЗУ и блокировки записи в накопитель или чтения из накопителя во время работы с высокоскоростными ВЗУ. 1 з.п. ф-лы, 2 ил.

Изобретение относится к вычислительной технике, а именно к регистровым запоминающим устройствам, и может быть применено в вычислительных комплексах для обмена информацией между оперативной памятью ЭВМ и внешними запоминающими устройствами (ВЗУ).

Цель изобретения - расширение области применения устройства за счет независимых записи и чтения данных.

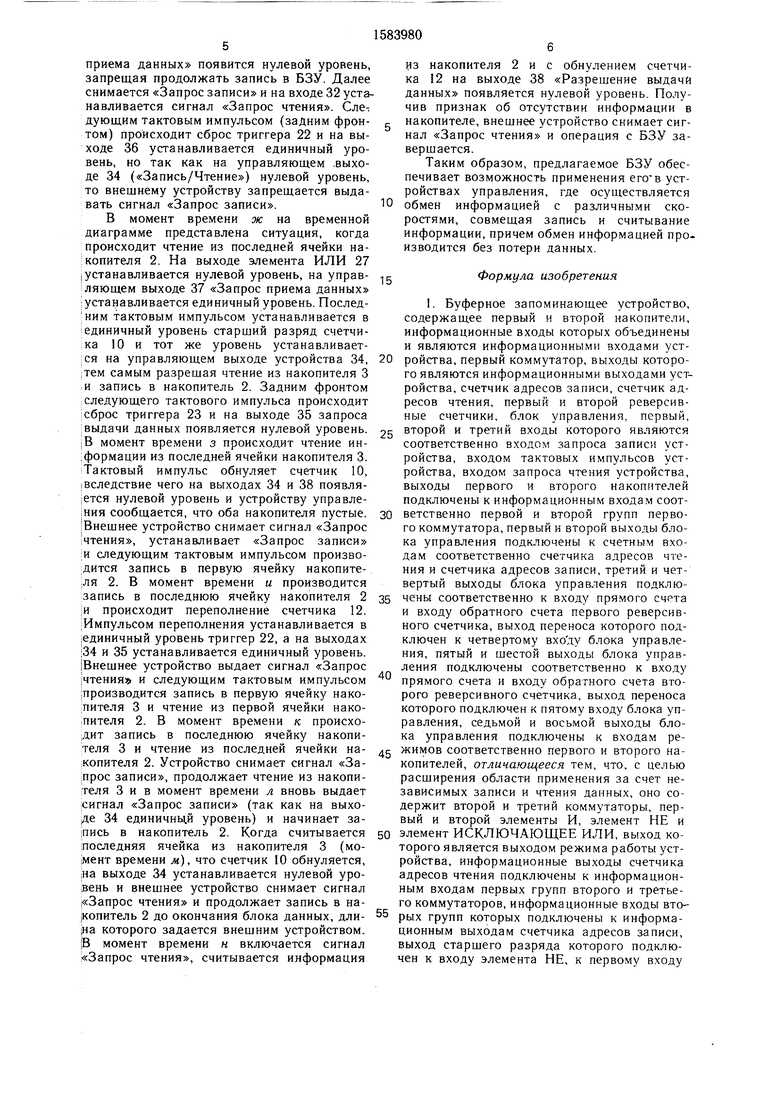

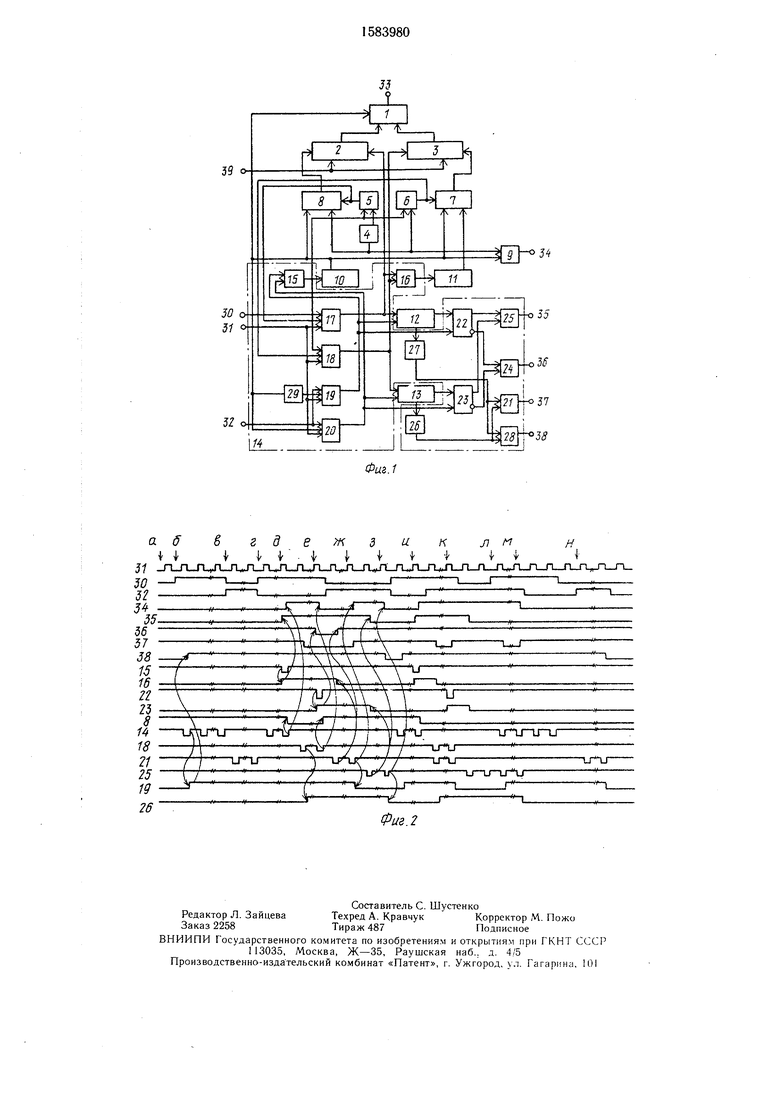

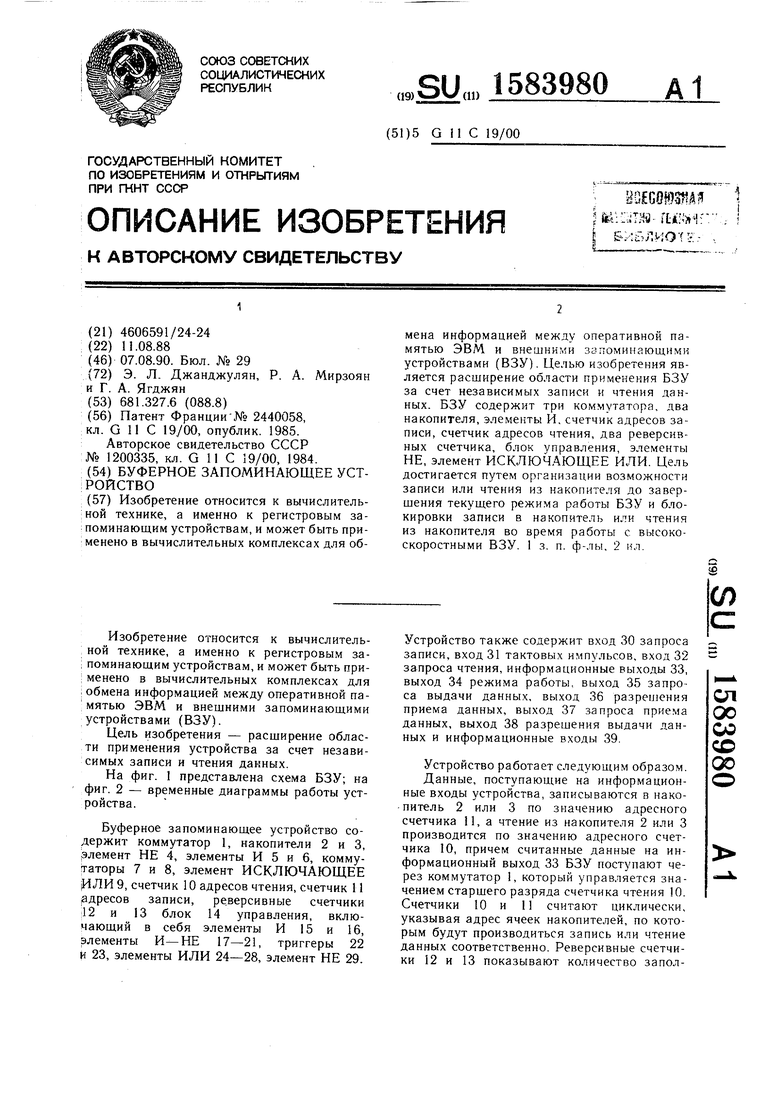

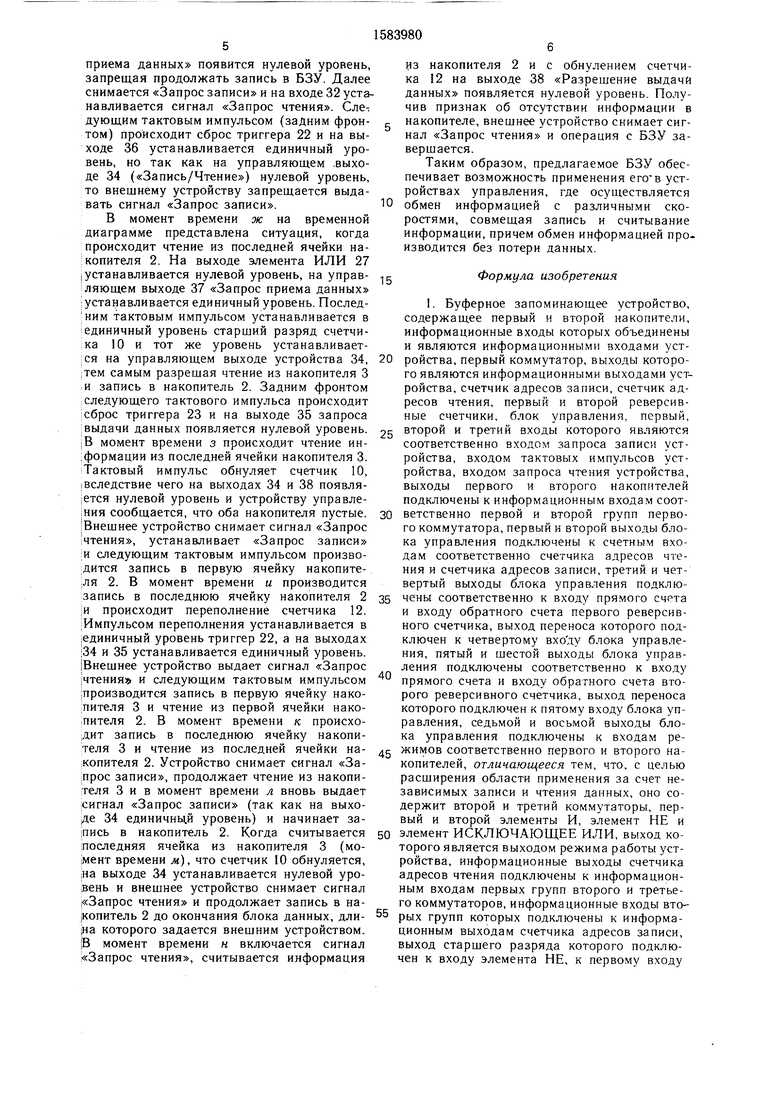

На фиг. 1 представлена схема БЗУ; на фиг. 2 - временные диаграммы работы устройства.

Буферное запоминающее устройство содержит коммутатор 1, накопители 2 и 3, элемент НЕ 4, элементы И 5 и 6, коммутаторы 7 и 8, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 9, счетчик 10 адресов чтения, счетчик 11 адресов записи, реверсивные счетчики 12 и 13 блок 14 управления, включающий в себя элементы И 15 и 16, элементы И-НЕ 17-21, триггеры 22 к 23, элементы ИЛИ 24-28, элемент НЕ 29.

Устройство также содержит вход 30 запроса записи, вход 31 тактовых импульсов, вход 32 запроса чтения, информационные выходы 33, выход 34 режима работы, выход 35 запроса выдачи данных, выход 36 разрешения приема данных, выход 37 запроса приема данных, выход 38 разрешения выдачи данных и информационные входы 39.

Устройство работает следующим образом.

Данные, поступающие на информационные входы устройства, записываются в накопитель 2 или 3 по значению адресного счетчика 11, а чтение из накопителя 2 или 3 производится по значению адресного счетчика 10, причем считанные данные на информационный выход 33 БЗУ поступают через коммутатор 1, который управляется значением старшего разряда счетчика чтения 10. Счетчики 10 и 11 считают циклически, указывая адрес ячеек накопителей, по которым будут производиться запись или чтение данных соответственно. Реверсивные счетчики 12 и 13 показывают количество заполСП

оо со со

00

ненных ячеек накопителей 2 или 3 соответственно. Разрядность счетчиков 10-13 выбирается, исходя из объема накопителей 2 и 3. Так, если объем каждого накопителевые уровни, а на выходах 36 и 37 - единичные уровни.

С приходом сигнала «Запрос записи на вход 30 устройства (момент времени б)

«-разряд «VI.I

ля равен 2, то счетчики 10 и 11 должны g на выходе элемента И 5 устанавливается единичный уровень, тем самым разрешая подключить выходы счетчика 11 через коммутатор 8 к адресным входам накопителя 2, а также прохождение тактового импульса от входа устройства 31. По леред- Ю нему фронту тактового импульса через элемент И 16 происходит запись данных с информационного входа 39 в накопитель 2 по адресу счетчика 11, а по заднему фронту тактового импульса происходит модификация счетчика 11 и счетчика 12. На выходе 38 разрешения выдачи данных появляется единичный уровень, так как значение счетчика 12 отлично от нуля. После некоторых циклов записи в БЗУ устройство управления снимает сигнал «Запрос записи и подает

быть гг+1 -разрядными, а 12 и 13 ными.

Старший разряд счетчика 11 определяет, в какой из накопителей можно производить запись.

Выходы элементов И 5 и 6 блокируют элементы И-НЕ 17 и 18 для прохождения тактового импульса по записи, а старший разряд счетчика 10 блокирует элементы И- НЕ 19 и 20 для прохождения тактового импульса по чтению. Выходы элементов И- 15 НЕ 17 и 18 модифицируют счетчики 12 и 13 соответственно по прямому счетному входу, производят запись в накопитель 2 или 3 и посредством элемента И 16 модифицируют счетчик 11. Выходы элементов

И-НЕ 19 и 20 модифицируют счетчики 1220 сигнал «Запрос чтения по входу 32 уст- и 13 по реверсивному счетному входу соот- ройства (момент времени в), ветственно, сбрасывают управляющие триг-На выходе элемента И 5 устанавливает- геры 22 и 23, если они установлены, и по- ся нулевой уровень, разрешая подключить вы- средством элемента И 15 модифицируют ходы счетчика 10 через коммутатор 8 к адрес- счетчик 10 чтения. Единичные выходы управ-25 ным входам накопителя 2, прохождение тактоляющих триггеров 22 и 23 поступают на элемент ИЛИ 25, выход которого является запросом выдачи данных в БЗУ, а нулевые вы ходы подключены к элементу ИЛИ 24, выход которого является признаком разрешевого импульса через элемент И-НЕ 19 и выдачу информации от накопителя 2 через коммутатор 1 на информационный выход 33, так как значение старшего разряда счетчика 10 равно нулю. По заднему фронту

ния приема данных в накопители 2 и 3. 30 тактового импульса происходит модификация счетчика 10 через элемент И 15 по счетному входу и счетчика 12 по обратному счетному входу.

При отсутствии сигналов «Запрос записи и «Запрос чтения на информационном вы- сом приема данных из ВЗУ, а выход эле- 35 ходе 33 БЗУ находится информация ячейки мента ИЛИ 28 - признаком разрешения накопителя, адрес которого указывает счет- выдачи данных из накопителей 2 или 3. чик 10 (на управляющих входах коммутаВыходы счетчиков 12 и 13 поступают на n-входовые элементы ИЛИ 27 и 26 соответственно, выходы которых поступают на элемент И-НЕ 21 и на элемент ИЛИ 28. Выход элемента И-НЕ 21 является запроВыходы 35 и 37 дают возможность без потери данных производить обмен между ОП и ВЗУ при соблюдении следующего условия: объемы накопителей должны быть равными объему блока данных ВЗУ. Так, при операции «Запись (данные считываются из ОП и записываются в ВЗУ) устройство управления ВЗУ выдает сигнал «Чтение на вход 32 при переполнении одного из накопителей, признаком которого является появление единичного уровня на выходе 35 БЗУ, а при операции «Чтение (данные считываются из ВЗУ и записываются в ОП) устройство управления БЗУ выдает сигнал записи на вход 30 БЗУ при отсутствии данных в одном из накопителей, признаком кототоров 7 и 8 - нулевой уровень).

В момент времени г на временной диаграмме показана ситуация, когда после нескольких циклов чтения устройство управления продолжает запись в накопитель 2.

В момент времени д производится запись в последнюю ячейку накопителя 2. 45 Выход переполнения счетчика 12 устанавливает триггер 22, а задний фронт тактового импульса устанавливает в единицу старший разряд счетчика 11 и на управляющем выходе устройства 34 появляется признак режима работы («Запись/Чтение),разрешая устройству продолжать операцию в режиме одновременной записи и чтения с БЗУ. Единичный уровень на выходе триггера 22 выдает на выход 35 устройства запрос выдачи данных. Если будет продолжена запись в БЗУ, то произойдет пере50

В момент времени д производится запись в последнюю ячейку накопителя 2. 45 Выход переполнения счетчика 12 устанавливает триггер 22, а задний фронт тактового импульса устанавливает в единицу старший разряд счетчика 11 и на управляющем выходе устройства 34 появляется признак режима работы («Запись/Чтение),раз решая устройству продолжать операцию в режиме одновременной записи и чтения с БЗУ. Единичный уровень на выходе триггера 22 выдает на выход 35 устройства запрос выдачи данных. Если будет продолжена запись в БЗУ, то произойдет перерого является появление единичного уровня на выходе 37 БЗУ.

На временной диаграмме (фиг. 2, момент

времени а) последовательно исходное состоя- . „.

ние БЗУ. Счетчики 10-13 и триггеры 22 и 23 5Б полнение накопителя 3 (момент времени е) сброшены сигналом начальной установки (не и счетчика 13. Триггер 23 установится в показано). При этом на управляющих вы-- «1, а старший разряд счетчика 11 в «О ходах БЗУ 34, 35 и 38 установлены ну- и на управляющем выходе 36 «Разрешение

левые уровни, а на выходах 36 и 37 - единичные уровни.

С приходом сигнала «Запрос записи на вход 30 устройства (момент времени б)

VI.I

сигнал «Запрос чтения по входу 32 уст- ройства (момент времени в), На выходе элемента И 5 устанавливает- ся нулевой уровень, разрешая подключить вы- ходы счетчика 10 через коммутатор 8 к адрес- ным входам накопителя 2, прохождение тактового импульса через элемент И-НЕ 19 и выдачу информации от накопителя 2 через коммутатор 1 на информационный выход 33, так как значение старшего разряда счетчика 10 равно нулю. По заднему фронту

тактового импульса происходит модификаторов 7 и 8 - нулевой уровень).

В момент времени г на временной диаграмме показана ситуация, когда после нескольких циклов чтения устройство управления продолжает запись в накопитель 2.

В момент времени д производится запись в последнюю ячейку накопителя 2. 5 Выход переполнения счетчика 12 устанавливает триггер 22, а задний фронт тактового импульса устанавливает в единицу старший разряд счетчика 11 и на управляющем выходе устройства 34 появляется признак режима работы («Запись/Чтение),разрешая устройству продолжать операцию в режиме одновременной записи и чтения с БЗУ. Единичный уровень на выходе триггера 22 выдает на выход 35 устройства запрос выдачи данных. Если будет продолжена запись в БЗУ, то произойдет пере0

. „.

Б полнение накопителя 3 (момент времени е) и счетчика 13. Триггер 23 установится в «1, а старший разряд счетчика 11 в «О и на управляющем выходе 36 «Разрешение

приема данных появится нулевой уровень, запрещая продолжать запись в БЗУ. Далее снимается «Запрос записи и на входе 32 устанавливается сигнал «Запрос чтения. Следующим тактовым импульсом (задним фронтом) происходит сброс триггера 22 и на выходе 36 устанавливается единичный уровень, но так как на управляющем выходе 34 («Запись/Чтение) нулевой уровень, то внешнему устройству запрещается выдавать сигнал «Запрос записи.

В момент времени ж на временной диаграмме представлена ситуация, когда происходит чтение из последней ячейки накопителя 2. На выходе элемента ИЛИ 27 устанавливается нулевой уровень, на управляющем выходе 37 «Запрос приема данных устанавливается единичный уровень. Последним тактовым импульсом устанавливается в единичный уровень старший разряд счетчика 10 и тот же уровень устанавливает10

15

из накопителя 2 и с обнулением счетчика 12 на выходе 38 «Разрешение выдачи данных появляется нулевой уровень. Получив признак об отсутствии информации в накопителе, внешнее устройство снимает сигнал «Запрос чтения и операция с БЗУ завершается.

Таким образом, предлагаемое БЗУ обеспечивает возможность применения его в устройствах управления, где осуществляется обмен информацией с различными скоростями, совмещая запись и считывание информации, причем обмен информацией производится без потери данных.

Формула изобретения

25

30

35

го являются информационными выходами устройства, счетчик адресов записи, счетчик адресов чтения, первый и второй реверсивные счетчики, блок управления, первый, второй и третий входы которого являются соответственно входом запроса записи устройства, входом тактовых импульсов устройства, входом запроса чтения устройства, выходы первого и второго накопителей подключены к информационным входам соответственно первой и второй групп первого коммутатора, первый и второй выходы блока управления подключены к счетным входам соответственно счетчика адресов чтения и счетчика адресов записи, третий и четвертый выходы блока управления подключены соответственно к входу прямого счета и входу обратного счета первого реверсивного счетчика, выход переноса которого подключен к четвертому входу блока управления, пятый и шестой выходы блока управления подключены соответственно к входу прямого счета и входу обратного счета второго реверсивного счетчика, выход переноса которого подключен к пятому входу блока управления, седьмой и восьмой выходы блока управления подключены к входам ре45 жимов соответственно первого и второго накопителей, отличающееся тем, что, с целью расширения области применения за счет независимых записи и чтения данных, оно содержит второй и третий коммутаторы, первый и второй элементы И, элемент НЕ и

50 элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого является выходом режима работы устройства, информационные выходы счетчика адресов чтения подключены к информационным входам первых групп второго и третьего коммутаторов, информационные входы вто55 рых групп которых подключены к информационным выходам счетчика адресов записи, выход старшего разряда которого подключен к входу элемента НЕ, к первому входу

40

из накопителя 2 и с обнулением счетчика 12 на выходе 38 «Разрешение выдачи данных появляется нулевой уровень. Получив признак об отсутствии информации в накопителе, внешнее устройство снимает сигнал «Запрос чтения и операция с БЗУ завершается.

Таким образом, предлагаемое БЗУ обеспечивает возможность применения его в устройствах управления, где осуществляется обмен информацией с различными скоростями, совмещая запись и считывание информации, причем обмен информацией производится без потери данных.

Формула изобретения

0

5

го являются информационными выходами устройства, счетчик адресов записи, счетчик адресов чтения, первый и второй реверсивные счетчики, блок управления, первый, второй и третий входы которого являются соответственно входом запроса записи устройства, входом тактовых импульсов устройства, входом запроса чтения устройства, выходы первого и второго накопителей подключены к информационным входам соответственно первой и второй групп первого коммутатора, первый и второй выходы блока управления подключены к счетным входам соответственно счетчика адресов чтения и счетчика адресов записи, третий и четвертый выходы блока управления подключены соответственно к входу прямого счета и входу обратного счета первого реверсивного счетчика, выход переноса которого подключен к четвертому входу блока управления, пятый и шестой выходы блока управления подключены соответственно к входу прямого счета и входу обратного счета второго реверсивного счетчика, выход переноса которого подключен к пятому входу блока управления, седьмой и восьмой выходы блока управления подключены к входам ре5 жимов соответственно первого и второго накопителей, отличающееся тем, что, с целью расширения области применения за счет независимых записи и чтения данных, оно содержит второй и третий коммутаторы, первый и второй элементы И, элемент НЕ и

0 элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого является выходом режима работы устройства, информационные выходы счетчика адресов чтения подключены к информационным входам первых групп второго и третьего коммутаторов, информационные входы вто5 рых групп которых подключены к информационным выходам счетчика адресов записи, выход старшего разряда которого подключен к входу элемента НЕ, к первому входу

0

второго элемента И и к первому входу элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход которого подключен к выходу старшего разряда счетчика адресов чтения, к управляющему входу первого коммутатрора и шестому входу блока управления, выход элемента НЕ подключен к первому входу первого элемента И, второй вход которого подключен к второму входу второго элемента И и к девятому выходу блока управления, выход первого элемента И подключен к управляющему входу второго коммутатора и седьмому входу блока управления, восьмой вход которого подключен к управляющему входу третьего коммутатора и выходу второго элемента И, выходы второго и третьего коммутаторов, подключенных к адресным входам соответственно первого и второго накопителей, информационные выходы первого и второго реверсивных счетчиков подключены к входам соответственно первой и второй групп блока управления, десятый, одиннадцатый, двенадцатый и тринадцатый выходы блока управления являются соответственно выходом запроса выдачи данных, выходом разрешения приема данных, выходом запроса приема данных и выходом разрешения выдачи данных устройства.

2 Устройство по п. 1, отличающееся тем, что блок управления содержит первый и второй триггеры, элементы И-НЕ, элементы ИЛИ, элементы И и элемент НЕ, вход которого является шестым входом блока управления и подключен к первому входу первого элемента И-НЕ, выход которого подключен к первому входу первого элемента И, к входу сброса первого триггера и является шестым выходом блока управления, выход элемента НЕ подключен к первому входу второго элемента И-НЕ, выход которого является четвертым выходом блока управления и подключен к входу сброса второго триггера и второму входу первого эле0

0

мента И, выход которого является первым выходом блока управления, второй вход первого элемента И-НЕ является третьим входом блока управления и подключен к

второму входу второго элемента И-НЕ, третий вход которого является вторым входом блока управления и подключен к третьему входу первого элемента И-НЕ и первым входам третьего и четвертого элементов И- НЕ, вторые входы которых являются соответственно восьмым и седьмым входами блока управления, третий вход третьего элемента И-НЕ является первым входом и девятым выходом блока управления и подключен к третьему входу четвертого элемента

И-НЕ, выход которого является третьим и седьмым выходами блока управления и подключен к первому входу второго элемента И, выход которого является вторым выходом блока управления, выход третьего элемента И-НЕ является пятым и восьмым выходами блока управления и подключен к второму входу второго элемента И, прямые выходы первого и второго триггеров подключены к входам первого элемента ИЛИ, выход которого является десятым выходом блока управ5 ления, инверсные выходы первого и второго триггеров подключены к входам второго элемента ИЛИ, выход которого является одиннадцатым выходом блока управления, входы установки первого и второго триггеров являются соответственно пятым и

0 шестым входами блока управления, выход третьего элемента ИЛИ подключен к первым входам пятого элемента И-НЕ и пятого элемента ИЛИ, выходы которых являются соответственно двенадцатым и тринадцатым выходами блока управления, выход четвер5 того элемента ИЛИ подключен к вторым входам пятого элемента И-НЕ и пятого элемента ИЛИ, входы третьего и четвертого элементов ИЛИ являются входами соответственно первой и второй групп блока управления.

39 о

30 о

а. б ёгде

IIIJ-IJr

31 30 32 J4 3556-ГГ

57

38

И

so

Л Л7

I I

Я

Фиг.2

Авторы

Даты

1990-08-07—Публикация

1988-08-11—Подача