1

Изобретение относится к запоминающим устройствам.

Известное буферное запоминающее устроство, содержащее матрицу оперативной памяти, информационные входы и выходы которой через элементы И подключены соответственно к выходам и входам входного и выходного регистров, счетчики адресов записи и считывания, соединенные с блоком управления, дещифратор адреса, подключенный к матрице оперативной памяти, характеризуется большими аппаратурными затратами.

Для упрощения предлагаемое устройство содержит генератор импульсов, выходы которого подключены к блоку управления, элементы ИЛИ по числу разрядов счетчиков, дополнительные элементы И, информационные входы которых подключены к выхсдам соответствующих счетчиков, управляющие входы - к блоку управления, а выходы - к входам соответствующих элементов ИЛИ, выходы которых соединены с входами дещифратора адреса.

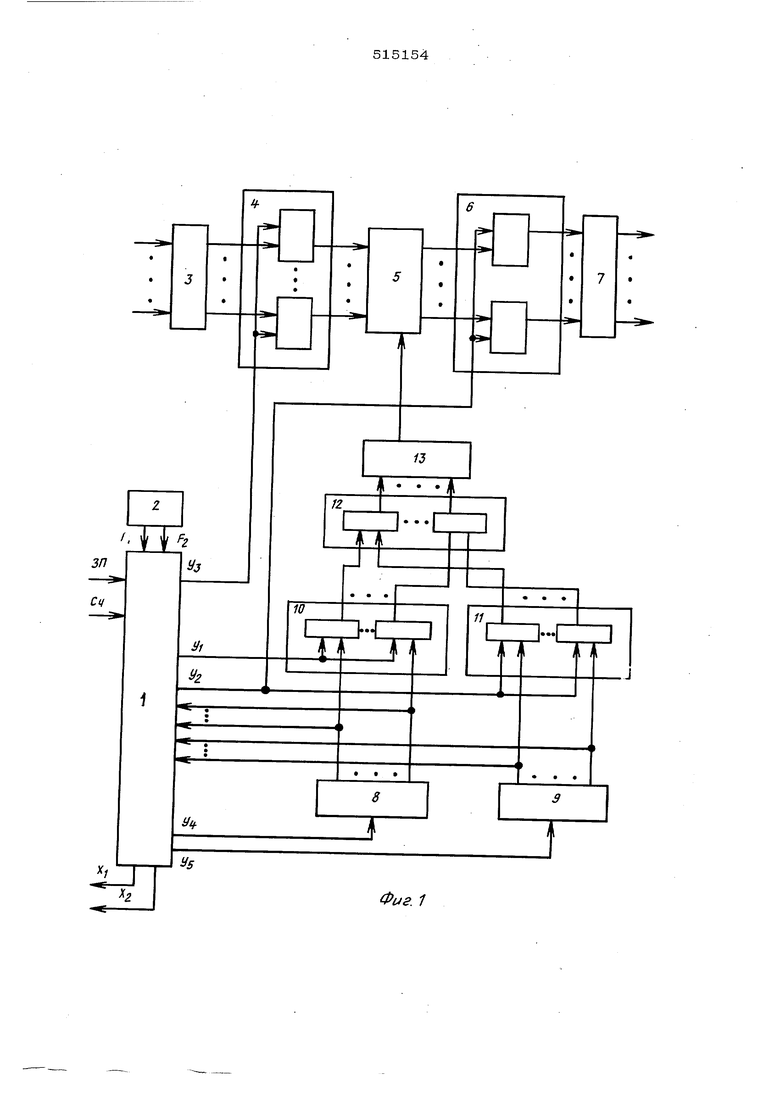

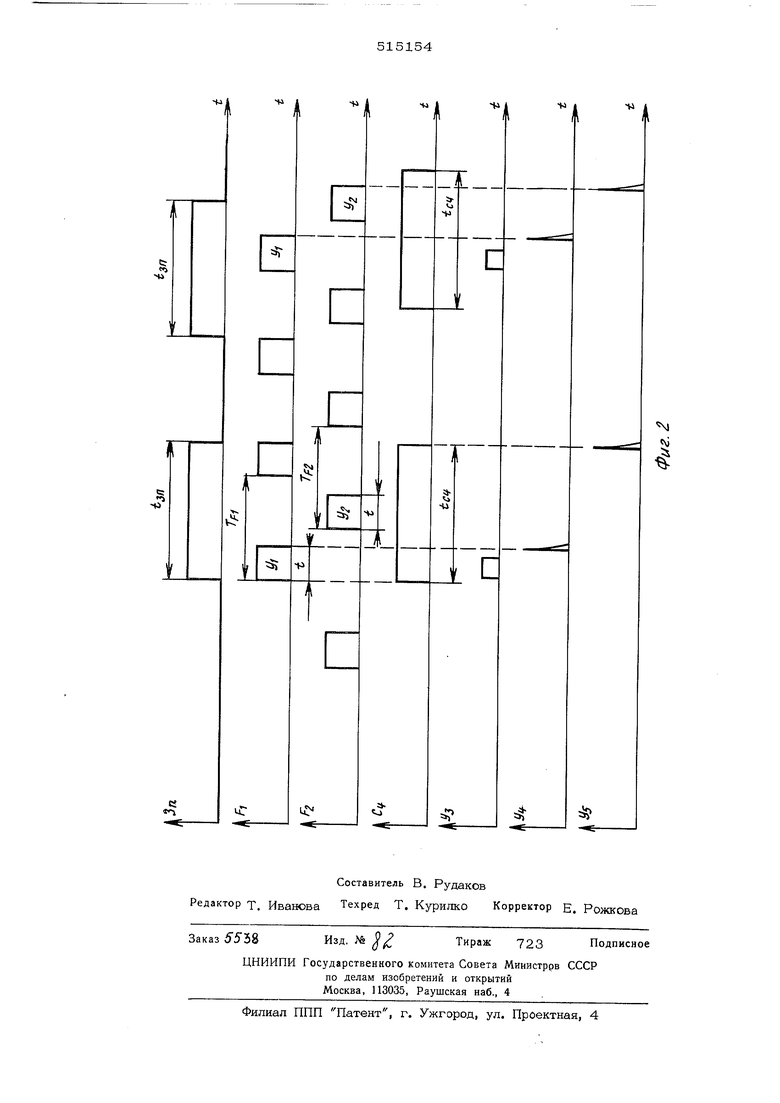

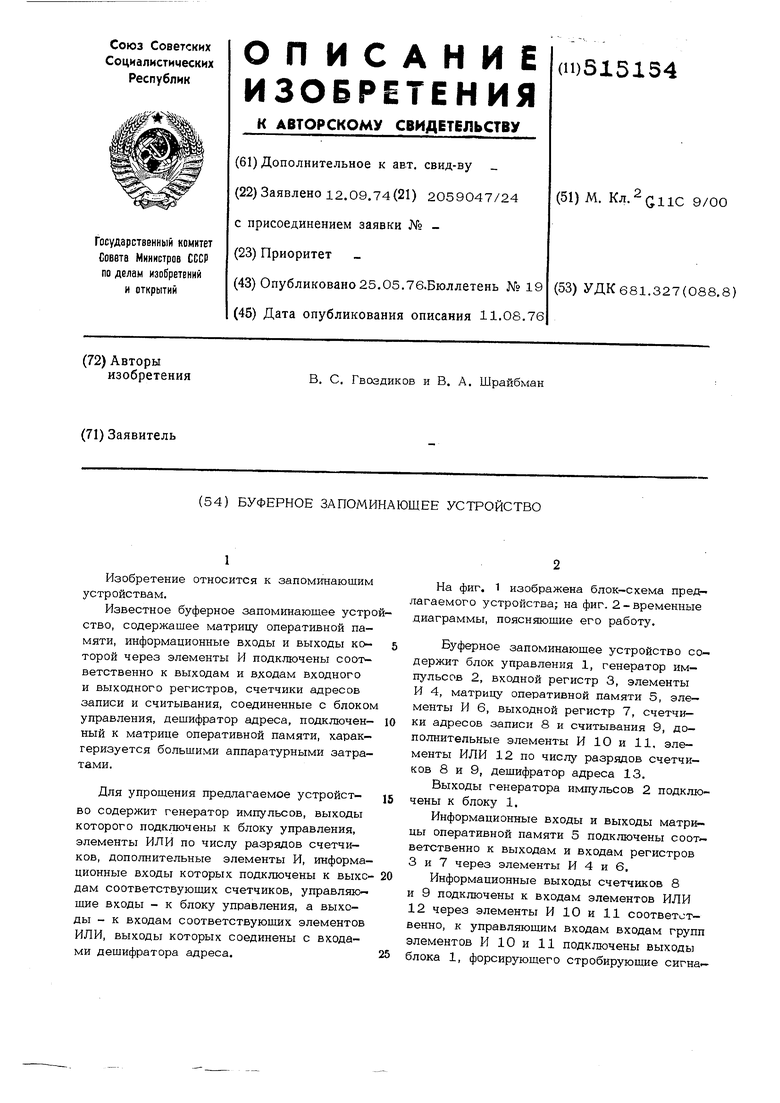

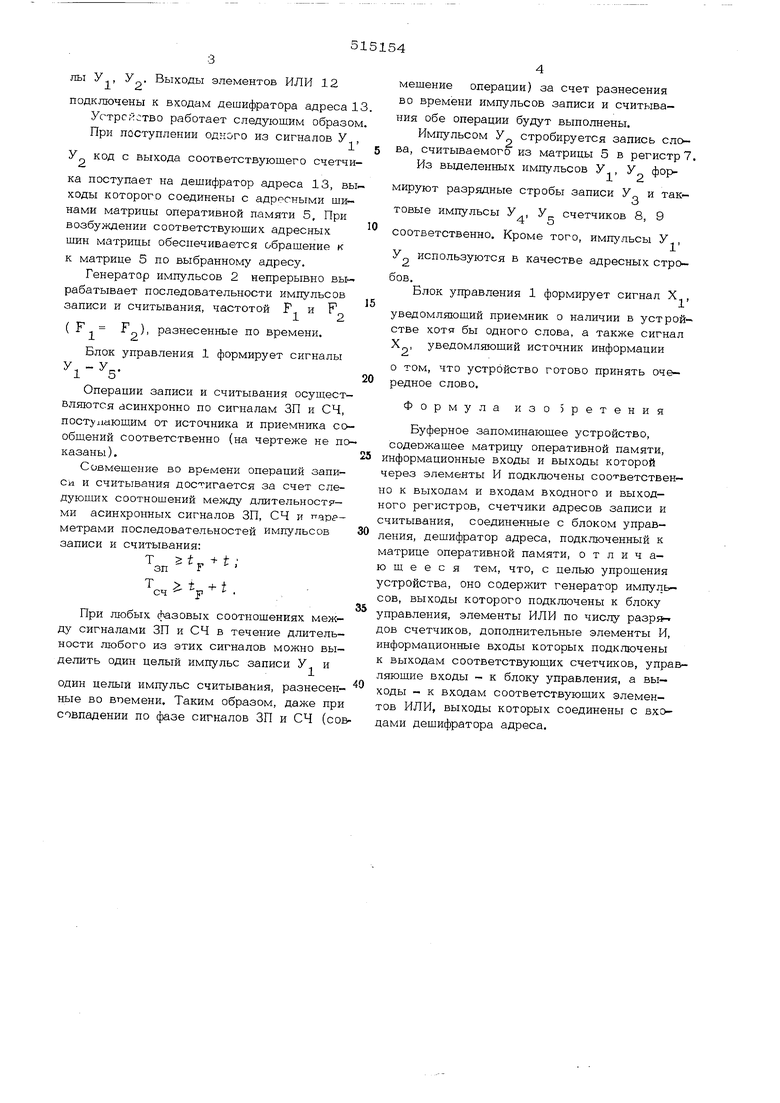

На фиг. 1 изображена блок-схема предлагаемого устройства; на фиг. 2-временные диаграммы, поясняющие его работу.

Буферное запоминающее устройство содержит блок управления 1, генератор импульсов 2, входной регистр 3, элементы И 4, матрицу оперативной памяти 5, элементы И 6, выходной регистр 7, счетчики адресов записи 8 и считывания 9, дополнительные элементы И 10 и 11, элементы ИЛИ 12 по числу разрядов счетчиков 8 и 9, дешифратор адреса 13.

Выходы генератора импульсов 2 подключены к блоку 1.

Информационные входы и выходы матрицы оперативной памяти 5 подключены соот ветственно к выходам и входам регистров 3 и 7 через элементы И 4 и 6,

Информационные выходы счетчиков 8 и 9 подключены к входам элементов ИЛИ 12 через элементы И 10 и 11 соответственно, к управляющим входам входам групп элементов И 10 и 11 подключены выходы блока 1, форсирующего стробируюшие сигналы У У . Выходы элементов ИЛИ 12 подключены к входам дешифратора адреса Устройство работает следующим образо При поступлении одного из сигналов У У код с выхода соответствующего счетчи ка поступает на дешифратор адреса 13, вы ходы которого соединены с адресными щинами матрицы оперативной памяти 5, При возбуждении соответствующих адресных шин матрицы обеспечивается обращение к к матрице 5 по выбранному адресу. Генератор импульсов 2 непрерывно вырабатывает последовательности импульсов записи и считывания, частотой F и F ( F F ), разнесенные по времени. Блок управления 1 формирует сигналы 1 - 5Операции записи и считывания осущест вляются асинхронно по сигналам ЗП и СЧ, поступающим от источника и приемника со общений соответственно (на чертеже не по казаны). Совмещение во времени операций запиен и считывания достигается за счет следующих соотношений между длительности- ми асинхронных сигналов ЗП, СЧ и ггареметрами последовательностей импульсов записи и считывания: .. При любых фазовых соотношениях между сигналами ЗП и СЧ в течение длительности любого из этих сигналов можно выделить один целый импульс записи У и ОДИН целый импульс считывания, разнесенные во впемени. Таким образом, даже при совпадении по фазе сигналов ЗП и СЧ (со мещение операции) за счет разнесения во времени импульсов записи и считывания обе операции будут выполнены. Импульсом У стробируется запись слова, считываемого из матрицы 5 в регистр. Из вьщеленных импульсов У , У формируют разрядные стробы записи У и тактовые импульсы У , У счетчиков 8, 9 соответственно. Кроме того, импульсы У , У используются в качестве адресных стробов. Блок управления 1 формирует сигнал X , уведомляющий приемник о наличии в устройстве хотя бы одного слова, а также сигнал X , уведомляющий источник информации о том, что устройство готово принять очередное слово. Формула изобретения Буферное запоминающее устройство, содержащее матрицу оперативной памяти, информационные входы и выходы которой через элементы И подключены соответственно к выходам и входам входного и выходного регистров, счетчики адресов записи и считывания, соединенные с блоком управления, дешифратор адреса, подключенный к матрице оперативной памяти, отличающееся тем, что, с пелью упрощения устройства, оно содержит генератор импульсов, выходы которого подключены к блоку управления, элементы ИЛИ по числу разря-. дов счетчиков, дополнительные элементы И, информационные входы которых подключены к выходам соответствующих счетчиков, управляющие входы - к блоку управления, а выходы - к входам соответствующих элементов ИЛИ, выходы которых соединены с входами дешифратора адреса.

| название | год | авторы | номер документа |

|---|---|---|---|

| Буферное запоминающее устройство | 1980 |

|

SU942139A1 |

| Буферное запоминающее устройство | 1978 |

|

SU767836A1 |

| Буферное запоминающее устройство | 1983 |

|

SU1096692A1 |

| Программируемая линия задержки | 1986 |

|

SU1406753A1 |

| Устройство для диагностирования логических блоков | 1986 |

|

SU1520518A1 |

| Оперативное запоминающее устройство | 1983 |

|

SU1095233A1 |

| Буферное запоминающее устройство | 1985 |

|

SU1287238A1 |

| СИСТЕМА РАСПРЕДЕЛЕНИЯ РЕСУРСОВ | 2000 |

|

RU2189073C2 |

| Многоканальное буферное запоминающее устройство | 1980 |

|

SU903971A1 |

| УСТРОЙСТВО СОРТИРОВКИ СИМВОЛОВ | 1992 |

|

RU2067317C1 |

Авторы

Даты

1976-05-25—Публикация

1974-09-12—Подача