С5 БУФЕРНОЕ .ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Буферное запоминающее устройство | 1983 |

|

SU1096692A1 |

| Буферное запоминающее устройство | 1978 |

|

SU767836A1 |

| Буферное запоминающее устройство | 1988 |

|

SU1583938A1 |

| Буферное запоминающее устройство | 1980 |

|

SU932566A1 |

| Устройство для ввода информации | 1979 |

|

SU911500A2 |

| Буферное запоминающее устройство | 1985 |

|

SU1257704A1 |

| Буферное запоминающее устройство | 1989 |

|

SU1691891A1 |

| Буферное запоминающее устройство | 1982 |

|

SU1049968A1 |

| Постоянное запоминающее устройство | 1977 |

|

SU705521A1 |

| Буферное оперативное запоминающее устройство | 1988 |

|

SU1559379A1 |

1

Изобретение относится к технике систем передачи данных и может использоваться в центрах коммутации сообщений.

Известно буферное запоминающее

устройство (БЗУ), которое может использоваться для накопления и промежуточного хранения сообщений, представляющих собой законченные в смысловом отношении блоки данных. Устрой- ю ство содержит блок управленияj генератор импульсов, входйой регистр,элементы И, матрицу оперативной памяти, выходной регистр, счетчики адресов записи и считывания, элемент ИЛИ и is дешифратор адресов П.

Недостатком известного устройства является его сложность.

Наиболее близким к предлагаемому по технической сущности является 20 БЗУ, содержащее регистр входного слова, входные элементы И, счетчики адресов, дешифратор адресов, матрицы памяти, элементы ИЛИ, регистр выходного лова и узел управления. Источник сообщений сопровождает входные сло ва синхроимпульсами записи ЗП.Если свободна первая матрица памяти. То в нее осуществляется запись. Входное слово записывается в регистр входного слова. Сигнал управления, поступающий на управляющие входы первых входных элементов И, разрешает перезапись содержимого регистра входного слова .в первую матрицу памяти.

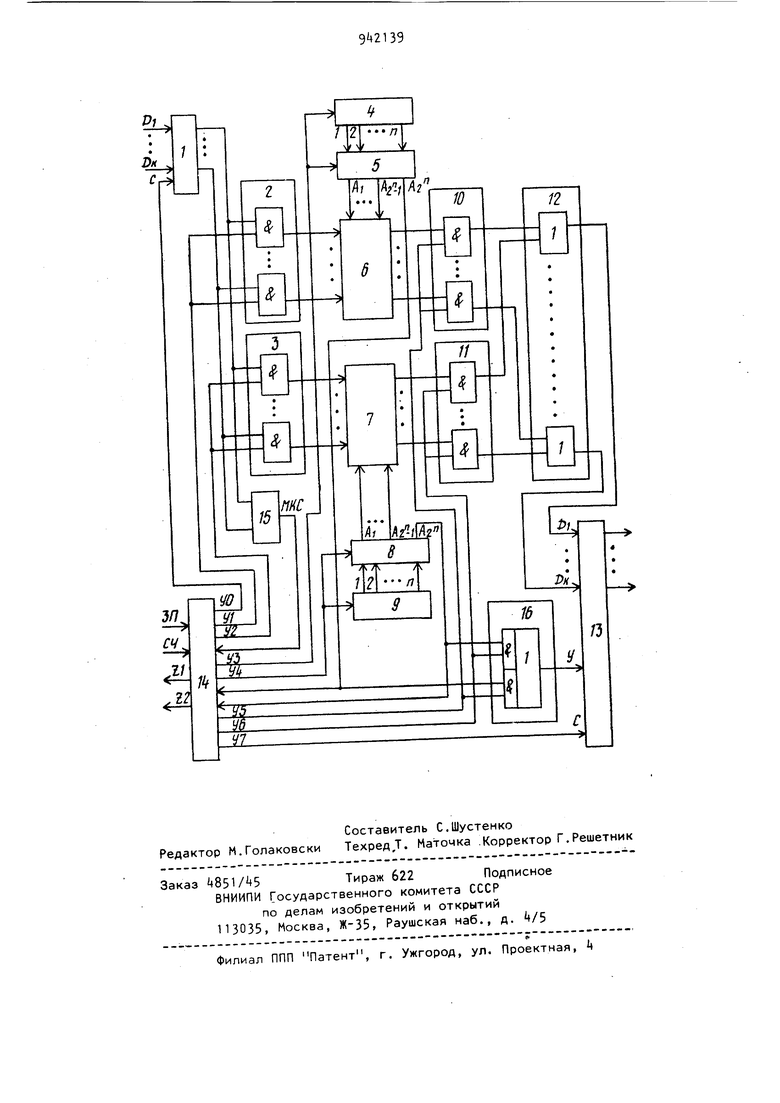

После заполнения первой матрицы памяти узел управления вырабатывает сигнал занятости, уведомляющий приемник сообщений о наличии в БЗУ сообщения. Одновременно наминается запись, поступающего на вход БЗУ нового сообщения во вторую матрицу памяти, если она свободна. Сигнал управления, поступающий на управляющие входы вторых входных элементов И, разрешает перезапись содержимого регистра входного слова в вторую матрицу памяти. Последовательная выборка адресов мат3риц памяти осуществляется с помощью счетчиков адреса и дешифраторов адресов. Считывание информации из БЗУ осу ществляется при поступлении от прие ника сообщений синхроимпульсов СЧ. Сигнал управления, поступающий н управляющие входы первых выходных элементов И, разрешает прохождение слова из второй матрицы памяти чере элементы ИЛИ на входы регистра выхо ного слова. Если приемник сообщений своевременно реагирует на сигнал занятости запись в БЗУ осуществляют практичес ки непрерывно благодаря поочередному освобождению матрицы памяти. В п тивном случае БЗУ заполняется полностью и узлом управления вырабатывается сигнал, уведомляющий о том, что дальнейшая запись сообщений в БЗУ невозможна. 8 процессе передачи в сообщениях могут возникать искажения (сбои) информации. Способы обнаружения и исправления как одиночных, так и групповых сбоев текстовой части сообщения достаточно известны. Однако, -возможны сбои синхронизации, ведущие к искажению структуры и даже формата сообщения. Их восстановление в процессе обработки в реальном масштабе времени практчиески не возмо)йно. Характерным, признаком подобных сбоев является отсутствие в последнем слове сообщения кодовой :комбинации маркера конца сообщения 2. Недостатком известного устройства является возможность накопления им и передачи на обработку невосстановимых в дальнейшем сбойных сообщений. Кроме того, в устройстве запоминается кодовая комбинация последнего слова сообщения, которая является фиксированной для всех соо щений , что приводит к увеличению оборудования и снижению достовернос ти считываемых сообщений. Так, напр мер, в результате сбоя в последней ячейке любой из матриц памяти БЗУ сообщение может быть в дальнейшем снято с обработки. Цель изобретения - упрощение . устройства и повышение достоверности считывания. Поставленная цель достигается те что в буферное запоминающее устрой94ство, содержащее первый и второй накопители, информационные входы которых подключены к выходам элементов И соответственно первой и второй групп, адресные входы первого и второго накопителей подключены к выходам соответственно первого и второго дешифраторов, управляющие входы которых подключены к соответствующим выходам блока управления, информационные входы первого и второго дешифраторов подключены к выходам соответственно первого и второго счетчиков, управляющие входы которых подключены к соответствующим выходам. блока управления, информационные выходы нервого и второго накопителей подключены к одним входам элементов И соответственно третьей и четвертой групп, друг-ие входы которых подключены к соответствующим выходам блока управления, выходы элементов И третьей группы подключены к одним входам элементов ИЛИ группы, другие входы которых подключены к выходам элементов И четвертой группы, одни входы элементов И первой и второй групп подключены к выходам первого регистра, управляющий вход которого подключен к соответствующему выходу блока управления, другие входы элементов И первой и второй групп подключены к соответствующим выходам блока управления, выходы элементов ИЛИ группы подключены к информационным входам второго регистра,первый управляющий вход которого подключен к соответствующему выходу блока управления, дополнительно введены третий дешифратор и элемент 2И-ИЛИ, одни входы которого подключены к соответствующим выходам первого и второго дешифраторов,а другие входы - к соответствующим выходам блока управления, выход элемента 2И-ИЛИ подключен ко второму управляющему входу второго регистра, входы третьего дешифратора подключены к выходам первого регистра, выход третьего дешифратора и соответствующие выходы первого и второго дешифраторов подключены ко входам блока управления. На чертеже представлена блок-схема устройства. Буферное запоминающее устройство содержит регистр 1 входного слова, элементы И 2 первой группы, элемен5ты И 3 второй группы, первый счетчи , первый дешифратор 5, первый нако питель 6, второй накопитель 7,второй дешифратор 8, второй счетчик 9, элементы И 10 третьей группы, элементы И 11 четвертой группы, группу элементов ИЛИ 12, регистр 13 выходн го слова.Блок k управления, третий дешифратор 15, элемент 16. Слова сообщения, сопровождаемые синхроимпульсами записи ЭП, поступа параллельно-последовательно от исто ника сообщений на информационные входы регистра 1 входного слова. Блок И управления формирует из синхроимпульсов ЗП сигналы УО, У1, УЗ, если запись осуществляется в на копитель 6, или сигналы УО, У2, УА, если запись осуществляется а накопи тель 7. По сигналу УО входное слйво записывается в регистр 1. Сигнал У1 разрешает перезапись входного сл ва из регистра 1 в накопитель б, а сигнал У2.- в накопитель 7. Последовательная выборка адресов накопителей 6 и 7 осуществляется со ответственно с помощью счетчиков 4, и дешифраторов 5 и 8. Выборка адреса разрешается си1- налом УЗ для накопителя 6 и сигналом у для накопителя 7. Изменение состояния счетчика 4 осуществляется по заднему фронту сигнала УЗ, а счетчика 9 - по заднему фронту сигнала У. Каждому состоянию любого из счетчиков соответствует определенная ячейка связанной с ним матрицы памяти за исключением последнего состояния, поскольку ячейка для последнего слова сообщения в матрицах памяти отсутствует. Таким образом, последнее слово сообщения в БЗУ не записывается. При записи в регистр 1 входного слова, содержащего кодрвую комбинацию маркера конца сообщения, дешифратором 15 формируется сигнал МКС, поступающий в блок I управления. Совпадение сигналя МКС с соответствующими из сигналов А1, формируемых дешифраторами 5 и 8 при записи информации, свидетельствует о наличии кодовой комбинации маркера конца в поОпеднем байте сообщения и вызывает появление на выходе блока 14 управления потенциального сигнала занятости 1.1, уведомляющего о нали 96 чии в БЗУ сообщения. Сигнал Zl присутствует на выходе БЗУ до тех пор, пока в БЗУ имеется хотя бы одно сообщение. После заполнения обеих матриц памяти БЗУ формирует сигнал 2. 2,уведомляющий о том, что запись сообщений в БЗУ невозможна. Если в результате сбоя в сообщении, записываемом в матрицу памяти, отсутствует слово с кодовой комбинацией маркера конца сообщения, то после окончания записи эта матрица памяти считается не заполненной. При этом БЗУ не формирует сигнал Z 1,если другая матрица памяти свободна, а также сигнал Z2, если другая матрица памяти заполнена. Таким образом, на входе БЗУ осуществляется ликвидация сообщений с искаженной структурой или форматом. Считывание слов сообщения из БЗУ осуществляется синхроимпульсами считывания С4, поступающими от приемника сообщений. При этом блок 14 управления формирует из синхроимпульсов СЧ сигналы УЗ, У5, У7 во время считыватывания сообщения из накопителя 7. Сигналом У7 осуществляется запись выходного слова в регистр 13. Если любой из счетчиков 4 и 9, работающий на считывание, находится в последнем состоянии, то на выходе Ai соответствующего дешифратора появляется сигнал, прохождение которого на установочный вход регистра 13 раз решается сигналом У5 при считывании сообщения из накопителя 6, и сигналом УЬ - при считывании сообщения из накопителя 7. Поступление сигнала на установочный вход регистра 13 обеспечивает появление на его выходах кодовой комбинации маркера конца сообщения. Предлагаемое изобретение позволяет повысить достоверность считываемого последнего слова сообщения за счет исключения возможности возникновения сбоев в процессе записи и хранения этого слова в БЗУ и одновременно упростить конструкцию БЗУ, уменьшив количество ячеек в каждой матрице памяти, так как не надо записывать и хранить слово, содержащее фиксированную кодовую комбинацию. Кроме того, из потока проходящей через БЗУ информации исключаются со79 21

общения с искаженной структурой или форматом.

Формула изобретения

Буферное запоминающее устройство, содержащее первый и второй накопители , информационные входы которых подключены к выходам элементов И соответственно первой и второй групп, адресные входы первого и второго накопителей подключены к выходам соответственно первого и второго дешифраторов, управляющие входы которых подключены к соответствующим выходам блока управления, информационные входы первого и второго дешифраторов подключены к , выходам соответственно первого и второго счетчиков, управляющие входы которых подключены к соответствующим выходам блока управления, информационные выходы первого и второ го накопителей подключены к одним входам элементов И соответственно третьей и четвертой групп, другие входы которых подключены к соответствующим выходам блока управления, выходы элементов И третьей группы подключены к одним входам элементов ИЛИ группы, другие входы которых подключены к выходам эле ментовм И четвертой группы, одни входы элементов И первой и второй групп подключены к выходам первого регистра, управляющий вход которого

подключен к соответствующему выходу блока управления, другие входы элементов И первой и второй групп подключены к соответствующим выходам блока управления, выходцы элементов ИЛИ группы подключены к информационным входам второго регистра, первый управляющий вход которого подключен к соответствующему выходу блока управления, отличающееся тем, что, с целью упрощения устройства и повышения достоверности считывания, оно содержит третий дешифратор и элемент 2И-ИЛИ, одни входы которого подключены к соответствующим выходам первого и второго дешифраторов, а другие входы - к соответствующим выходам блока управления, выход элемента 2И-ИЛИ подключен ко второму управляющему входу второго регистра, входы третьего дешифратора подключены к выходам первого регистра, выход третьего дешифратора и соответствующие выходы первого и второго дешифраторов подключены к входам блока управления.

Источники информации, принятые во внимание при экспертизе

Авторы

Даты

1982-07-07—Публикация

1980-11-19—Подача