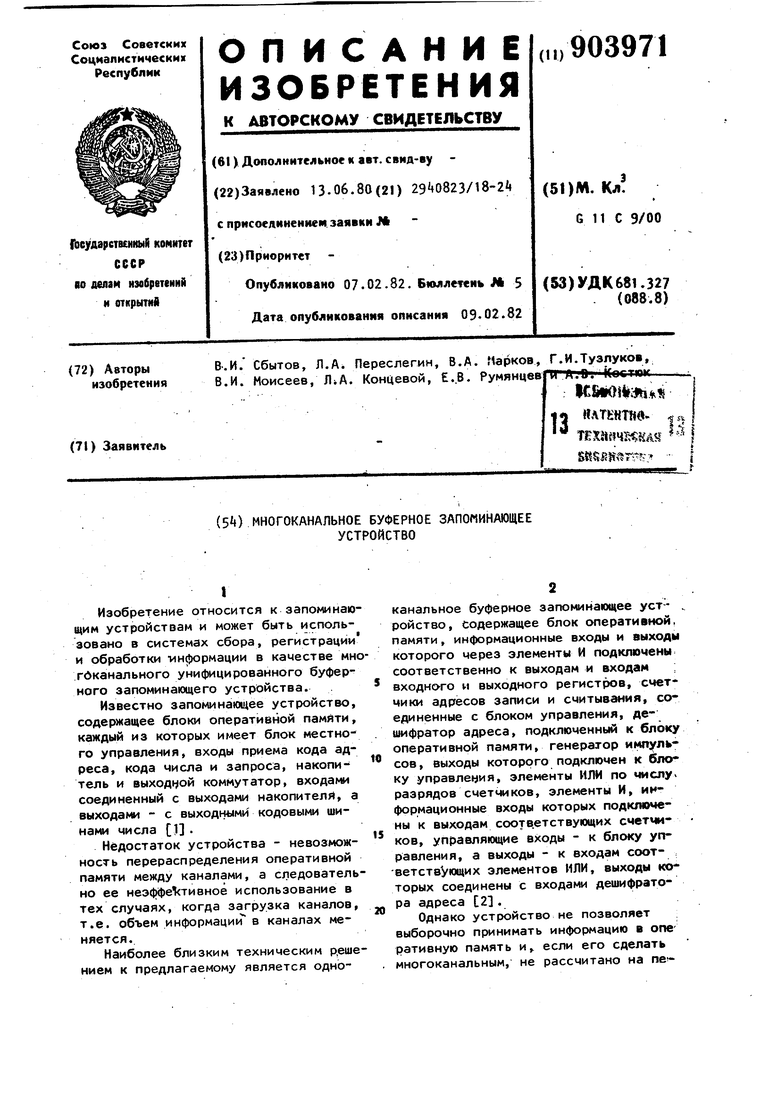

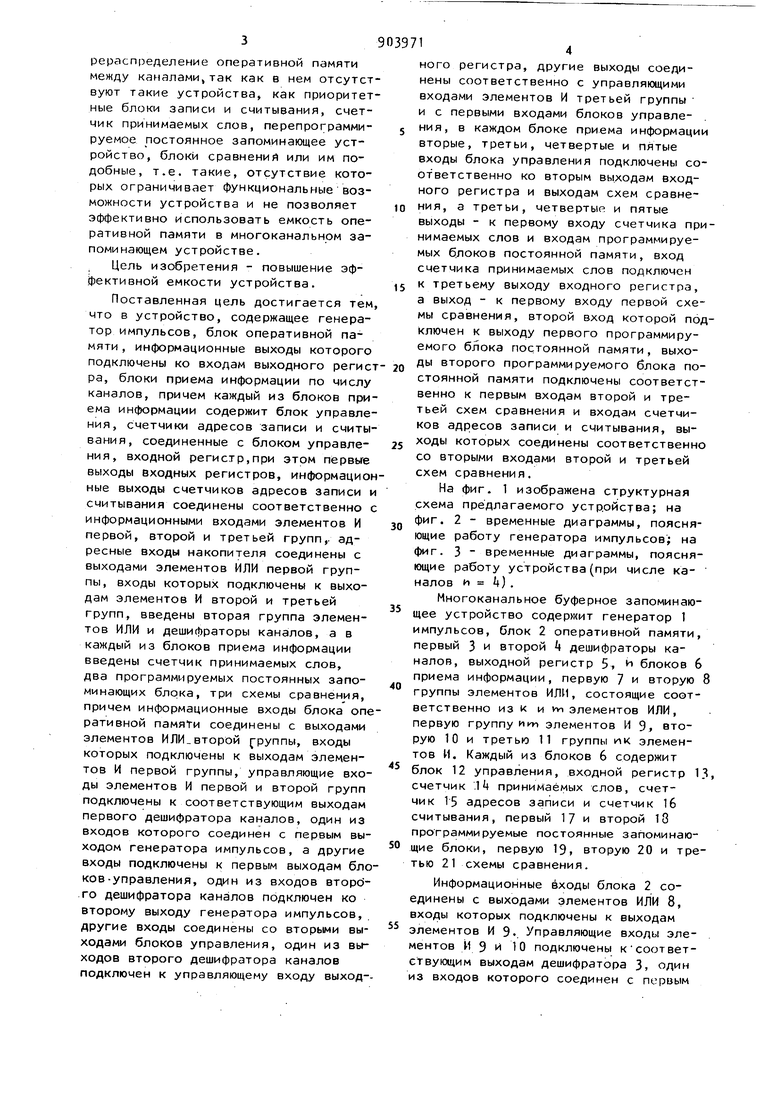

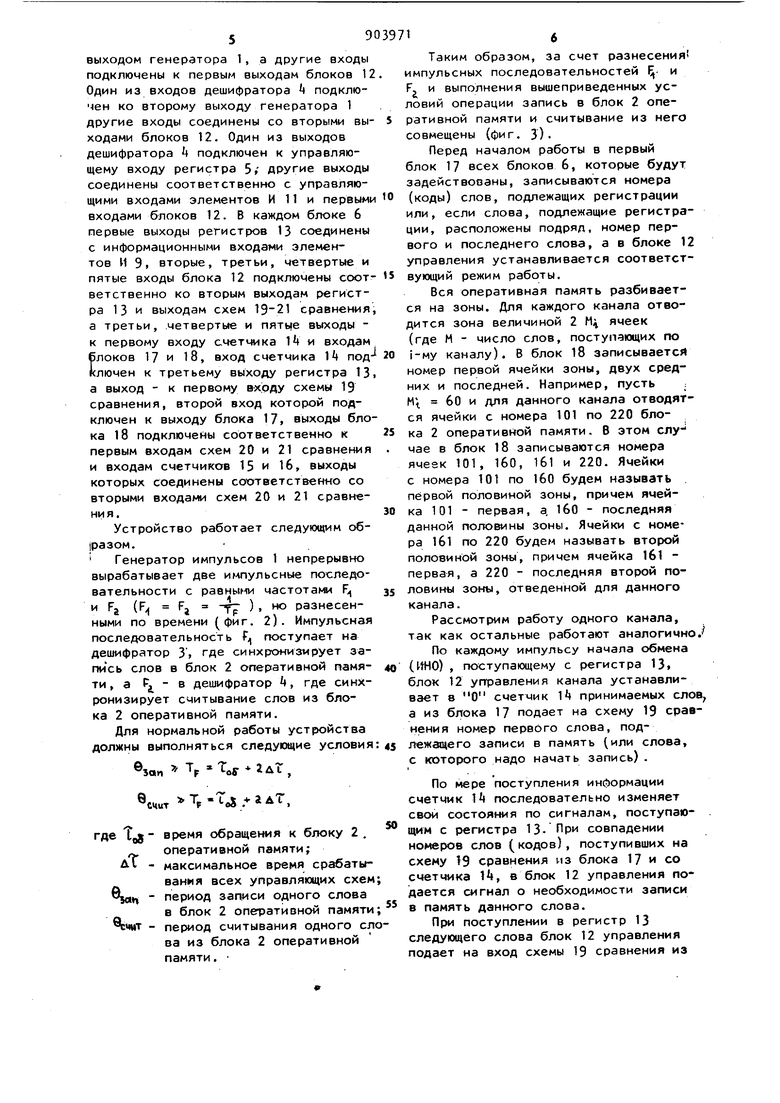

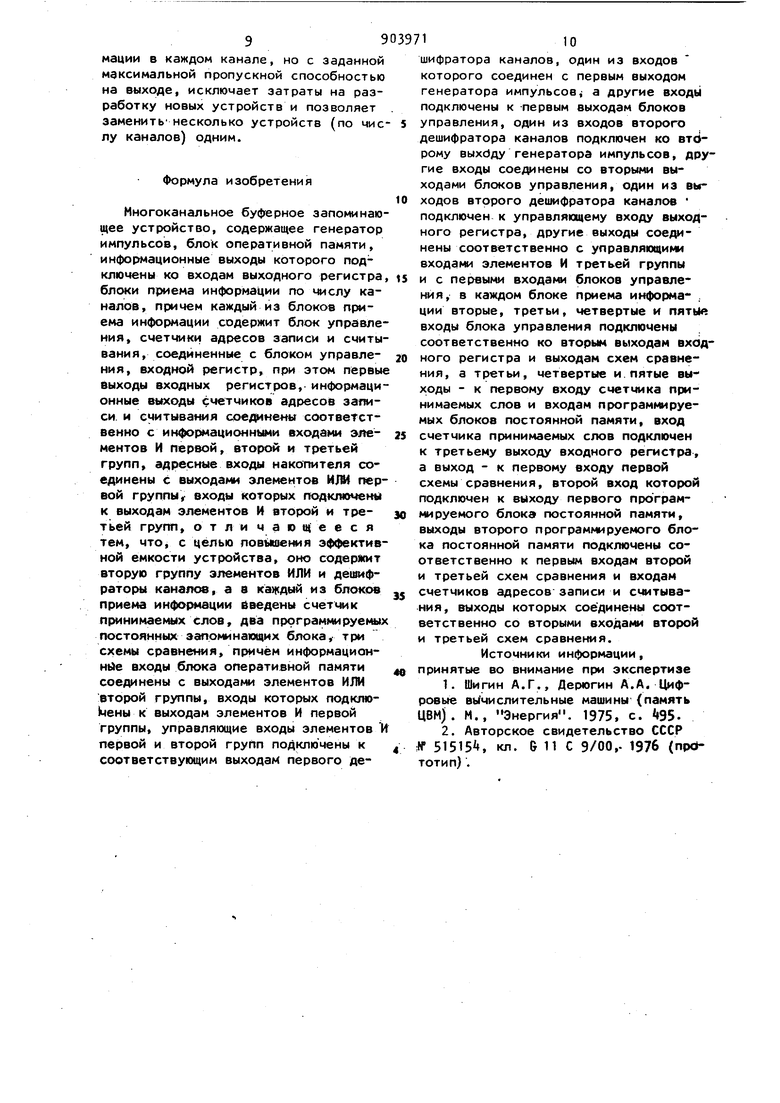

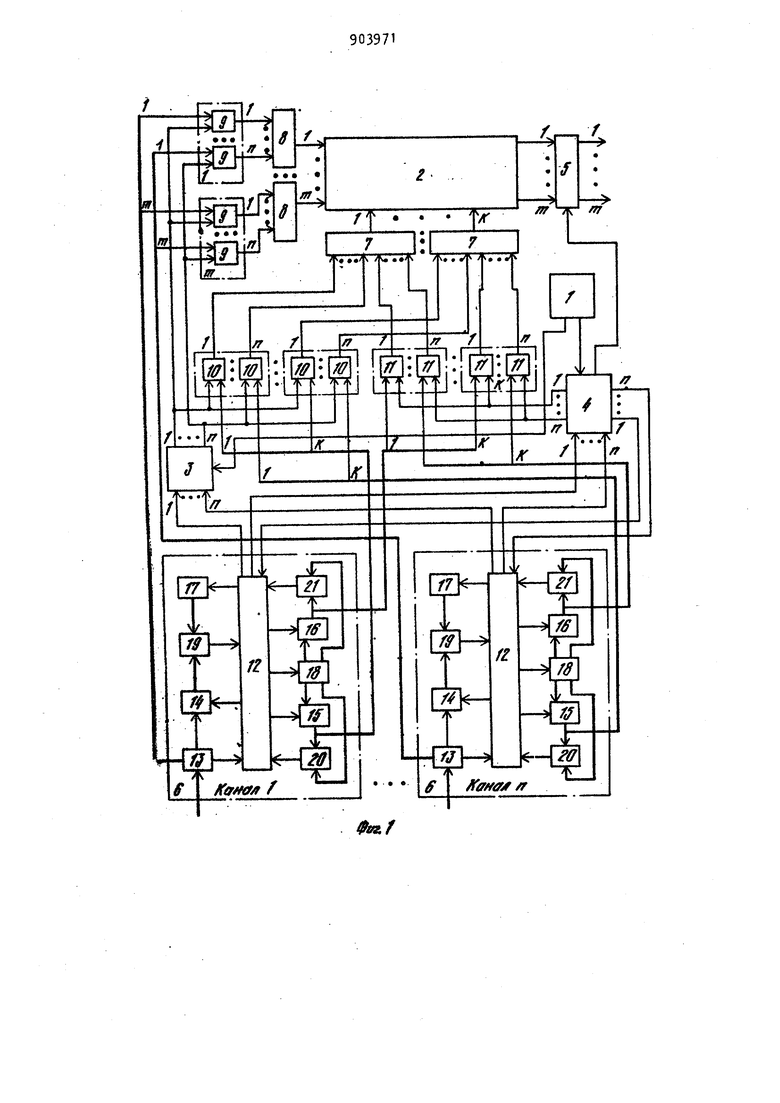

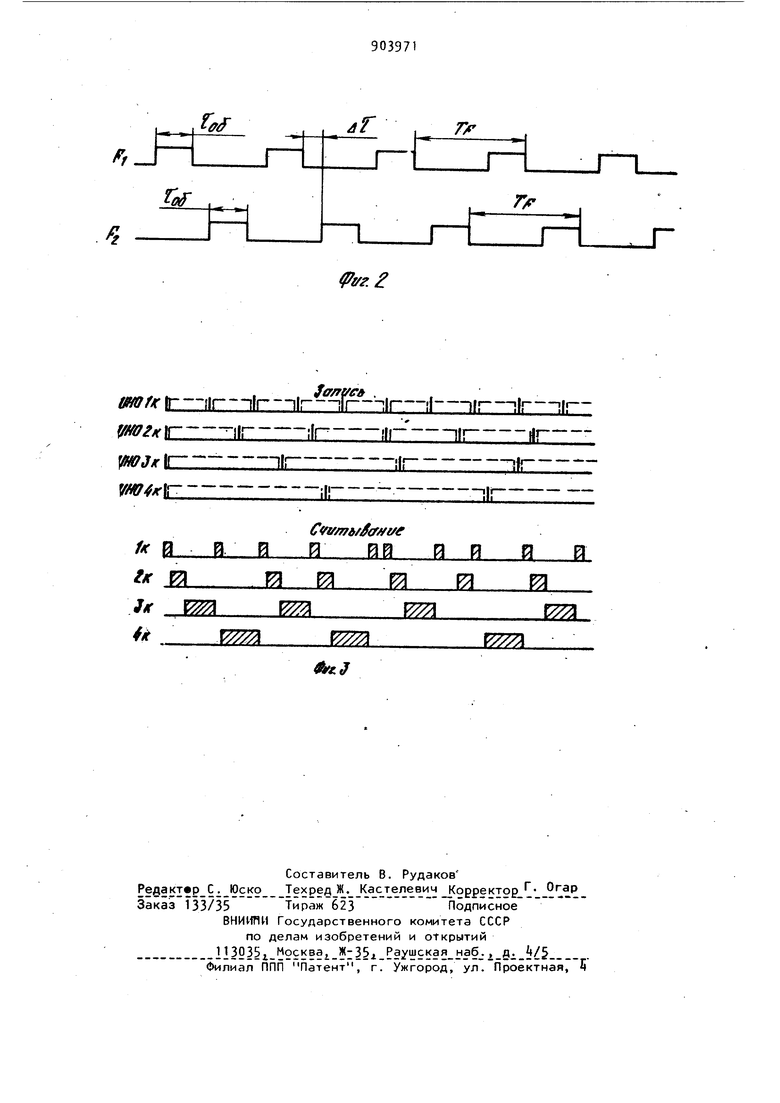

Изобретение относится к запоминающим устройствам и может быть использовано в системах сбора, регистрации и обработки н рмации в качестве мно Тдканального унифицированного буферного запоминающего устройства. . Известно запоминающее устройство, содержащее блоки оперативной памяти, каждый из которых имеет блок местного управления, входы приема кода адреса, кода числа и запроса, накопитель и выход ой коммутатор, входами соединенный с выходами накопителя, а выходами - с выходными кодовыми шинами числа СП Недостаток устройства - невозможность перераспределения оперативной памяти между каналами, а следовательно ее неэ(()фе ти8ное использование в тех случаях, когда загрузка каналов, т.е. объем информации в каналах меняется. Наиболее близким техническим решением к предлагаемому является одноканальное буферное запоминающее уст-- . ройство. Содержащее блок оперативной, памяти, информационные входы и аыходм которого через элементы И подключены соответственно к выходам и входам ; входного и выходного регистров, счетчики адресов записи и считывания, со единенные с блоком управления, дешифратор адреса, подключенный к блоку оперативной памяти, генератор импуль сов, выходы которого подключен к бло ку управле14ия, элементы ИЛИ по числу разрядов счетчиков, элементы И, информационные входы которых подключены к выходам соотв.етствующих счетчиков, управляющие входы - к блоку управления, а выходы - к входам соот- : ветствУющих элементов ИЛИ, выходы которых соединены с входами дешифратора адреса 2. Однако устройство не позволяет выборочно принимать информацию в one ративную память и, если его сделать многоканальным, не рассчитано на перерасп(зеделение оперативной памяти между каналами,так как в нем отсутствуют такие устройства, как приоритетные блоки записи и считывания, счетчик принимаемых слов, перепрограммируемое постоянное запоминающее устройство, блоки сравнений или им подобные, т.е. такие, отсутствие которых ограничивает функциональные возможности устройства и не позволяет эффективно использовать емкость оперативной памяти в многоканальном запоминающем устройстве. Цель изобретения - повышение эффективной емкости устройства. Поставленная цель достигается тем что в устройство, содержащее генератор импульсов, блок оперативной памяти , информационные выходы которого подключены ко входам выходного регист ра, блоки приема информации по числу каналов, причем каждый из блоков приема информации содержит блок управления, счетчики адресов записи и считывания, соединенные с блоком управления, входной регистр,при этом первые выходы входных регистров, информацион ные выходы счетчиков адресов записи и считывания соединены соответственно с информационными входами элементов И первой, второй и третьей групп,- адресные входы накопителя соединены с выходами элементов ИЛИ первой группы, входы которых подключены к выходам элементов И второй и третьей групп, введены вторая группа элементов ИЛИ и дешифраторы каналов, а в каждый из блоков приема информации введены счетчик принимаемых слов, два программируемых постоянных запоминающих блока, три схемы сравнения, причем информационные входы блока опе ративной памяти соединены с выходами элементов ИЛИ второй руппы, входы которых подключены к выходам элементов И первой группы, управляющие входы элементов И первой и второй групп подключены к соответствующим выходам первого дешифратора каналов, один из входов которого соединен с первым выходом генератора импульсов, а другие входы подключены к первым выходам бло ков -управления, один из входов BTOpdго дешифратора каналов подключен ко второму выходу генератора импульсов, другие входы соединены со вторыми выходами блоков управления, один из выходов второго дешифратора каналов подключен к управляющему входу выход91 ного регистра, другие выходы соединены соответственно с управляющими входами элементов И третьей группы и с первыми входами блоков управления, в каждом блоке приема информации вторые, третьи, четвертые и пятые входы блока управления подключены соответственно ко вторым выходам входного регистра и выходам схем сравнения, а третьи, четвертые и пятые выходы - к первому входу счетчика принимаемых слов и входам программируемых блоков постоянной памяти, вход счетчика принимаемых слов подключен к третьему выходу входного регистра, а выход - к первому входу первой схемы сравнения, второй вход которой подключен к выходу первого программируемого блока постоянной памяти, выходы второго программируемого блока постоянной памяти подключены соответственно к первым входам второй и третьей схем сравнения и входам счетчиков адресов записи и считывания, выходы которых соединены соответственно со вторыми входами второй и третьей схем сравнения. На фиг. 1 изображена структурная схема предлагаемого устройства; на фиг. 2 - временные диаграммы, поясняющие работу генератора импульсов; на фиг. 3 временные диаграммы, поясняющие работу устройства (при числе каналов и t) . Многоканальное буферное запоминающее устройство содержит генератор 1 импульсов, блок 2 оперативной памяти, первый 3 и второй Ц дешифраторы каналов, выходной регистр 5, блоков 6 приема информации, первую 7 и вторую 8 группы элементов ИЛИ, состоящие соответственно из к и VV1 элементов ИЛИ, первую группу ит элементов И 9, вторую 10 и третью 11 группы ик элементов И. Каждый из блоков 6 содержит блок 12 управления, входной регистр 13, счетчик k принимаемых слов, счетчик 15 адресов записи и счетчик 16 считывания, первый 1/ и второй 18 программируемые постоянные запоминающие блоки, первую 19, вторую 20 и третью 21 схемы сравнения. Информационные входы блока 2 соединены с выходами элементов ИЛИ 8, входы которых подключены к выходам элементов И 9. Управляющие входы элементов И 9 1 10 подключены ксоответствующим выходам дешифратора 3, один из входов которого соединен с первым выходом генератора 1, а другие входы подключены к первым выходам блоков 12 Один из входов дешифратора подключен ко второму выходу генератора 1 другие входы соединены со вторыми выходами блоков 12. Один из выходов дешифратора подключен к управляющему входу регистра 5, другие выходы соединены соответственно с управляющими входами элементов И 11 и первыми входами блоков 12. В каждом блоке 6 первые выходы регистров 13 соединены с информационными входами элементов И 9, вторые, третьи, четвертые и пятые входы блока 12 подключены соответственно ко вторым выходам регистра 1 3 и выходам схем сравнения, а третьи, .четвертые и пятые выходы к первому входу счетчика 1 и входам блоков 17 и 18, вход счетчика 14 подключен к третьему выходу регистра 13 а выход - к первому входу схемы 19 сравнения, второй вход которой подключен к выходу блока 17, выходы бло ка 18 подключены соответственно к первым входам схем 20 и 21 сравнения и входам счетчиков 15 и 16, выходы которых соединены соответственно со вторыми входами схем 20 и 21 сравнения. Устройство работает следую(дим об|разом. Генератор импульсов 1 непрерывно вырабатывает две иг-мпульсные последовательности с paBHMhft частотами F, paBHMhft частотами г - ) , но разнесенИ F, (F, F, ными по времени (фиг. 2). Импульсная последовательность f поступает на дешифратор 3, где синхронизирует запись слов в блок 2 оперативной памяти, а Fj - в дешифратор Ц, где синхронизирует считывание слов из блока 2 оперативной памяти. Для нормальной работы устройства должны выполняться следующие условия Т. .т„ зон F oS Tp-ieS.aAT, время обращения к блоку 2 . где 1 оперативной памяти; Д - максимальное время срабатывания всех управляющих схем в5a - период записи одного слова в блок 2 оперативной памяти период считывания одного сл ва из блока 2 оперативной памяти. Таким образом, за счет разнесения импульсных последовательностей - и F, и выполнения р, к, c,o.,,,n.., вышеприведенных условий операции запись в блок 2 оперативной памяти и считывание из него совмещены (фиг. 3). Перед началом работы в первый блок 17 всех блоков 6, которые будут задействованы, записываются номера (коды) слов, подлежащих регистрации или, если слова, подлежащие регистрации, расположены подряд, номер первого и последнего слова, а в блоке 12 управления устанавливается соответствующий режим работы. Вся оперативная память разбивается на зоны. Для каждого канала отводится зона величиной 2 М ячеек (где М - число слов, поступающих по i-му каналу). В блок 18 записывается номер первой ячейки зоны, двух средних и последней. Например, пусть ; Мг 60 и для данного канала отводятся ячейки с номера 101 по 220 блока 2 оперативной памяти. В этом случае в блок 18 записываются номера ячеек 101, 1бО, 161 и 220. Ячейки с номера 101 по 160 будем называть первой половиной зоны, причем ячейка 1Q1 - первая, а, 1бО - последняя данной половины зоны. Ячейки с номера 1б1 по 220 будем называть второй половиной зоны, причем ячейка 1б1 первая, а 220 - последняя второй половины зоны, отведенной для данного канала. Рассмотрим работу одного канала, так как остальные работают аналогично. По каждому импульсу начала обмена (1ЖО) , поступающему с регистра 13, блок 12 управления канала устанавливает в О счетчик 1 принимаемых слов, а из блока 17 подает на схему 19 сравнения номер первого слова, подлежащего записи в память (или слова, с которого надо начать запись). По мере поступления информации счетчик l последовательно изменяет свои состояния по сигналам, поступающим с регистра 13- При совпадении номеров слов (кодов), поступивших на схему 19 сравнения из блока 17 и со сметчика Н, в блок 12 управления подается сигнал о необходимости записи в память данного слова. При поступлении в регистр 13 следующего слова блок 12 управления подает на вход схемы 19 сравнения из 79 блока 17 номер следующего слова, подлежащего регистрации и т.д. до следующего ИНО (или до совпадения с номером последнего слова, подлежащего регистрации). Таким образом е каждом блоке 6 происходит селекция поступающей на запись информации в соответствии с заданной в блоке 17 программой. Запись информации в блок 2 операти ной памяти осуществляется следущим образом. По нечетным ИНО в счетчик 15 из блока 18 записывается номер (код адреса) первой ячейки первой половины зоны памяти, отведенной для данного канала, а по четным ИНО в счетчик 15 из блока 18 записывается номер (код адреса) первой ячейки второй полоёины зоны памяти. При поступлении в блок 12 управления со схемы 19 сравнения сигнала о необходимости записи в память слова, блок 12 управления дает заявку на за пись в дешифратор 3. В соответствии с приоритетом дешифратор 3 выдает сигнал разрешения записи на один из его выходов, соответствующий данному каналу. Сигнал разрешения открывает соответствукнцие k элементов И 10, ра решая поступление кода адреса записи с выходов счетчика 15 через элейенты ИЛИ 7 на адресные входы блоka 2 оперативной памяти. Одновременно этот же сигнал разрешения открыва ет элементы И 9г разрешая пьступлени информации с информационных входов регистра 13 через элементы ИЛИ 8 на вход блока 2 оперативной памяти. После записи очередного слова в счетчик 15 адреса записи каждый раз добавляется единица. После записи первого слова в одну из половин зоны при нечетном ИНО из блока 18 на первый вход схемы 20 сравнения подается нЬмер последней ячейки первой половины зоны, а при четном ИНО из блока 18 на вход схемы 20 сравнения подается номер последней ячейки второй половины-зоны. На второй вход схемы 20 сравнения подается код с выхода счетчика 15При выработке сигнала сравнения схемой 20 сравнения остается свободной одна последняя ячейка соответствующей половины зоны и, следовательно, может быть записано только одно слово информации. Если и после этого .в блок 2 управления со схемы 19 срав .нения поступает сигнал о необходимос 71 ти записи очередного слова, блок 12 управления вырабатывает сигнал переполнения, а запись в блок 2 не производится. Таким образом, схема 20 сравнения служит для защиты второй половины зоны и зон, отведенных другим каналам при сбоях счетчиков Й-, счетчиков 15 и для обнаружения ошибок в программах, когда зоны заданы неверно (перекрываются). После заполнения информацией соответствующей ПОЛУНИНЫ зоны памяти она ставится в очередь на считывание. Считывание информации из блока 2 оперативной памяти происходит следующим образом.. По нечетным ИНО в счетчик 16 из блока 18 записывается номер (код адреса) первой ячейки, а на схему 21 сравнения подается номер последней ячейки второй половины зоны памяти. отведеннои для данного канала, а по четным ИНО в счетчик 16 из блока 18 записывается номер (код адреса) первой ячейки, а на схему 21 сравнения подается номер последней ячейки первой половины зоны памяти. В соответствии с приоритетом данного канала д ешиЛратор Ц разрешает поступление сигналов считывания по одному из его и выходов в соответству1Ьщий блок 12 управления и далее на счетчик 16 считывания, который последовательно изменяет свои состоярия. Сигнал разрешения, задержанный ртносительно первого на время, необходимое для срабатывания счетчика адреса считывания, по одному изм других выходов дешифратор А поступает на соответствующие элементы И 11 и разрешает поступление кода адреса считывания с выходов счетчика 16 через элементы ИЛИ 7 на адресные входы блока 2 оперативной памяти. Одновременно с отдельного выхода дешифратора поступают импульсы записи на управляющий вход выходного регистра 5-. Считывание продолжается до выработки сигнала схемой 21 сравнения, на входы которого поступают номер последней ячейки соответствующей половины зоны памяти из блока 18 и код с выхода счетчика 16.. Использование предлагаемого устройства, как унифицированного в системах сбора, регистрации и обработки информации с различным объёмом инфор мации в каждом канале, но с заданной максимальной пропускной способностью на выходе, исключает затраты на разработку новых устройств и позволяет заменить несколько устройств (по чис лу каналов) одним. Формула изобретения Многоканальное буферное запоминающее устройство, содержащее генератор импульсов, блок оперативной памяти, информационные выходы которого подключены ко входам выходного регистра блсжи приема информации по числу каналов, причем каждый из блоков приема информации содержит блок управления, счетчики адресов записи и считывания, соединенные с блоком управления, входной регистр, при этом первые выходы входных регистров, информационные выходы счетчиков адресов записи, и считывания соедане чы соответственно с информационнъми входами элементов И первой, второй и третьей групп, адресные входы накопителя соединены с выходами элементов ИШ первой группы входы которых подключены к выходам элементов И второй и третьей групп, о т л и чающееся тем, что, с целью повъпоения эффективной емкости устройства, оно содержит вторую группу элементов ИЛИ и дешифраторы канатю, а в ка)|(дый из блоков приема информации введены счетчик принимаемых слов, два программируемых постоянных запоминающих блока, три схемы сравнения, причём информационHtile входы блока оперативной памяти соединены с выходами элементов ИЛИ второй группы, входы которых подклюК ены к выходам элементов И первой группы, управляющие входы элементов И первой и второй групп подключены к соответствующим выходам первого де9110 шифратора каналов, один из входов которого соединен с первым выходом генератора импульсов а другие входы подключены к первым выходам блоков управления, один из входов второго дешифратора каналов подключен ко втЬрому выхбду генератора импульсов, другие входы соединены со вторыми выходами блоков управления, один из выходов второго дешифратора каналов подключен к управляющему входу выходного регистра, другие выходы соединены соответственно с управляющими входами элементов И третьей группы и с первыми входами блоков управления, в каждом блоке приема информации вторые, третьи, четвертые и пятые входы блока управления подключены соответственно ко вторым выходам входного регистра и выходам схем сравнения, а третьи, четвертые и.пятые выходы - к первому входу счетчика принимаемых слов и входам программируемых блоков постоянной памяти, вход счетчика принимаемых слов подключен к третьему выходу входного регистра, а выход - к первому входу первой схемы сравнения, второй вход которой подключен к выходу первого программируемого блока постоянной памяти, выходы второго программируемого блока постоянной памяти подключены соответственно к первым входам второй и третьей схем сравнения и входам счетчиков адресов записи и с тывания, выходы которых соединены соответственно со вторыми входами второй и третьей схем сравнения. Источники информации, принятые во внимание при экспертизе 1.Шигин А.Г., Дерюгин А.А. Цифровые вь числительные машины (память ЦВМ). М., Энергия. 1975, с. kSS2,Авторское свидетельство СССР 51515, кл. & 11 С 9/00,. 1976 (пр тотип).

.. Л/

уг.

t±

r

г

| название | год | авторы | номер документа |

|---|---|---|---|

| Однокристальный микропроцессор | 1978 |

|

SU734695A1 |

| Устройство для сопряжения каналов ввода-вывода с оперативной памятью | 1977 |

|

SU682900A1 |

| Устройство для управления параллельным выполнением команд в электронной вычислительной машине | 1982 |

|

SU1078429A1 |

| Устройство для коммутации сообщений | 1984 |

|

SU1247879A1 |

| Устройство для сопряжения вычислительной машины с телеграфными каналами связи | 1986 |

|

SU1392571A1 |

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1278867A2 |

| Устройство буферизации команд процессора | 1983 |

|

SU1092506A1 |

| Управляющая векторная вычислительная система | 1982 |

|

SU1120340A1 |

| Селекторный канал | 1983 |

|

SU1226477A1 |

| Многоканальное измерительное устройство для цифровой фильтрации | 1985 |

|

SU1252919A1 |

/ff/rffff . , ЙУ/ГЙ111itlll - Ir-if y/g7/ rtl ill(

РИДУ Jr IIllr

ir

Cwa7b/f(

IK a Й. и H ИЙ H я я и

Hr

rilT . It rfl

Авторы

Даты

1982-02-07—Публикация

1980-06-13—Подача