1

Изобретение относится к автоматике и вычислительной технике.

Известен преобразователь частота-код, содержащий счетчик, триггеры, схемы совпадения и собирательную схему. Однако он имеет низкое быстродействие и ограниченную точность 1. Известен также преобразователь частота-код, содеращий блок выделения периода ВХОД11ОЙ частоты, выход которого подключен к входу блока измерения периода, генератор эталонной частоты, выход которого через схему совпадения, счетчик и вторую схему совпадения подключен к входу второго счетчика, триггер, через который выход блока выделения периода входной частоты нодключен к второму входу схемы совпадения, три группы схем совпадения, второй триггер, третью схему совпадения и третий триггер, через которые выход счетчика соединен с вторым входом второй схемы совнадения 2. Однако он обладает низким быстродействием и точностью, малым узким дианазоном преобразования.

Цель изобретения - повышение точности, быстродействия и расширение диапазона iiiicобразования.

Это достигается тем, что предлагаемый преобразователь снабжен двумя регистрами памяти, четырьмя элементами задержки и источником сигналов фиксированного интервала

времени, выход которого подключен к оторо.му входу третьей схемы совпадения, к входу первого регистра и через первый элемент задержки к входам первой группы схем совпадения, а через второй элемент задержки к второму входу второго счетчика, выходы которого через первую грунну схем совпадения по вторым входам соединены с входами первого регистра намятн, причем выходы блока измерения периода через вторую группу схем совпадения, второй регистр памяти и третью группу схем совпадения соединены с входами счетчика, выход которого подключен к вторым входам третьей группы схем совпадения, а вход второго регистра памяти через третий элемент задержки соединен с вторыми входами второй группы схем совпадения и через четвертый элемент задерл ки с вторым входом блока измерения периода.

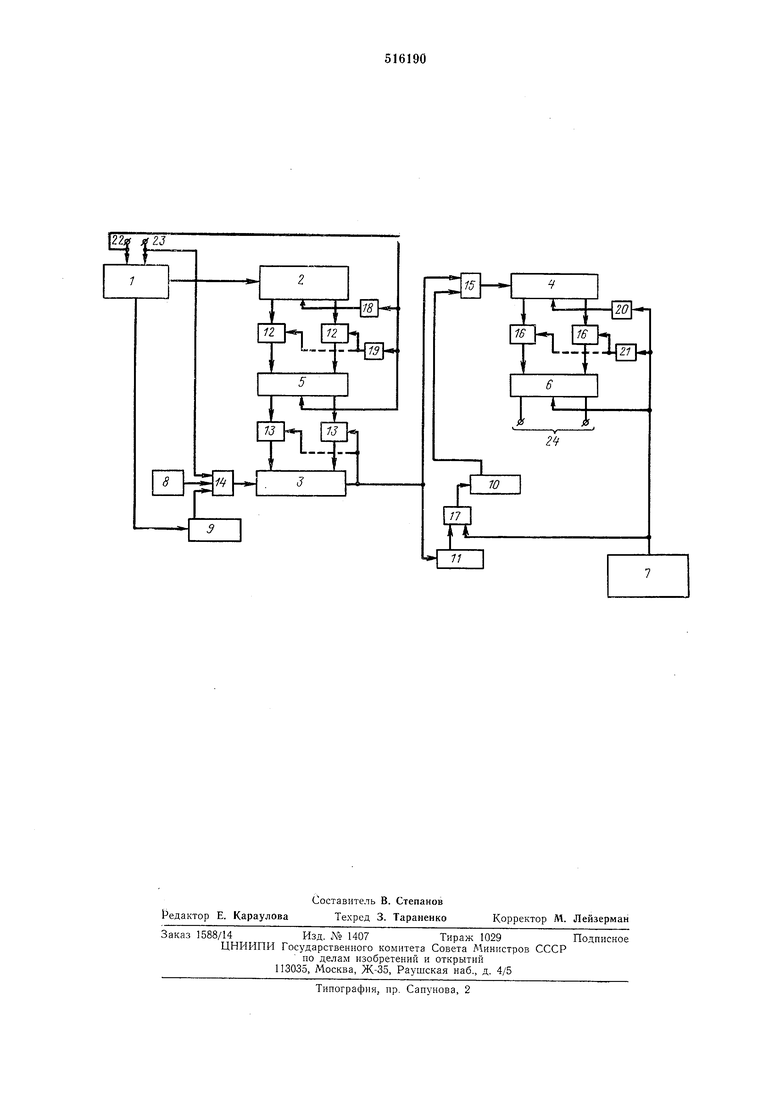

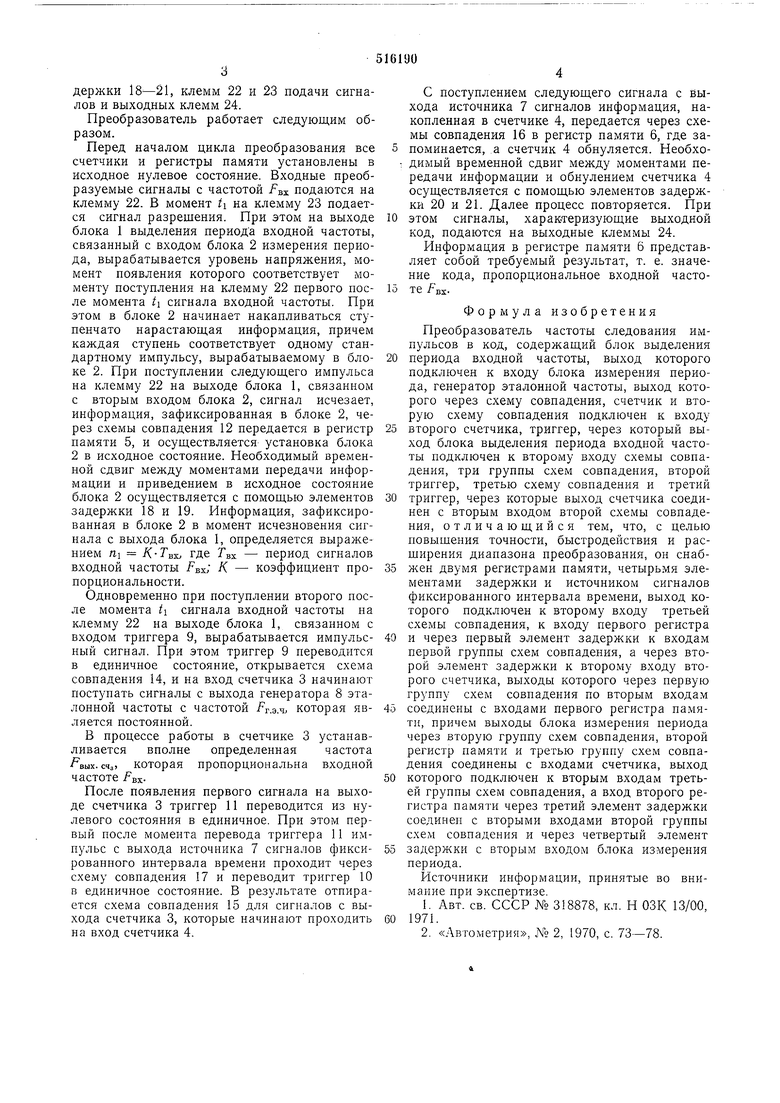

На чертеже показана функциональная схема предлагаемого преобразователя.

Преобразователь состоит из блока 1 выделения периода входной частоты, блока 2 измерения нернода, первого счетчика 3, второго счетчика 4, первого регистра памяти 5, второго регистра памяти 6, источника 7 сигналов фиксированного интервала времени генератора 8 импульсов эталонной частоты, триггеров 9-11, схем совнадения 12-17, элементов задержки , клемм 22 и 23 подачи сигналов и выходных клемм 24. Преобразователь работает следующим образом. Перед началом цикла преобразования все счетчики и регистры памяти установлены в исходное нулевое состояние. Входные преобразуемые сигналы с частотой подаются на клемму 22. В момент ti на клемму 23 подается сигнал разрешения. При этом на выходе блока 1 выделения периода входной частоты, связанный с входом блока 2 измерения периода, вырабатывается уровень напряжения, момент появления которого соответствует моменту поступления на клемму 22 первого после момента /i сигнала входной частоты. При этом в блоке 2 начинает накапливаться ступенчато нарастающая информация, причем каждая ступень соответствует одному стандартному импульсу, вырабатываемому в блоке 2. При поступлении следующего импульса на клемму 22 на выходе блока 1, связанном с вторым входом блока 2, сигнал исчезает, информация, зафиксированная в блоке 2, через схемы совпадения 12 передается в регистр памяти 5, и осуществляется установка блока 2 в исходное состояние. Необходимый временной сдвиг между моментами передачи информации и приведением в исходное состояние блока 2 осуществляется с помощью элементов задержки 18 и 19. Информация, зафиксированная в блоке 2 в момент исчезновения сигнала с выхода блока 1, определяется выражением П1 /С-Гвх, где Гвх - период сигналов входной частоты FB.; К - коэффициент пропорциональности. Одновременно при поступлении второго после момента /i сигнала входной частоты на клемму 22 на выходе блока 1, связанном с входом триггера 9, вырабатывается импульсный сигнал. При этом триггер 9 переводится в единичное состояние, открывается схема совпадения 14, и на вход счетчика 3 начинают поступать сигналы с выхода генератора 8 эталонной частоты с частотой г.э.ч которая является постоянной. В процессе работы в счетчике 3 устанавливается вполне определенная частота . счз которая пропорциональна входной частоте FBJ,. После появления первого сигнала на выходе счетчика 3 триггер 11 переводится из нулевого состояния в единичное. При этом первый после момента перевода триггера 11 импульс с выхода источника 7 сигналов фиксированного интервала времени проходит через схему совпадения 17 и переводит триггер 10 в единичное состояние. В результате отпирается схема совпадения 15 для сигналов с выхода счетчика 3, которые начинают проходить на вход счетчика 4. С поступлением следующего сигнала с выхода источника 7 сигналов информация, накопленная в счетчике 4, передается через схемы совпадения 16 в регистр памяти 6, где запоминается, ,а счетчик 4 обнуляется. Необходимый временной сдвиг между моментами передачи информации и обнулением счетчика 4 осуществляется с помощью элементов задержки 20 и 21. Далее процесс повторяется. При этом сигналы, характеризующие выходной код, подаются на выходные клеммы 24. Информация в регистре памяти 6 представляет собой требуемый результат, т. е. значение кода, пропорциональное входной частоте FES.. Формула изобретения Преобразователь частоты следования импульсов в код, содержащий блок выделения периода входной частоты, выход которого подключен к входу блока измерения периода, генератор эталонной частоты, выход которого через схему совпадения, счетчик и вторую схему совпадения подключен к входу второго счетчика, триггер, через который выход блока выделения периода входной частоты подключен к второму входу схемы совпадения, три группы схем совпадения, второй триггер, третью схему совпадения и третий триггер, через которые выход счетчика соединен с вторым входом второй схемы совпадения, отличающийся тем, что, с целью повышения точности, быстродействия и расширения диапазона преобразования, он снабжен двумя регистрами памяти, четырьмя элементами задержки и источником сигналов фиксированного интервала времени, выход которого подключен к второму входу третьей схемы совпадения, к входу первого регистра и через первый элемент задержки к входам первой группы схем совпадения, а через второй элемент задержки к второму входу второго счетчика, выходы которого через первую группу схем совпадения по вторым входам соединены с входами первого регистра памяти, причем выходы блока измерения периода через вторую группу схем совпадения, второй регистр памяти и третью группу схем совпадения соединены с входами счетчика, выход которого подключен к вторым входам третьей группы схем совпадения, а вход второго регистра памяти через третий элемепт задержки соединеп с вторыми входами второй группы схем совпадения и через четвертый элемент задержки с вторым входом блока измерения периода. Источники информации, принятые во внимание при экспертизе. 1.Авт. св. СССР № 318878, кл. Н ОЗК 13/00, 1971. 2.«Автометрия, № 2, 1970, с. 73-78.

Авторы

Даты

1976-05-30—Публикация

1974-04-04—Подача