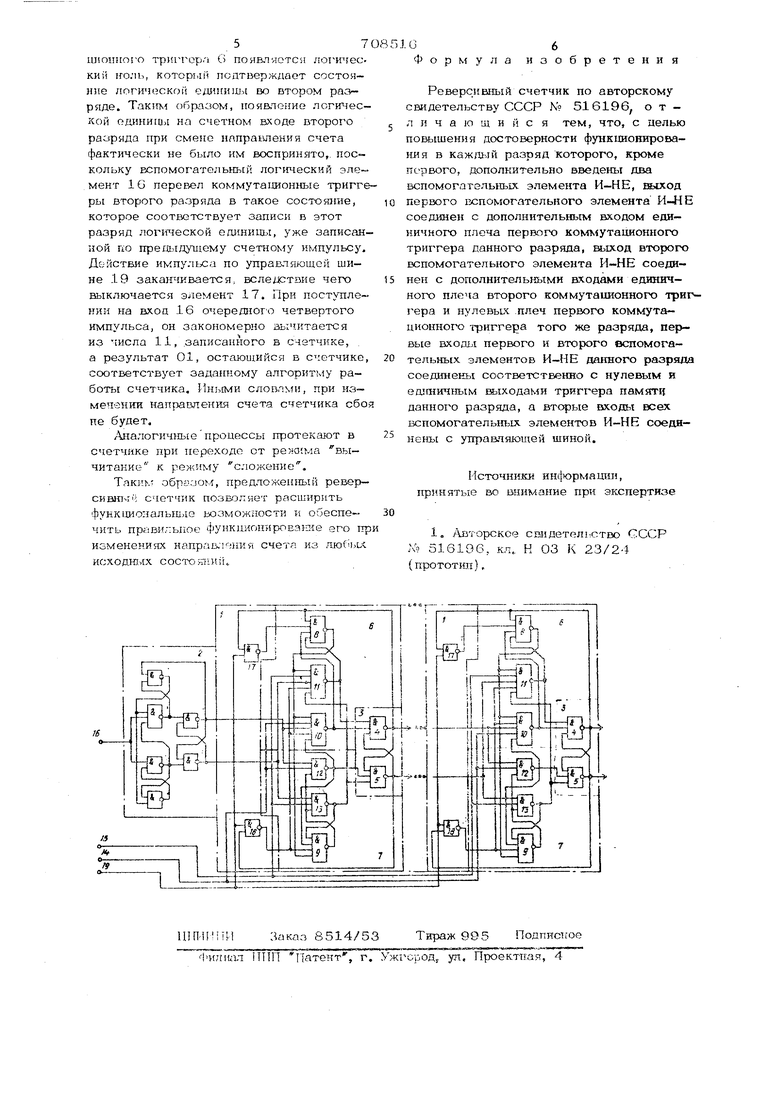

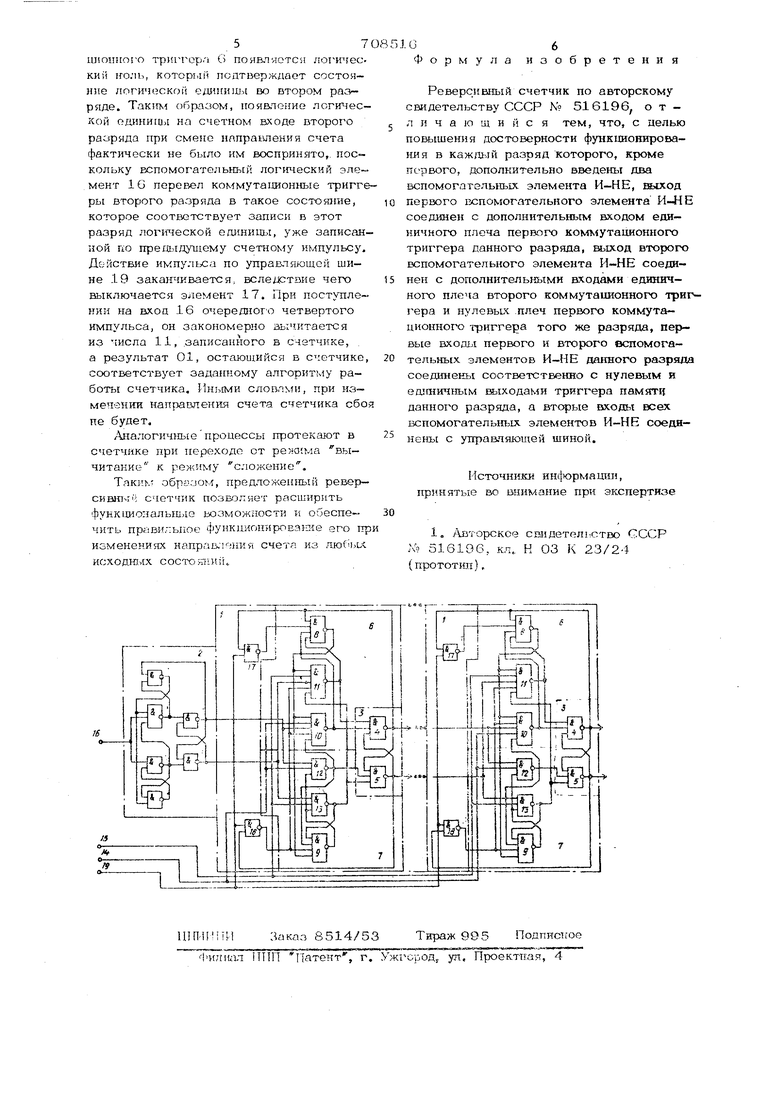

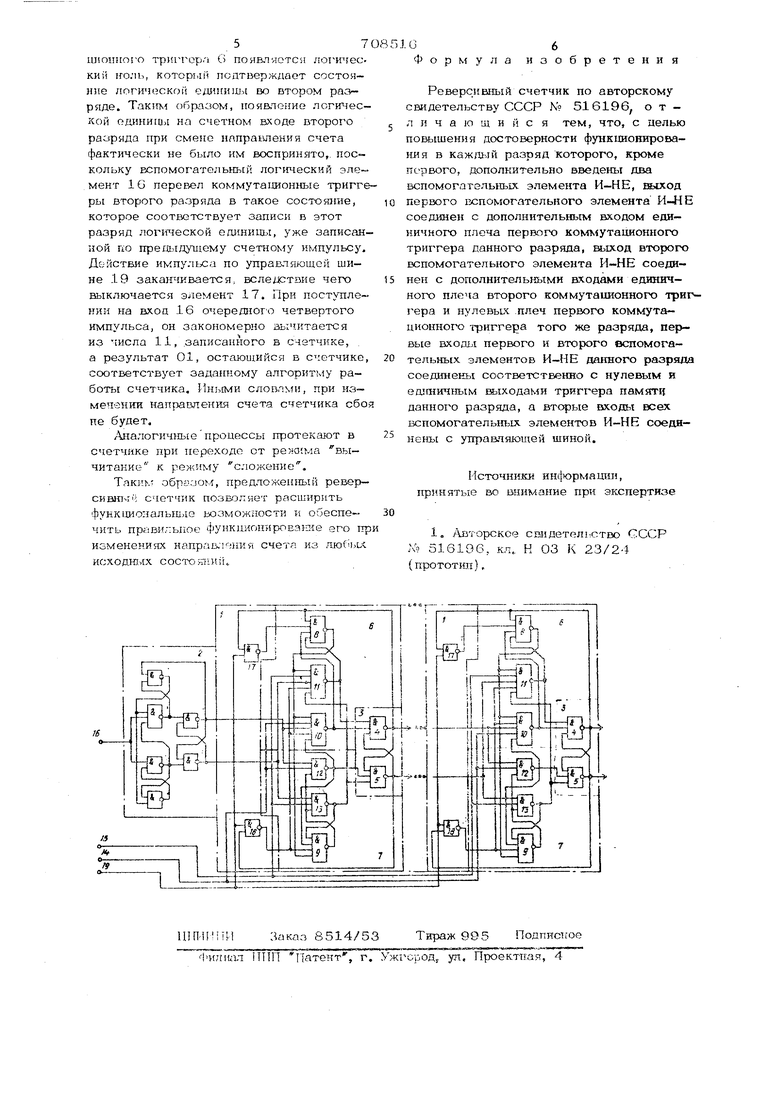

Предложение относится к области пострюения устройств вычислительной техники и дискретной автоматики на потенциальных логических элементах, . преимущественно в микроэлектронном исполнении. Известен реверсивный счетчик, кажды разряд которого, кроме первого, содержи триггер памяти на двух элементах И-НЕ и два коммутационных триггера, каждый из которых содержит один элемент И-НЕ в единичном плече и два элемента И-НЕ в нулевом плече, причем выходы нулевого плеча первого коммутационного три rfpa соединены с единичными входами триггера памяти, выходы нулевого плеча второго коммуташюнного триггера соединены с нулевыми входами триггера памяти, выход единичного плеча первог-о коммутационного триггера соединен с единичным входом второго коммутационного триггера, выходы первого и второго элементов И-НЕ нулевого плеча вто- рого коммута1шонного триггера соединены с входами соответственно первого и второго элементов И-ИВ нулевого плеча первого коммутационного триггера, дополнителыЕые входы первых элементов И-НЕ нулевых плеч коммутационных триггеров соединены с единичным выходом триггера памяти предыдущего разряда, управляющие входы элементов И-НЕ нулевых плеч коммутационных триггеров соединены с шиной вычитания, дополнительные входы вторых элементов И-НЕ нулевых плеч коммутационных триггеров соединены с нулевым выходом триггера памяти предыдущего разряда, а управляющие входы этих логических элементов соединены с шиной сложения, дополнительный вход единкчнсчо плеча первого коммутационного триггера соешшен с ед 1ничным выходом триггера памяти данного разряда, першлй разряд реверсивного счетчика содержит счетный триггер, вход которого соединен с входом реверсивного счетчика , 3 Недостатком илшрсти.го ренорсиыюго счетчика является относительно низкая достоверность функииоинроваш1я, т.к. при реверсе счетчика возможизл сбои. Целью изобретения является повышен достоверности функ1шонироБания. Это достигается тем, что в известный ревер сивный счетчик, в кажд1лй разряд, кроме первого, дополнительно введешь два вспомогательных элемента И-НЕ, выход первого вспомогательного элемента И-НЕ соединен с дoпo шитeльтlым входом елкничпого плеча первого коммутационного триггера данного разряда, выход второго вспомогательного элемента И-НЕ соединен с дополнительными входа ми единичного плеча второго коммутахш ного триггера и нулевых плеч первого коммутационного триггера того же раэряда, nepBiite входы первого и второго вспомогательных элементов И--1Ш данно разряда соединены соответственно с нулевым и единичным выходами триггера памяти данного разряда, а вторые входы всех вспомогательных элементов И-НЕ соединены с управляющей шиной. Структурная схема реверсивного счет чика показана на чертеже. Реверсивный счетчик,каждый разряд 1 которого, кром первого 2, содержит триггер 3 памяти на двух элементах 4 и 5 И-riE н два коммутационных триггера 6 и 7, кажды из которых содержит один элемент соответственно 8 и 9 И-НЕ в единичном плече и два элемента 10, 11 и 12, 13 И-НЕ в нулевом плече, причем В1,ход1л нулевого плеча первого коммутационно1Х триггера 6 соединены с единич)ыми ахо дами триггера 3 памяти, выходы нулево го плеча второго коммута1шонного триггера 7 соедине1Пз1 с нулевыми входами триггера 3 памяти, единичного пл ча первого коммуташ1онного триггера 6 соединен с единичным входом второго коммутационного триггера 7, вььходы первого 12 и второго 13 элементов И-НЕ нулевого плеча второго коммутацио ного триггера 7 соединены с входами соответственно первого 10 и второго 11 элементов И-НЕ нулевого плеча первого коммутационного триггера О, дополнительные входы первых элементов И-НЕ 10 и 12 нулевых плеч коммутационных триггеров О и 7 соединены с еданичным вьрсодом триггера 3 памят предыдущего разряда, управляющие ксоды первых элементов 1C) и 12 H-liE нулевых плеч KOMMyTainioitm.ix триггоG. ров G и 7 соештетл с шиной 14 вычитания, дополнительные вхошл вторых элементов 11 и 13 И-НЕ нулевых плеч коммута1шотпз1х триггеров G и 7 соединены с нулевым выходом триггера 3 памяти пред1)Д 1цего разряда, а управл,тю-шие входы этих логических элементов соед15нены с шиной 15 сложения, дополнительный вход единичного плеча первого коммутационного триггера 6 соединен с еш{ничшлм выходом триггера 3 памяти данного разряда, первый разряд 2реверсивного счетчика содержит счетный триггер, вход которого соединен с входом 1G реверсивного счетчика, выход первого вспомогательного элемента 17 И-НЕ каждого разряда соединен с дополнительным входом единичного плеча первого коммутационного триггера 6 данного разряда, выход второго вспомогательного элемента 1Ь И-НЕ соединен с допол1штельными входами; единичного плеча второго коммуташюнного триггера 7 и нулевых плеч первого коммутационного триггера 6 того же разряда, первые входь первого и второго вспомогательных элементов 17 и 18 И-НЕ данного разряда соединены соответственно с нулевым и единичным выходами триггера 3памяти данног о разряда, а вторые входы всех вспомог ательпых элементов И-НЕ соединены с упрашдяюшей шиной 19. Реверсивный счетчик работает следующим образом. Из исходного нулевого состош1Ия два первых разряда счетчика перекллочаются под воздействием импульсов, поступающих на вход 16, Пусть переход от режима сложения к режиму вычитания должен произойти после того, как первые два разряда достигли состояния 11, которое является наиболее не- благоприятш.1;м с точки зрения возможности возникновения сбоя. В t.-soMeHT, предшествующий изменению сигна-юв, по шииам 14 и 15 на управляющую шину 19 поступает логическая единица. Поскольку второй разряд находится в единичном состоянии, то л- гический ноль появится только на выходе вспомогательного элемента 17. Этот логический ноль вызовет появление логинеско единишл на выходе элемента 8 первого коммутационного триггера 6 и затем лоп-пеского нуля на выходе элемента 9 второт о коммутационного триггера 7. При изменепни сигналов на щинах 14 и 15, на в1-1ходе элемента 10 первого коммута

| название | год | авторы | номер документа |

|---|---|---|---|

| Реверсивный счетчик с последовательным переносом | 1974 |

|

SU516196A1 |

| Реверсивный регистр сдвига | 1971 |

|

SU474853A1 |

| Реверсивный счетчик | 1980 |

|

SU892739A1 |

| Реверсивный регистр сдвига | 1974 |

|

SU593317A1 |

| Реверсивный счетчик | 1973 |

|

SU476687A1 |

| Реверсивный счетчик импульсов | 1976 |

|

SU664300A1 |

| Реверсивный счетчик | 1985 |

|

SU1257839A1 |

| ДЕКАДНЫЙ СЧЕТЧИК | 1970 |

|

SU418981A1 |

| Реверсивное счетное устройство | 1989 |

|

SU1713100A1 |

| Реверсивный счетчик | 1973 |

|

SU458100A1 |

Авторы

Даты

1980-01-05—Публикация

1977-04-06—Подача