1

Изобретение относится к вычислительной технике.

Известны матричные накопители для запоминающего устройства, выполненные на МДП транзисторах с изменяемым пороговым напряжением. В нем ток считывания протекает через один транзистор, что обуславливает большое быстродействие к независимость тока считывания от состояния транзисторов в столбце. Однако при интегральном исполнеНИИ нельзя полезно использовать площадь между парами соседних столбцов накопителя. Наиболее близким техническим решением к изобретению является матрица накопителя запоминающего устройства на МДП-транзисторах 1 с изменяемым порогом включения, в каждом столбце которой транзисторы включены последовательно. В этой известной матрице быстродействие и ток считывания обратно пропорциональны числу транзисторов в столбце. Кроме того, величина тока считывания в ней зависит от порогового напряжения каждого из транзисторов в столбце и поэтому может значительно изменяться в зависимости от записанной информации.

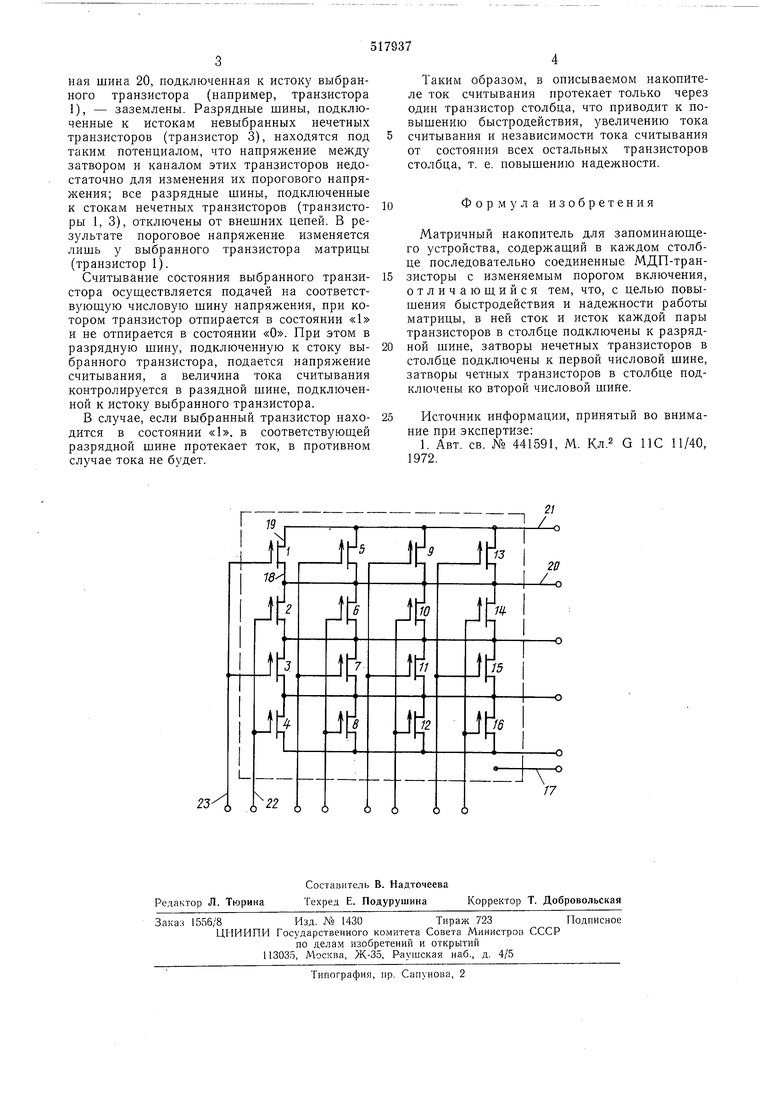

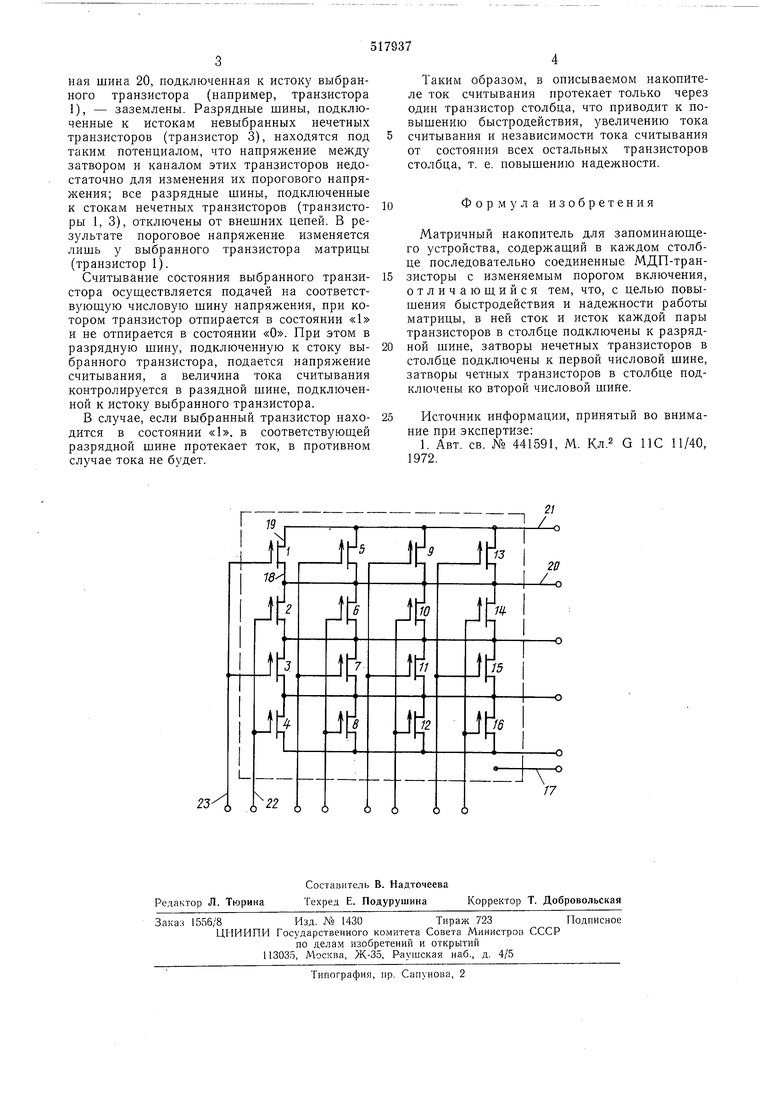

Целью изобретения является увеличение быстродействия и величины тока считывания, обеспечение независимости величины тока считывания от состояния транзисторов в столбце. В описываемом накопителе это достигается тем, что сток и исток каждой пары последовательно соединенных транзисторов в столбце подключены к разрядной шине соответствующей строки, затворы нечетных транзисторов в столбце подключены к первой числовой шине, четных - ко второй числовой шине соответствующего столбца.

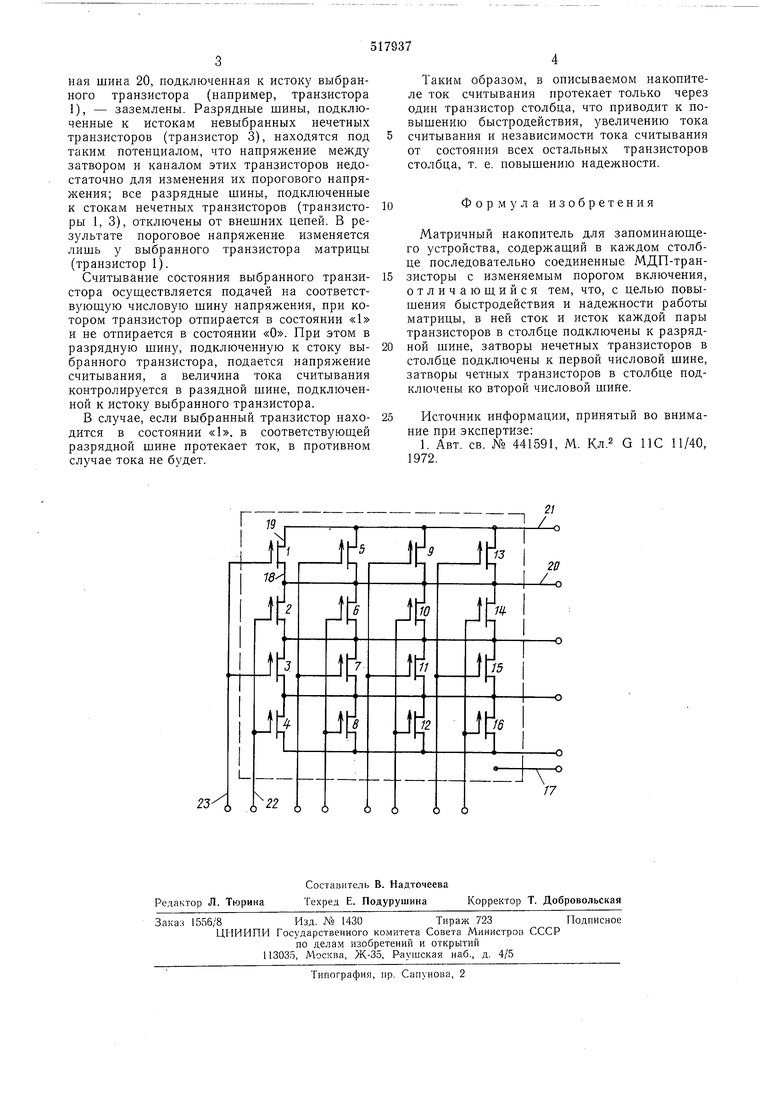

На чертеже представлена электрическая схема, описываемого накопителя и приняты обозначения: 1 -16-МДП-транзисторы с изменяемым пороговым напряжением; 17 - вывод подложки; 18 и 19 - истоки и стоки транзисторов соответственно; 20 и 21 - разрядные шины строк; 22-23 - вторые и первые числовые шины столбцов соответственно.

Информация записывается в матрицу за два цикла: в нервом цикле происходит запись состояния «1 во все транзисторы матрицы, а во втором - избирательная запись состояния «О. Запись «1 осуществляется подачей на все числовые шины импульса напряжения определенной полярности, при котором пороговые напряжения всех транзисторов становятся одинаковыми. При этом подложка 17 заземлена. Избирательная запись «О осуществляется подачей импульса противоположной полярности на выбранную числовую шину, например первую числовую шину 23 первого столба. При этом вывод подложки 17, невыбранные числовые шины 22, а также разряд

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство | 1977 |

|

SU720509A1 |

| Программируемое постоянное за-пОМиНАющЕЕ уСТРОйСТВО | 1978 |

|

SU809378A1 |

| Накопитель для полупостоянного запоминающего устройства с электрической перезаписью информации | 1973 |

|

SU519760A1 |

| Интегральное запоминающее устройство на мдп транзисторах | 1973 |

|

SU458036A1 |

| Матричный накопитель | 1981 |

|

SU1015440A1 |

| МАТРИЧНЫЙ НАКОПИТЕЛЬ НА МДП-ТРАНЗИСТОРАХ С ИЗМЕНЯЕМЫМ ПОРОГОВЫМ ВКЛЮЧЕНИЕМ | 1985 |

|

RU1378681C |

| Матричный накопитель | 1980 |

|

SU974412A1 |

| Интегральное запоминающее устройство | 1973 |

|

SU479153A1 |

| Способ записи и считывания информации в МНОП-элементе памяти,МНОП-элемент памяти и матричный накопитель для запоминающего устройства | 1983 |

|

SU1405088A1 |

| Формирователь записи-считывания для запоминающих устройств | 1978 |

|

SU765873A1 |

Авторы

Даты

1976-06-15—Публикация

1974-04-04—Подача