(54) ДЕЛИТЕЛЬ ЧАСТОТЫ С ПЕРЕМЕННЫМ КОЭФФИЦИЕНТОМ ДЕЛЕНИЯ

| название | год | авторы | номер документа |

|---|---|---|---|

| Линейный интерполятор | 1986 |

|

SU1416940A1 |

| Устройство для преобразования частоты | 1981 |

|

SU1008904A1 |

| Делитель частоты с переменным коэффициентом деления | 1976 |

|

SU657619A1 |

| Дельта-модулятор | 1988 |

|

SU1510090A2 |

| Аналого-цифровой преобразователь с цифровой коррекцией | 1982 |

|

SU1069157A1 |

| Многоканальное устройство для ввода информации | 1984 |

|

SU1265783A1 |

| Цифровой демодулятор частотно-манипулированных сигналов | 1982 |

|

SU1058083A1 |

| Делитель частоты следования импульсов с переменным коэффициентом деления | 1983 |

|

SU1092730A1 |

| Устройство для коррекции шкалы времени | 1991 |

|

SU1781669A1 |

| Делитель частоты следования импульсов с переменным коэффициентом деления | 1985 |

|

SU1292177A1 |

1

Изобретение относится к радиотехнике и может быть использовано в радиотехнических установках различного назначения, в частности в системах фазовой автоподстройки систем стабилизации дискретных частот цифровых синтезаторов частоты.

Известен делитель частоты с переменным коэффициентом деления, содержащий последовательно соединенные источник импульсов, первый делитель частоты с первым блоком д/гя установки коэффициента деления, первый элемент И, второй делитель частоты с вторым блоком для установки, первый триггер и второй элемент И, при этом выход первого делителя частоты подключен к входам второго и третьего элементов И, выход третьего элемента И соединен с управляющим входом второго блока для установки и с входом первого триггера, один из выходов которого подключен к входу первого элемента И.

Однако быстродействие известного делителя частоты ограничено временем переключения входного сигнала с входа счетчика на вход первого делителя. Это время ограничивается возможным быстродействием выходного коммутационного узла. Коммутационный узел не позволяет получить быстродейсвие делителя частоты, равное быстродействию делителя частоты с фиксированным коэффициентом деления, у которого оно максимально возможно и ограничивается лишь быстродействием одного функционально законченного элемента - триггера.

Целью изобретения является повышение быстродействия делителя.

Для этого в него введены в-торой триггер и формирователь задержки, выход которого соединен с первым управляющим входом первого делителя частоты и с управляющим входом первого блока ,цля установки, а вход - с выходом второго элемента И и с одним из входов второго триггера, один из выходов которого соединен с третьим входом второго элемента И и с вторым управляющим входом первого делителя частоты, а другой выход - с входом третьего элемента И, выход которого подключен к второму входу второго триггера.

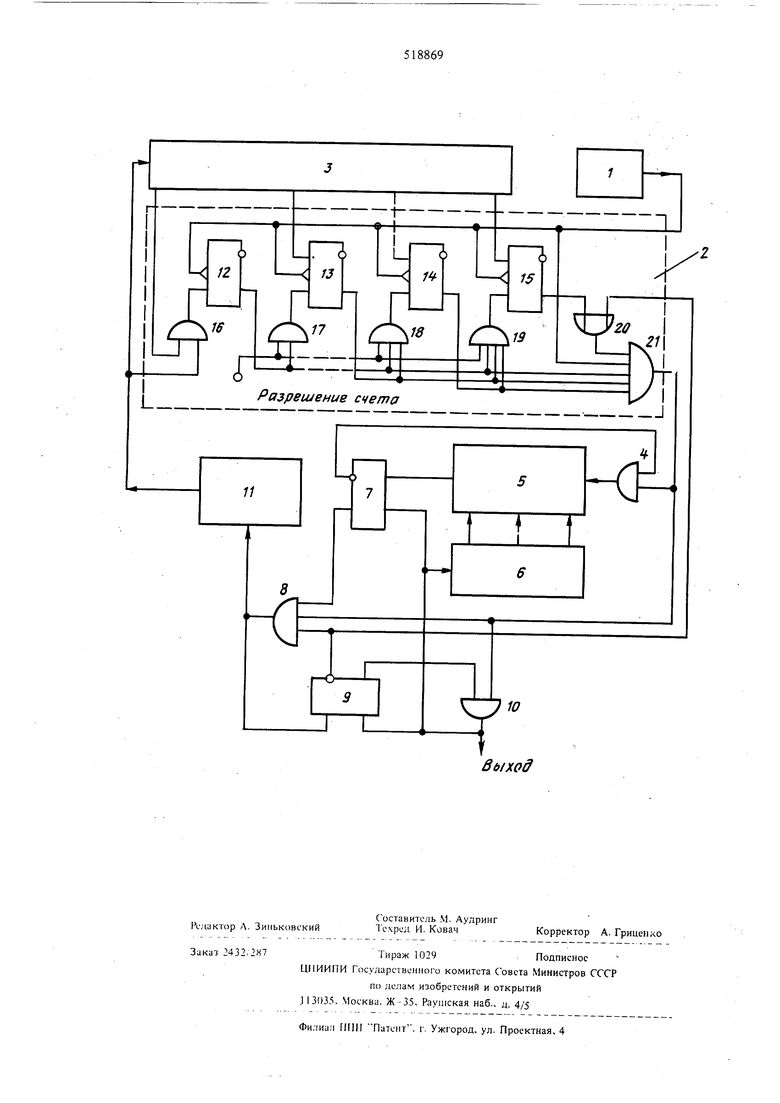

На чертеже приведена структурная электрическая схема делителя.

Делитель частоты с неременным коэффициентом деления содержит источник импульсов 1 первый делитель частоты 2 с первым блоком для установки 3, первый элемент И 4, второй делитель частоты 5 с вторым блоком )лля установки 6. первый триггер 7, второй элемент И 8, второй триггер 9. грети11 элемент И 10 и формирователь задержки И. Первы делитель частоты включает в себя (ri-tlj - разряд ный двоичный счетчик на триггерах 12 - 15 с элеме тами И 16-19, а также элемент МЛИ 20 и элемент И 21. Делитель частоты с переменным коэффициенто деления работает следующим образом. В начальный момент при помощи второго блока для установки 6 во втором делителе частоты 5 устанавливается коэффициент деления N2 равный )-2. где Npffu) целая часть частного, Nc4 / NCU - коэффициент деления первого делителя частоты и на вход первого делителя частоты 2 поступают импульсы с выхода источника импульсов 1. Первый делитель частоты 2 при этом работает в режиме постоянного коэффициента пересчета. В качестве первого делителя частоты 2 можно использовать либо двоичный счет1шк, работающий в режиме полного заполнения своих разрядов, либо двоично-десятичный, либо кольцевой или кольцевой с одной перекрестной связью. Отличие между этими счетчиками будет только в способе переключения счетчика из режима счета с коэффициентом ( в режим счета с коэффициентом N,-NJc + Nocr, (де NOCT -остаток от деления МоЬщ/Исч). Если выбран двоичный счетчик, то его выполнение может также быть различным., синхронным, со сквозным переносом, асинхронным; важно, чтобы счетчик обладал высоким быстродействием. Первый делитель частоты 2 выполнен в виде синхронного двоичного счетчика на триггерах 12-1 и элементах И 16 - 19, 21. Коэффициент пересчета задается тем, что на вход элемента ИЛИ 20 с второго управляющего вхо да счетчика, соединенного с первым выходом второго триггера 9, подается единичный потенциал. В этом случае независимо от состояния триггера 15n+i-ro разряда счетчика импульс на выходе элемента И 21 появляется только в момент, когда все предшествующие л, триггеров счетчика устанавливаются в одно; например, единичное состояние. В режиме счета с коэффициентом Мсчна выходе элемента И 16 имеется разрешающий потенциал, и триггер 12 младшего разряда счетчика работает в естественном режиме счета, т.е. изменяет свое состоя ние на обратное после каждого входного импульса. При появлении сигнала на выходе второго дели теля частоты 5, а он появляется с некоторой задержкой из-за более низкого быстродействия второго делителя частоты 5, срабатывает первый триггер 7. При этом с второго выхода первого триггера 7 запрещающий потенциал подается на второй вход первого эле мента И 4, а разрешающий потенциал с первого выхода первого триггера 7 подается на первый вход второго элемента И 8, на третьем входе которого уж имеется разрешающий потенциал с первого выхода второго триггера 9. При появлении на выходе первого делитег;/ частоты 2 очередного импульса этот импульс поступает на второй вход третьего элемента И 10, а через второй элемент И 8 проходит на вход формирователя задержки 11 и на первый вход второго триггера 9, который срабатывает по заднему фронту импульса и подает запрещающий потенциал на третий вход второго элемента И 8 и на второй управляющий вход первого делителя частоты 2. Одновременно с второго выхода второго триггера 9 разрешающий потенциал поступает на первый вход третьего элемента И 10. Формирователь задержки 11 срабатывает по заднему фронту импульса и формирует импульс, максимальная длительность которого не должна превышать полутора периодов входных колебаний. Формирователь задержки 11 может быть вьшолнен либо на триггере с элементами И, на одновибраторе или в виде дифференцирующих цепочек. Импульс с выхода формирователя задержки 11 поступает на управляющий вход первого блока для установки 3 и разрешает установку во всех разрядах счетчика, кроме первого, необходимых состояний триггеров в соответствии с требуемым коэффициентом счета N первого делителя частоты 2 в последнем цикле его работы. Кроме того, в зависимости от того, четный или нечетный коэффициент пересчета N с одного из выходов первого блока для установки 3 на один из входов элемента И 16, либо импульс подается, либо он отсутствует. Одновременно выходной импульс формирователя задержки 11 подается на первый управляю щий .вход первого делителя частоты 2. Этот управляющий вход, в случае выполнения первого делителя частоты 2 в виде двоичного счетчика, соединен с вторым входом элемента И 16. Если коэффициент N., нечетный, то на выходе элемента И 16 появляется запрещающий потенциал, который поступает на соответствующий управляющий вход первого тригге.1а и запрещает на один период входных колебаний срабатывание триггера 12 младшего разряда счетчика. При четном коэффициент М, запрещающий потенциал на выходе элемента И 16 отсутствует и триггер 12 работает в режиме естественного счета. При использовании предложенного способа записи коэффициента N, счетчик не может обеспечить счет с коэффициентом пересчета, равным единице, поскольку в этом случае необходимо за половину периода входных колебаний произвести установку в единичное состояние и первого триггера 12 счетчи1са.Это должно привести к снижению быстродействия ДПКД, что нежелательно. Поэтому в предложенном устройстве обеспечивается установка в первом делителе частоты 2 в последующем цикле его работы переменного коэффициента N, Нсч- Мост - Ne4- Г Q г (Ncy - 1). Для этой цели дополнительно введен (п + 1)-и более старший разряд счетчика, в котором также производится установка необходимого состояния в зависимости от требуемого коэффициента пересчета N и выход триггера 15 (n + l) -го разряда счетчика подключец к одному пз входов элемента И 21 через элемент ИЛИ 20, к второму входу которого подключен первый выход второго триггера 9. В начале последнего цикла работы первого делителя частоты 2 TpiirreiJ 9 с абатьгеает и на второй вхо элемента ИЛИ 20 подается нулевой потенциал, поэтому импульс на выходе элемента И 21 появляется толь ко в случае, когда все(п-И) триггеры счетчика установятся в соответствующее, например единичное состояние. Эгот импульс через элемент И 10 проходит на выход ДПКД и одновременно возвращает в первоначальное исходное состояние первый 7 и второй 9 триггеры, а также поступает на управляющий вход второго блока для установки 6 и обеспечивает установку во втором делителе частоты 5 требуемого коэффициента деления Nj. При этом первый делитель частоты 2 автоматически переходит в режим работы с коэффициентом пересчета . Формула изобретения Делитель частоты с переменным коэффициентом деления, содержащий последовательно соединенные источник импульсов, первый делитель частоты с первым блоком для установки коэффициента деления,11ервый элемент И, второй делитель частоты с вторым блоком для установки, первый триггер и второй элемент И, при этом выход первого делителя частоты подключен к входам второго и третьего элементов И, выход третьего элемента И соединен с управляющим входом второго блока для установки и с входом первого триггера, один из выходов которого подключен к входу первого элемента И, отличающийся тем, что, с целью повыщения быстродействия, в него введены второй триггер и формирователь задержки, выход которого соединен с первым управляющим входом первого делителя частоты и с управляющим входом первого блока для установки, а вход - с выходом второго элемента И и с одним из входов второго триггера, один из выходов которого соединен с третьим входом второго элемента И и с вторым управляющим входом первого делителя частоты, а другой выход - с входом третьего элемента И, выход которого подключен к второму входу второго триггера.

Авторы

Даты

1976-06-25—Публикация

1974-12-02—Подача