1

Изобретение относишся к области автоматизации контроля цифровых схем. Оно может быть иаиользовано для проверки качества (т. е. способности о биаружения заданных неисправностей) тестов при выборе системы тестов для синхронных цифровых модулей, ностроенных на интегральных схемах, а так же непосредственно для производственного контроля таких модулей с аюмощью выбранных тестов.

Известно устройство для контроля цифровых модулей и проверки качества тестов, содержащее генератор псевдослучайных последовательностей, 1генера,тор сннхронизадии, блок формирователей, блок дискриминаторов, первый блок сравнения, счетчик тактов и основной блок управления, причем первый выход основного блока управления соединен со входом генератора синхронизации и с одноименными входами генератора псевдослучайиых последовательностей, блока формирователей, блока дискриминаторов и первого блока сравнения, первый вход - с одноименным выходом блока дискриминаторов, а второй вход - с выходом первого блока сравнения, первый и второй входы которого связаны с шиной выходных сигналов эталонного модуля и вторым выходом блока дискриминаторов соответственно, второй вход блока дискриминаторов соединен с шиной выходных сигналов

контролируемого модуля, первый выход генератора синхронизации связан с вторым входом блока формирователей, второй выход - с одноименным входом генератора псеводслучайных последовательностей, выход которого соединен с третьим входом блока формирователей, выход которого соединен с шиной входных сигналов контролируемого и эталонного модулей.

Недостаток известното устройства заключается в том, что оно не позволяет осуществлять проверку контролирующих свойств используемых в качестве тестов псевдослучайных последовательностей и поэтому никогда заранее неизвестно, насколько полный контроль они обеспечивают. Это создает опасность пропуска многих неисправностей у контролируемых модулей. Отсутствие данных о том, KaiKHe именно неисправности каждого ковкретного модуля обнаруживает та или иная псевдослучайная последовательность, делает невозможным их целенаправленный отбор для получения полной системы тестов для контролируемых модулей.

Целью изобретения является расширение функциональных возможностей устройства обе опечивающего наряду с производственным контролем цифровых (преимущественно синхронных) модулей нроверку качества вырабатываемых, им псевдослучайных тестов для

каждого типа модуля на любом, заведомо исправном его экземпляре.

Сущлость изобретения заключается в том, что в предлагаемое устройство дополнительно введены контактный блок, блоК усилителей, сменная -плата е эталонной интегральной схемой, два илштатора неиапраВностей, счетчик неисправностей, второй и третий блоки сравнения, дополнительный блок мнравления, регистр результатов и регистр длины теста, причем первый вьгход дололнительного блока управления соединен с одноименным входом регистра длины теста и третьим входом основного блока управления, второй и третий выходы - со входами счетчика неисправно-стей и регистра результата соответственно, нервый вход - с выходом второго блока сравнения и третьим (ВЫХОДОМ основното блока управления, второй вход - с первыми входами первого и второго имитаторов неисправностей и вы.ходом гсчетчика неисправностей, третий вход-с .выходом регистра результата, а четвертый вход - с выходоМ третьего блОКа сравнения, первый вход которого связан с выходом блока усилителей и вторым входом nepBOiro имитатора неисправностей, а второй вход - ic выходом второго имитатора неисправностей, второй вход которого соединен е выходОгМ эталонной схемы сменной платы, вход которой соединен с выходом первого ими1татора неиаправностей, вход блока усилителей соединен с в,ыходом контактного блока, вход которого соединен с шиной входных и выходных сигналов интегральных схем модуля, выход регистра, длины теста соедииен с первым входом второго блока сравнения, второй вход которого соединен с одноименным входом регистра длины теста и .первым выходом счетчика тактов, второй вылод и .первый вход которого связаны с четвертым входом и вторым выходом основнаго блока управления соответственно, дополнительные входы - выходы счетчика тактов, регистра длины теста, регистра результата, донол.нительногО и основного блоков управления соединены с шиной сигналов индикации и пульта, управления.

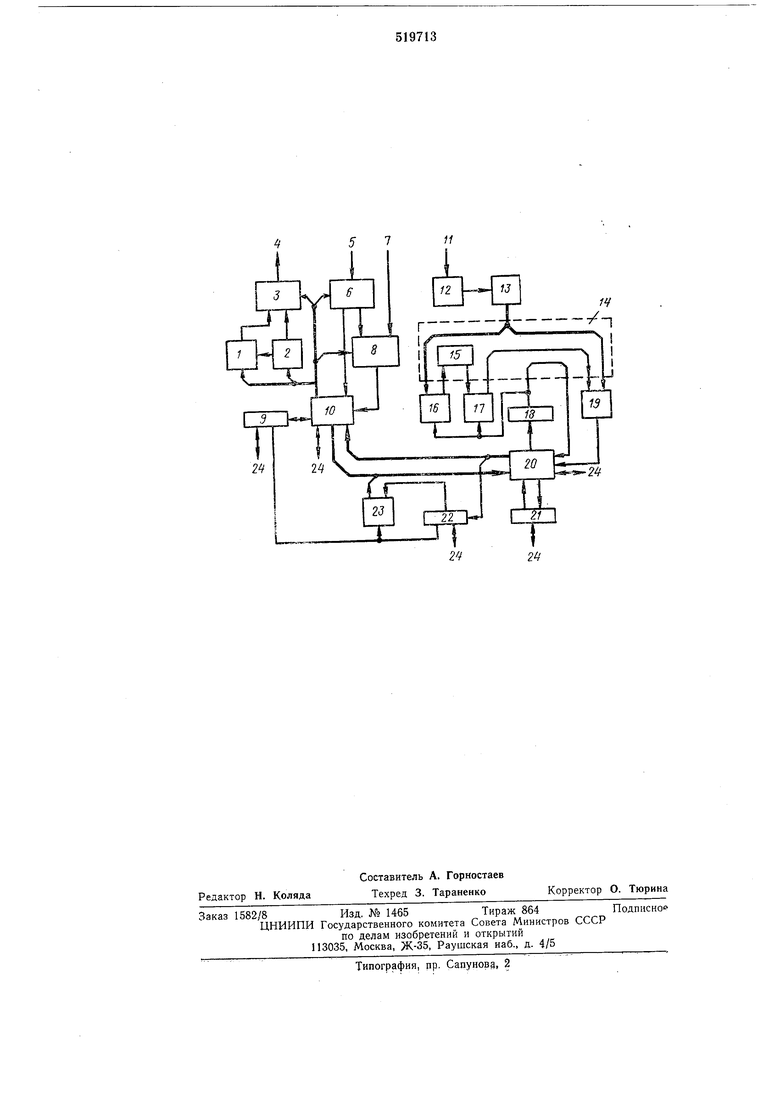

На чертеже приведена блок-схема устройства, где 1 -генератор |П€евдослучайных последовательностей, 2-генератор синхронизации, 3 - блок (форМирователей, 4 - шина входных сигналов контролируемого и эталонного модулей, 5 - шина выходных сигналов контролируемого модуля, 6 -блок диокриминаторов, 7-шина выходных сигналов эталонного модуля, 8-тервый блок сравнения, 9- счетчик тактов, 10 - основной блок управления, 1 -ши«а входных и выходных сигналов интегральных схем .модуля, 12 - контактный блок, 13 - блок усилителей, 14-сменная п:лата, 15 - эталонная интегральная схема, 16 - первый имитатор неисправностей, 17 - второй имитатор неисправностей, 18-счетчик HieHcnpaBHocTeA, 19 - третий блок сравнения, 20 - дополнительный блок управления, 21- регистр результатов, 22 - регистр длины теста, 23 - второй блок сравнения, 24 -шина сигналов шндикадии пульта управления.

Устройство работает следующим образом.

При использовании устройства в режиме контроля модулей входы контролируемого и эталонного модуля подключаются параллельно к блоку формирователей входных сигналов 3. Выходы контролируемого модуля (включая выходы всех его интегральных схем) соединяются со входами блока дискриминаторов выходных сигналов 6, а выходы эталонного модуля (также включая выходы всех его интегральных схем)-со входами первого блока сравнения 8.

После ручного запуска основного блока управления 10, этот блок приводит в исходное состояние все остальные блоки, а затем включает генераторы 1 и 2. Последовательности сигналов, вырабатываемые этими генераторами, поступают на блок формирователей входных сигналов 3, которые образуют и подают на входы контролируемого и эталонного модулей последовательность наборов потенциальных сигналов, являющихся псевдослучайным тестом. После установки на входах модулей набора потенциалов, соответствующего текущему такту теста, блок 10 увеличивает на единицу содержимое счетчика тактов 9.

Сигналы на выходах контролируемого модуля в каждом такте теста анализируются блоком дискриминаторов 6, которые определяют логическое значение сигнала на каждом выходе, а также фиксируют все случаи отклонения выходных потенциалов модуля за пределы допусков для «1 и «О. Выходные сигналы блока дискриминаторов 6, отражающие логические значения выходов модуля, сравниваются в каждом такте теста первым блоком сравнения 8 с выходными сигналами эталонного модуля. При обнаружении неравенства блок 8 выдает соответствующий сигнал в основной блок управления. 10, который выключает генераторы 1 и 2, останавливая тем самым гест, и сигнализирует (с помощью элементов индикации пульта) о неисправности контролируемого модуля. Аналогичная реакция блока 10 имеет место по сигналу блока дискриминаторов 6 при отклонении потенциала хотя бы на одном выходе модуля за пределы допусков для «1 и «О. В обоих случаях счетчик тактов 9 фиксирует номер такта теста, в котором обнаружена неисправность модуля. Состояние счетчика 9 индицируется на пульте устройства.

Проверка качества псевдослучайных тестов, получаемых с помощью генератора 1 производится на этапе выбора тестов для каждого типа модуля, подлежащего контролю на производстве, и осуществляется путем поочередной имитации всех наиболее вероятных неисправностей интегральных схем модуля.

Для каждой имитируемой неисправности проверяется, обнаруживает ее исследуемый тест или нет, и по результатам такой проверки составляются списки всех обнаруживаемых и

всех необнаруживаемых неисправностей. Эти списки и характеризуют качество теста. Если проверенный тест не обнаруживает некоторые неисправности, то на этих неисправностях испытывается другой тест, который получается изменением начального состояния или алгоритма работы генератора 1. Этот процесс продолжается до тех пор, пока не будет получен набор тестов, обнаруживающий все неисправности модуля.

Проверка качества тестов для заданного типа модуля производится на любом заведомо исправном его экземпляре.

Для подачи тестов на модуль его входы соединяются с выходами блока формирователей входных сигналов 3. Имитация неисправностей любой интегральной схемы модуля производится с помощью однотипной эталонной интегральной схемы 15, подключаемой к устройству с помощью сменной платы 14, и имитаторов 16, 17.

Работа устройства при проверке теста на неисправностях i-он интегральной схемы модуля протекает следующим образом.

После соединения контактного блока 12 с выводами i-ой интегральной схемы и подключения к устройству сменной платы, соответствующей этой схеме, производится установка всех блоков в исходное состояние и запуск дополнительного блока управления 20.

Блок 20, в свою очередь, запускает основной блок управления 10, который включает генераторы 1 и 2 и тем самым обеспечивает подачу теста па входы модуля. Начальному состоянию счетчика неисправностей 18 (все нули) соответствует режим самоконтроля устройства. В этом режиме неисправности не имитируются, и входные сигналы t-ой интегральной схемы модуля передаются имитатором 16 без каких-либо изменений яа входы эталон«ой схемы 15. Выходные сигналы схемы 15 также без изменений передаются через имитатор 17 на входы третьего блока сравнения 19, на другие входы которого поступают выходпые сигналы i-ой интегральной схемы модуля. Блок 19 производит сравнение выходных сигналов обеих схем в каждом такте текста и в случае их неравенства выдает сигнал в блок 20, который останавливает блок 10 и соответственно генераторы 1 и 2, в том такте теста, в котором обнаружено неравенство. Подобный останов в режиме самоконтроля свидетельствует о неисправности t-ой интегральной схемы модуля или самого устройства. В нормальном случае тест выполняется до конца. Конец теста фиксируется основным блоком управления 10 по номеру такта в счетчике 9. При этом блок 10 останавливает генераторы 1 и 2 и выдает соответствующий сигнал в дополнительный блок управления 20.

По этому сигналу блок 20 увеличивает на 1 содержимое счетчика неисправностей 18. Новому (отличному от нуля) состоянию счетчика соответствует заранее обусловленная неисправность, на которой должен проверяться.

тест. Далее блок 20 анализирует состояние того разряда регистра результатов 21, который соответствует данной неисправности (при начальной установке всех блоков устройства в исходное состояние в этот регистр засылается маска неисправностей интегральной схемы, задаваемая с помощью регистра переключателей пульта устройства). Если состояние этого разряда «1 (неисправность не подлежит имитации), то содержимое счетчика 18 увеличивается на 1 и анализируется следующий разряд регистра 21. Если состояние разряда «О, то с помощью имитаторов 16, 17 производится имитация неисправности, соответствующей состоянию счетчика неисправностей 18.

Например, если это состояние задает обрыв некоторого входа интегральной схемы, то соответствующий вентиль имитатора 16 отключает этот вход схемы 15 от линии, связывающей его с одноименным входом f-ой интегральной схемы модуля. Если должна имитироваться неисправность в виде постоянного значения «1 или «О некоторого выхода интегральной схемы, то соответствующий вентиль имитатора 17 отключает вход третьего блока сравнения 19 от соответствующего выхода схемы 15 и задает на этом входе фиксированное значение «1 или «О.

После окончания процессов коммутации в имитаторах 16, 17 дополнительный блок управ.пения 20 запускает блок управления 10, который обеспечивает выполнение теста. При этом сигналы, действующие в процессе выполнения теста на входах г-ой интегральной схемы модуля, подаются через имитатор 16 на входы схемы 15. Третий блок сравнения 19 сравнивает в каждом такте теста выходные сигналы этой схемы, поступающие через имитатор 17, с выходными сигналами i-ой иптегральной схемы модуля. При обнаружении неравенства также как и в режиме самоконтроля происходит останов теста. Однако в этом случае останов означает, что тест обнаружил имитируемую неисправность. Для фиксации этого факта блок 20 устанавливает в «1 соответствующий этой неисправности разряд регистра результатов 21, а также анализирует результат полученный вторым блоком сравнения 23 при сравнении номера такта, в котором обнаружена неисправность, сохраняемого в счетчике 9, с содержимым регистра длины теста 22. Если этот номер больше числа в регистре 22, то блок 20 обеспечивает его передачу в регистр 22, в противном случае состояние регистра 22 не меняется. Начальное состояние регистра 22 (после окончания режима самоконтроля) - во всех разрядах, и таким образом, данная операция позволяет зафиксировать в этом регистре наибольший для всех обнаруживаемых тестом неисправностей номер такта, на котором прерывается тест. Иными словами, после проверки всех неисправностей г-ой интегральной схемы - регистр 22 указывает минимальную длину начального участка теста.

достаточного для обнаружения всех обнарул иваемых тестом неисправностей этой схемы.

Если имитируемая неисправность не обнаруживается, то тест выполняется до конца. После этого, либо после окончания операции с регистрами 21 и 22 (в случае обнаружения неисправности) дополнительный блок управления 20 анализирует поступающие в него через сменную плату 14 выходы счетчика неисправностей 18 для того, чтобы проверить, исчерпаны или нет все неисправности, которые имитироваться для t-ой интегральной схемы. Если все неисправности исчерпаны, то происходит останов устройства. В противном случае описанный выше процесс повторяется, начиная с момента увеличения содержимого счетчика 18 на 1.

Останов устройства после окончания проверки теста на всех заданных неисправностях г-ой интегральной схемы модуля сопровождается соответствующей сигнализацией на пульте. Элементы индикации пульта, связанные с регистром результатов 21, указывают все обнаруженные и необнаруженные неисправности этой схемы (т. е. характеризуют качество теста по отношению к данным неисправностям), а элементы индикации регистра 22 указывают минимальную длину теста.

Формула изобретеиия

Устройство для контроля цифровых модулей и проверки качества тестов, содержащее генератор псевдослучайных последовательностей, генератор синхронизации, блок формирователей, блок дискриминаторов, первый блок сравнения, счетчик тактов и основной блок управления, причем первый выход основного блока управления соединен со входом генератора синхронизации и с одноименными входами генератора псевдослучайных последовательностей, блока формирователей, блока дискриминаторов и первого блока сравнения, первый вход - с одноименным выходом блока дискриминаторов, а второй вход - с выходом первого блока сравнения, первый и второй входы которого связаны с шиной выходных сигналов эталонного модуля и вторым выходом блока дискриминаторов соответственно, второй вход блока дискриминаторов соединен с шиной выходных сигналов контролируемого

модуля, первый выход генератора синхронизации связан со вторым входом блока формирователей, второй выход - с одноименным входом генератора псевдослучайных последовательностей, выход которого соединен с третьим входом блока формирователей, выход которого связан с шиной входных сигналов контролируемого и эталонного модулей, о тличающееся тем, что, с целью расширения функциональных возможностей, в устройство дополнительно введены контактный блок, блок усилителей, сменная плата с эталонной интегральной схемой, два имитатора неисправностей, счетчик неисправностей, второй и третий блоки сравнения, регистр длины теста, регистр результата и дополнительный блок управления, причем первый выход дополнительного блока управления соединен с одноименным входом регистра длины теста и третьим входом основного блока управления, второй и третий выходы - со входами счетчика неисправностей и регистра результата соответственно, первый вход - с выходом второго блока сравнения и третьим выходом основного блока управления, второй первыми входами первого и второго имитаторов неисправностей и выходом счетчика неисправностей, третий вход - с выходом регистра результата, а четвертый вход - с выходом третьего блока сравнения, первый вход которого связан с выходом блока усилителей и вторым входом первого имитатора неисправностей, а второй вход - с выходом второго имитатора неисправностей, второй вход которого соединен с выходом эталонной схемы сменной платы, вход которой соединен с выходом первого имитатора неисправностей, вход блока усилителей соединен с выходом контактного блока, вход которого соединен с шиной входных и выходных сигналов интегральных схем модуля, выход регистра длины теста соединен с первым входом второго блока сравнения, второй вход которого соединен с одноименным входом регистра длины теста и первым выходом счетчика тактов, второй вход и первый вход которого соединены с четвертым входом и вторым выходом основного блока управления соответственно, дополнительные входы - выходы счетчика тактов, регистра длины теста, регистра результата, дополнительного и основного блоков управления соединены с шиной сигналов индикации и пульта управления.

:;j щи.

г/у

2

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля цифровых блоков | 1981 |

|

SU1037259A1 |

| Устройство для синтеза тестов | 1980 |

|

SU886003A1 |

| Устройство для формирования тестов | 1974 |

|

SU477413A1 |

| Устройство для автоматического контроля цифровых объектов | 1977 |

|

SU656063A1 |

| Устройство для контроля цифровых блоков | 1986 |

|

SU1383368A1 |

| Устройство для контроля цифровых блоков | 1982 |

|

SU1037261A1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ И ВОССТАНОВЛЕНИЯ ТЕХНИЧЕСКИХ СРЕДСТВ МЕДИЦИНСКОГО НАЗНАЧЕНИЯ | 1992 |

|

RU2072788C1 |

| Устройство для контроля цифровых объектов | 1974 |

|

SU546888A1 |

| Устройство для задания тестов | 1983 |

|

SU1168951A1 |

| Сигнатурный анализатор | 1989 |

|

SU1756890A1 |

Авторы

Даты

1976-06-30—Публикация

1974-02-21—Подача