(54) УСТРОЙСТВО ДЛЯ СИНТЕЗА ТЕСТОВ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля цифровых блоков | 1981 |

|

SU1037259A1 |

| Устройство для контроля цифровых модулей и проверки качества тестов | 1974 |

|

SU519713A1 |

| Устройство для контроля цифровых узлов | 1981 |

|

SU1012263A1 |

| Устройство для контроля неисправностей интегральных схем | 1980 |

|

SU1083138A1 |

| Устройство для имитации неисправностей | 1987 |

|

SU1444775A1 |

| Устройство для контроля неисправностей интегральных схем | 1974 |

|

SU528517A1 |

| Устройство для сопряжения вычислительного комплекса накопителей на магнитной ленте | 1983 |

|

SU1142839A1 |

| Устройство для контроля цифровых блоков | 1982 |

|

SU1037261A1 |

| Тренажер оператора радиоэлектронной аппаратуры | 1989 |

|

SU1658193A1 |

| Устройство для диагностики блоков электронных вычислительных машин | 1978 |

|

SU746556A1 |

I

Изобретение относится к вычислительной технике.

Известны устройства, позволякщие генерировать проверяющие тесты для дискретных схем по их математическим моделям и моделям неисправностей ti3

В силу неадекватности схемы и модели, имеияцей место в ряде случаев, синтезированные таким образом тесты являются, фактически, тестами для модели и не всегда тестами дпя самой схемы Это составляет принципиальный недостаток таких устройств. Преодолеть указанную трудность можно путем синтеза геста по типовому заведомо исправному модулю. Однако такие устройства этого не позволяют.

Наиболее близким техническим решением к предлагаемому является устройство, с помощью которого тест синтезируют по физическому модулю имитацией неисправностей в .интегральных схемах 2.

Однако указанным устройством не гарантируется полнота синтезированного теста синтез теста занимает чрезвычайно много BpeMeHHi синтезированный тест оказывается излишне длинным.

Первый недостаток объясняется тем, что сравнение сигналов исправного модуля с имитируемыми неисправностями в блоке сравнения осуществляется на уровне интегральных схем, а на уров10не модулей (навыходах интегральных схем, а не на выходах модулей интегральных схем), и, таким образом, не гарантируется транспортировка неисправностей на фиксированном входном

15 наборе к выходам модуля. Это ведет к тому, что тест, полученный без учета возможности транспортировки неисправности, многие неисправности не обнаруживает. Второй недостаток

20 обусловлен тем, что для многовходовых модулей, содержащих элементы шестого и более высокого рангов, генерация тестов на случайных набо3pax оказывается неэффективной. Трети недостаток объясняется отсутствием возможности оптимизации теста при помощи функциональных блоков устройства. Цель изобретения - увеличение пол . ноты контроля. Для достижения поставленной цели в устройство для синтеза тестов, содержащее блок управления, блок управ ления имитацией неисправностей, имитатор неисправностей,формирователь сигналов, генератор псевдослучайных последовательностей, синхронизатор, блок дискриминаторов, блок сравнения регистр результата, первый блок усийителей, счетчик неисправностей, при чем выход формирователя сигналов неисправностей является первым выходом устройства, первый вход формирователей сигналов подключен к выходу генератора псевдослучайных последовательностей, первый вход которого сое динен с первым выходом синхронизатора, второй выход которого подключен ко второму входу формирователя сигналов, третий вход которого соединен с первым управляющим выходом блока управления, второй, третий, четвертый и пятый управляющие выходы которого подключены соответственно к первому входу синхронизатора, объединенного со вторьм входом генератора псевдослучайных последовательностей, к nepJBOMy входу блока дискриминаторов, к первому входу блока сравнения и ко входу запуска блока управления имитацией неисправностей, первый вход блока управления подключеп к первому выходу блока дискриминаторов второй выход которого соединен со вторым входом блока сравнения, третий вход которого является входом сигнала эталона устройства, сигнальный вход блока дискриминаторов является вторым входом устройства, импульсный вход блока управления объединен со входом запуска блока управления имитацией неисправностей, первый вход запуска блока управления подключен к первому выходу счетчика неисправностей, вход которого подключен к первому входу имитатора неисправностей и к выходу блока управления имитацией неисправностей, второй выход счетчика неисправностей подключен ко второму входу имитатора неисправностей, .третий вход которого подключен к выходу первого блока усилителей, пер3вый выход имитатора неисправностей подключен к первому входу блока управления имитацией неисправностей, четвертый вход которого соединен с первой группой входов регистра результатов, введены Логический блок, первый и второй входы которого подключены соответственно к пятому и шестому управляющим выходам блока управления, вход запуска которого подключен к первому выходу логического блока, второй выход которого подключен к группе входоЬ регистра результатов, вторая rgynna выходов которого соединена с третьим входом логического блока, четвертый вход которого соединен с выходом блока сравнения, входы второго блока усилителей подключены к группе выходов имитатора неисправностей, выход второго блока усилителей соединен со входом первого блока усилителей и .является входом-выходом устройства. Блок управления содержит дешифратор, элемент задержки,генератор импульсов, счетчик и регистр, причем выходы дешифратора являются управляющими выходами блока, группа входов дешифратора сое динена с группой выходов счетчика, первый вход которого -является вторым входом запуска блока, второй и третий входы счетчика подключены соответственно к выходу элемента задержки и к. выходу генератора импульсов, вход элемента задержки является первым входом блока, первый вход генератора импульсов является первым входом запуска блока, второй вход генератора импульсов является импульсным входом блока, группа выходов регистра подключена к группе входов счетчика, . Кроме того, логический блок содержит регистр сдвига, эл1ементы И, группу элементов И, элемент ИЛИ и счетчик, причем лервый вход элемента И объединен с тактовым входом регистра сдвига и является первым входом блока,- второй вход элемента И является четвертым входом блока, выход элемен-, та И подключен к сдвигающему входу регистра сдвига, первая выходов регистра сдвига подключена к первой группе входов элементов И группы и является вторым входом блока, вторая группа входов элементов И группы является вторыми входами блока, третьим входом блока, выход каждого элемента И группы подключен к группе входов

сЧетчнка, группа выходов которого подключена к группе входов элемента ИЛИ, выход которого является первым выходом блока.

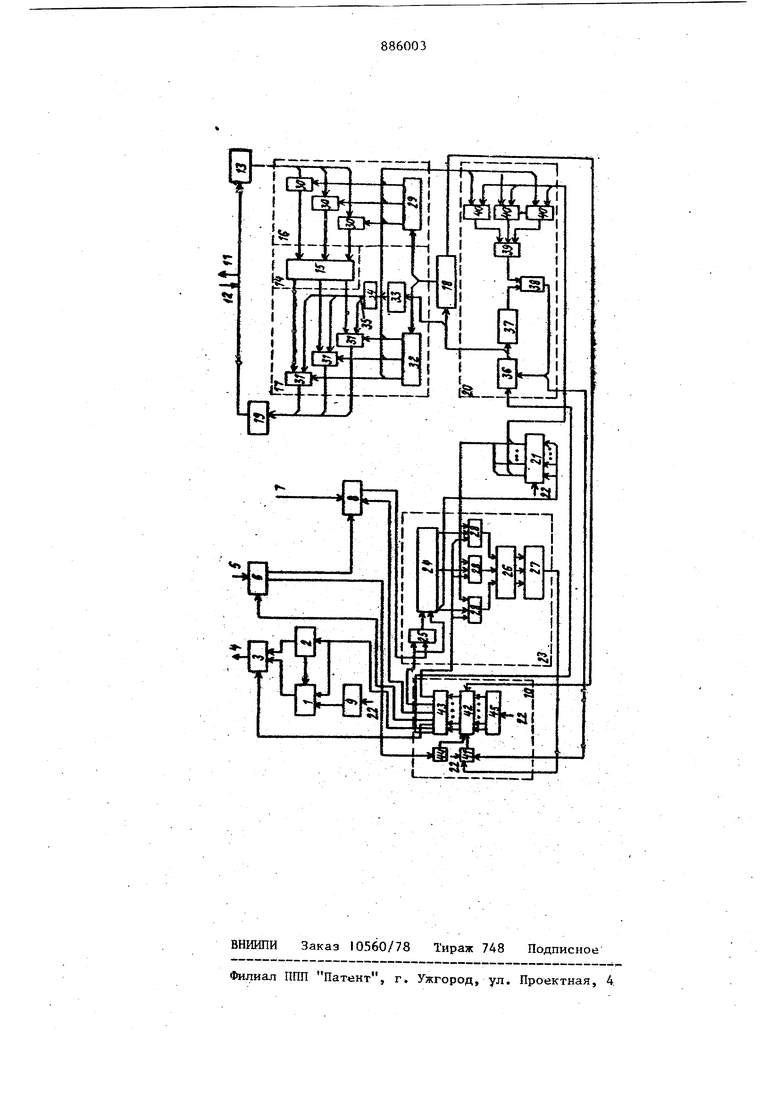

На чертеже изображена структурная схема предлагаемого устройства.

Устройство включает генератор 1 псевдослучайных последовательностей, синхронизатор 2, формирователь .3 сигналов (неисправности}, вход А сигналов модуля, в котором имитируется неисправность, и эталонного модуля, выход 5 сигналов модуля с имитируемой неисправность блок 6 дискриминаторов, выход 7 сигналов эталонного модуля, блок 8 сравнеиися, . регистр 9 маски, биок 10 уп1 авления, вход М сигналов интегральных схем модуля, выход 12 сигналову первый блок 13 усилителей, сменную плату 14, интегральную схему 15, в кото- / рой имитируются неисправности, йер вый имитатор 6 неисправностей вто рой имитатор 17 неиспраднсгетей счетчик 18 неисправностей, второй блок 19 усилителей, блок 20 уиравле-ния имитацией неисправностей, регистр 21 результатов входы 22 nyjibта управления, логический блок 23 регистр 24 сдвига, элемент И 25, счетчик 26, элемент ИЛИ 27, группу . элементов И 28, дешифратор 29, элементы И 30, управлянщие ключи 31, второй 32, триггер 33 ей счетньм входом,, управляемый ключ 34, вход 35 констаитньк неисправностей, генератор 36 импульсов, элемент 37 задержки, элемент И-НЕ 38, элемент ИЛИ 39, элементы И 40, генератор 41 :импульсов, счетчик 42, дешифратор 43, элемент 44 задержки, регистр 45, Второй блЬк 19 усилителей предназначен для приведения сигналов, поступающих со второго имитатора 17 неисправностей, к ста ндарТному виду. Он выполняется аналогично бдоку 13, ; Логический блок 23 составляет список неисправностей СП1, обнаруживаемых очередным входным набором, составляет список неисправностей СП2 обнаруживаемых входными наборами, включенными ранее в тест; подсчитыва ет число неисправностей, содержащихся в СП1, из числа не принадлежащих СП2 (вычисляет меру значимости входного набора); сравнивает меру значимости входного набора с пороговым значением Список неисправностей СП1, обнаруживаемых очередным входным набором.

формируется следунщим образом. Сигнал О или 1 из блока 8 сравнения поступает через элемент И 25 в младший разряд сдвигового регистра 24,

Прохождение этого сигнала через элемент И 25, а также сдвиг содержащего регистра 24 на один разряд в сторону старших разрядов обеспечиваются уп. равляющим сигналом блока 10,

В регистре 21 результатов хранится список неисправностей СП2, обнаруживаемых на всех наборах ъклкпенньк в тест. Список СП2 составляется путем выполнения операции поразрядноi го логического сложения содержимого .регистра 21 с сод&ржш4№1 сдвигового.- :. регистра 24 Дня этого единичный вход каждого триггера регистра 21 соедИг нен с соответствукяцим единичным выг

.ходом триггера регистра 24,

Для подсчета числа неисправностей, содержалоихся в СП1, из числа йе принадпежавцсЕ СП2 блок 10 последовательно опрашивает одноименные разряi ды регистров 21 н 24, Опрос осуврствляетСя путем подачи управлянщ&п} . сигнала йа соответствующий эя&лкаг ;28 И, первый вход которого соединен с Нулевым выходом триггера регистра 21

9 результата, а второй с единичша4 выходом триггера сдвигового регистра 24,

На вькоде злем1внта И 28 (на входе счетчика 26) появляется 1 яшш в

I том случае, если соответстауицая неисправность обнаруживается на очередном входном наборе и не обнаруживается ни на оДном из входных наборов, включенных ранее в тест.

4« На элемент ИЛИ 27 выведены выходы лишь трех разрядов счетчика 26, любая ненулевая комбинация значений которых свндете1и ствует о превышении меры значимости над пороговым значением. Например если в качестве по4Sрогового значения выбрано четыре неисправности, то на элемент ИЛИ 27 должны быть выведены третий и старшие разряды счетчика, В этом случае содержимое счетчика 26 равное значению 4

и более (выходной сигнал элемента ШШ° : равен I), свидетельствует о том, что мера значимости соответственно равна и превышает пороговое значение. При подготовке устройства к работе к формирователю 3 подключают два модуля, (Дпя краткости модуль, неисправности в котором не имитируются в процессе синтеза теста - первый, а модуль, интегральные элементы которого поочередно подключают к имит торам 16 и 17 неисправностей - второй). Одну из интегральных схем 15 второго модуля при помощи сменной платы 14 подключают к устройству, а с помощью выхода 12 сигнала - к модулю. В регистр 9 заносят маску а тивных входных переменных, а в регистр 21 - маску неисправностей в соответствии с выбранной схемой 15. Занесение масок осуществляют при помощи регистра переключателей пульта устройства. Выходы первого модуля со единяют со входами блока 8 сравнения а выходы второго модуля - со входами блока 6 дискриминаторов. Тест для модуля представляет собо совокупность тестов для его интегральных элементов. Синтез теста для модуля осуществляется путем последовательной генерации и оптимизации входной последовательности (теста) для каждой из его интегральных схем При синтезе теста для -ой.интегральной схемы модуля устройство работает следующю образом. После подключения 1-ой интегральной схемы к устройству и второму модулю, а первого и второго модулей к устройству производится установка всех функциональных блоков устройства в исходное состояние и запуск генератора 36 импульсов блоком 20 уп равления имитацией неисправностей. По первому импульсу генератора 36 записывается единица в счетчик 18 не исправностей {осуществляются подготовителыше операции, для имита1.ии первой неисправности в интегральной схеме 5). Возбуждается один из входов дешифраторов 29 или 32, При -ЭТОМ, если в первом разряде регистра 21 содержится 1 (первая неисправность не подлежит имитации), то на выходе одного из логических элементов И 40 устанавливается сигнал 1, а на выходе логического элемента И-НЕ 38 - О. Содержимое счетчика 18 увеличивается на 1, и анализиру ется следукиций разряд регистра 2. В том случае, когда содержимое разряда регистра 21 равно О, на выходе логического элемента И-НЕ 38 формирует ся сигнал 1, Этот сигнал останавливает генератор 36 импульсов и запускает блок 10 управления, В соответствии с содержи в.1м счетч ка 18 осуществляется имитация неисправности. Например, если это состоя. 8 ние задает обрыв второго входа интегральной схемы, то соответствующий элемент И 30 имитатора 16 неисправностей отключает этот вход схемы 15 от линии, связывающей его с одноименным входом (гой интегральной схемы второго модуля. В том случае, когда должна имитироваться неисправность в виде константы О или 1 некоторого выхода интегрального элемента, то соответствующий управляемый .ключ 31 имитатора 17 неисправностей отключает вход второго блока I9 усилителей от соответствующего выхода интегральной схемы.15 и подключает его ко входу рз константных неисправностей, на котором поддерживается сигнал, соответствующий состоянию триггера 33. После окончания процессов коммутации в имитаторах 16 и 17 неисправностей блок 10 управления включает генератор 1 исинхронизатор 2 и тем самым совместно с регистром 9 маски обеспечивает генерирование псевдо- случайных входных наборов из активных переменных и подачу их на входы формирователей 3. Формирователь 3 устанавливает на входах первого н второго модулей последовательность сигналов в. соответствии с набором активных перемендапс. Выходные сигналы первого модуля по щинам 7 поступают на блок сравнения 8 непосредственно, а выходные сигналы второго модуля ПС выходу 3 - через блок 6 дискриминаторов. Причем выходные сигналы второго модуля (реакция модуля с неисправностью) формируются следукицим образом. Входные сигналы интегральной схемы 13 поступают из функциональных целей модуля в блок 13 усилителей и ервый имитатор 16 неисправностей. Сформированные на выходах интегральной схеш 13 сигналы через второй имитатор 17 неисправностей поступают во второй блок I9 усилителей, где приводятся к стандартному виду, и далее - в Функциональные пепи второго модуля. Этим самым осуществляется проверка транспортировки имитируемой неисправности к выходам второго модуля. Выходные сигналы блока 6 дискриминаторов, отражакщие логические значения выходов второго модуля, сравниваются блоком 8 с выходными сигналами первого модуля. Если логические значения сравниваемых сигналов совпадают, то блок 8 формирует

сигнал О, в противном случае - 1 Несовпадение сигналов означает, что имитируемая неисправность на данном наборе активных переменных обнаруживается, иначе - не обнаруживается (не транспортируется этим набором к выходам модуля).

Сигналы О и 1 поступают в логический блок 23 для формирования списка обнаруживаемых неисправностей на текущем входном наборе. Эти сигнапь записываются в млада1ий разряд / регистра 24,а содержимое последнего сдвигается на один разряд вправо сигналом дешифратора 43. Синхросигнал опроса выходов из блока 6, задержанный элементом 44 задержки, с|8;расывает счетчик 42 в ноль. На выходе едеменного распределителя, образованного генератором 41, счетчиком 42 и дешифратором 43, формируется сигнал запуска генератора 36. Этот сигнал запускает генератор 36 импульсов, и процесс повторяется для очередной неисправности 1-го элемента После того как все неисправности )-ой интегральной схемы на рассматриваемом входном наборе окажутся проанализированными, по сигналу переполнения счетчика 18 неисправностей в счетчик 42 блока 10 управления заносится содержимое регистра 45. Н выходе дешифратора 43 формируется сигнал управления элементами И 28, по которому в логическом блоке 23 вычисляется мера значимости входного набора. Если мера значимости входного набора не ниже порогового значения, то на выходе элемента ИЛИ 27 формируется сигнал, блокирующий запуск генератора 41. Этот набор включается в последовательность входных наборов как элементарнь1й тест, а также запоминаются неисправности, обнаруживаемые на этом наборе.

В том случае, когда мера значимос1ти входного набора ниже порогового значения, этот набор исключается из рассмотрения, на выходе элемента ИЛИ 27 формируется сигнал О, и блок 10 управления передает управление схеме 20 управления имитацией неисправностей . Последняя осуществляет управление имитацией неисправности,имеющей наименьший номер в списке необнаруживаемых СП2, и запускает блок 10 для o6ecrteчения формирования очередного набора активных переменных.

Таким образо 1, предлагаемое устройство осуществляет сравнение сигналов не на выходе интегральных элементов, а на выходе модулей интегральных элементов, гарантируя тем самым транспортировку имитируемых неисправностей входными наборами к выходам модуля, что обеспечивает, в свою очередь, повышение полноты проверякщих тестов примерно в два раза. Поскольку число активных переменных для интегральных элементов, как Правило, в несколько разменьше числа входных переменных модуля, а введение регистра 9 маски обеспечивает формирование входных наборов лишь на активных переменных, то это уменьшает трудоемкость задачи перебора на . несколько порядков.

Реализация поиска тестов не на производных входных наборах, а на наборах активных входных переменных существенно уменьшает длину теста. Это объясняется тем, что эффективность наборов активных входных переменных вьш1е эффективности произвольных наборов. Кроме того, ведение логического блока и его связей позволяет проводить локальную оптимизацию теста, например, по известному критерию Чжена, что уменьшает дпину теста, синтезируемого с помощью, предлагаемого устройства,в несколько раз. Формула изобретения

S

исправности является первь04 выходом устройства, первый вход формирователя сигналов подключен к выходу генератора псевдослучайных последовательностей, первый вход которого соединен с

первым выходом синхронизатора, второй выход которого подключен ко второму входу формирователя сигналов, третий вход которого соединен с первым управляющим выходом блока управления, второй, третий, четвертый и пятый управляющие выходы которого подключены соответственно к первому входу синхронизатора, объединенного со ВТОрым входом генератора псевдослучайшлс последовательностей, к первому входу блока дискриминаторов, к первому входу блока сравнения и ко вход запуска блока управления имитацией неисправностей, первый вход блока управления подключен к первому выходу блока дискриминаторов, второй выход которого соединен со вторым входом блока сравнения, третий вход которого является входом сигнала эт лона устройства, сигнальный вход блока дискриминаторов является вторым входом устройства, импульсный вход блока управления объединен со входом запуска блока управления имитацией неисправностей, первый вход запуска блока управления подключен к первому выходу счетчика неисправностей, вход которого подключен к первому входу имитатора неисправностей и к выходу блока управления имитацией неисправностей, второй выход счетчика неисправностей подключен ко второму входу имитатора неисправностей, третий вход которого подключен к выходу первого блока усипителей, первый выход имитатора неисправностей подключен к первому входу блока управления имитацией неисправностей, четвертый вход которого соединен с первой группой входов регист ра результатов, о т лич ающ е ее я тем, что с целью увеличения полноты контроля, в него введены логический блок, первый и второй входы которого подключены соответственно к пятому и шестому управляющим выкодам блока управления, вход запуска котстрого подключен к первому выходу логического блока, второй выход кото рого подключен к группе входов регис ра результатов, вторая грушта выходов Которого соединена с третьим вхо дом логического блока, четвертый вхо которого соединен с выходом блока срдвнения, входы второго блока усили телей подключены к группе выходов имитатора неисправностей, выход второго блока усилителей соединен со вхрдом первого блока усилителей и является входом-выходом устройства. 3 . 12 2. Устройство по n.i,o т, л и ч а ю щ е е с я тем, что блок управле ния содержит дешифратор, элемент задержки, генератор импульсов, счетчик и регистр, причем вькоды дешифратора являются управлякхцими выходами блока, группа входов дешифратора соединена с группой выходов счетчика, первый вход которого является вторым входом запуска блока, второй и третий входы счетчика подключены соответственно к выходу элемента задержки и к выходу генератора импульсов, вход элемента задержки является первым входом блока, первый вход генератора импульсов является первым входом запуска блока, второй вход генератора импульсов является импульсным входом блока, группа выкодов регистра подключена к rpymfe входов счетчика. 3. Устройство по п.I, о т л и ч аю щ ее с я тем, что логический блок содержит регистр сдвига, элементы И, группу элементов И, элемент ИЛИ и счетчик, причем первый вход элемента И объединен, с тактовым входом регистра сдвига и является первым входом блока, второй вход элемента И является четвертым входом блока, выход элемента И подключен к сдвиганнцему входу регистра сдвига, первая группа выходов регистра сдвига подключена к первой группе входов элементов И группы и является вторым входом блока, вторая rpjmna входов элементов И группы является вторыми входами блока, третьим входом блока, выход каждого элемента И группы подключен к группе входов счетчика, группа выходов которого подключена к группе входов элемента ИЛИ. выход которого является первым выходом блока. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство CCGP № 526895, кл. G Об F 11/00, 1974.. 2.Авторское свидетельство СССР № 519713, кл. G Об F 11/00, 1974 (прототип).

.-.rij feL

s t .

bfib--1

Авторы

Даты

1981-11-30—Публикация

1980-02-11—Подача