а второй ВЫХОД -с третьими входами блоков пересылки старших тетрад байтов первого и второго регистров.

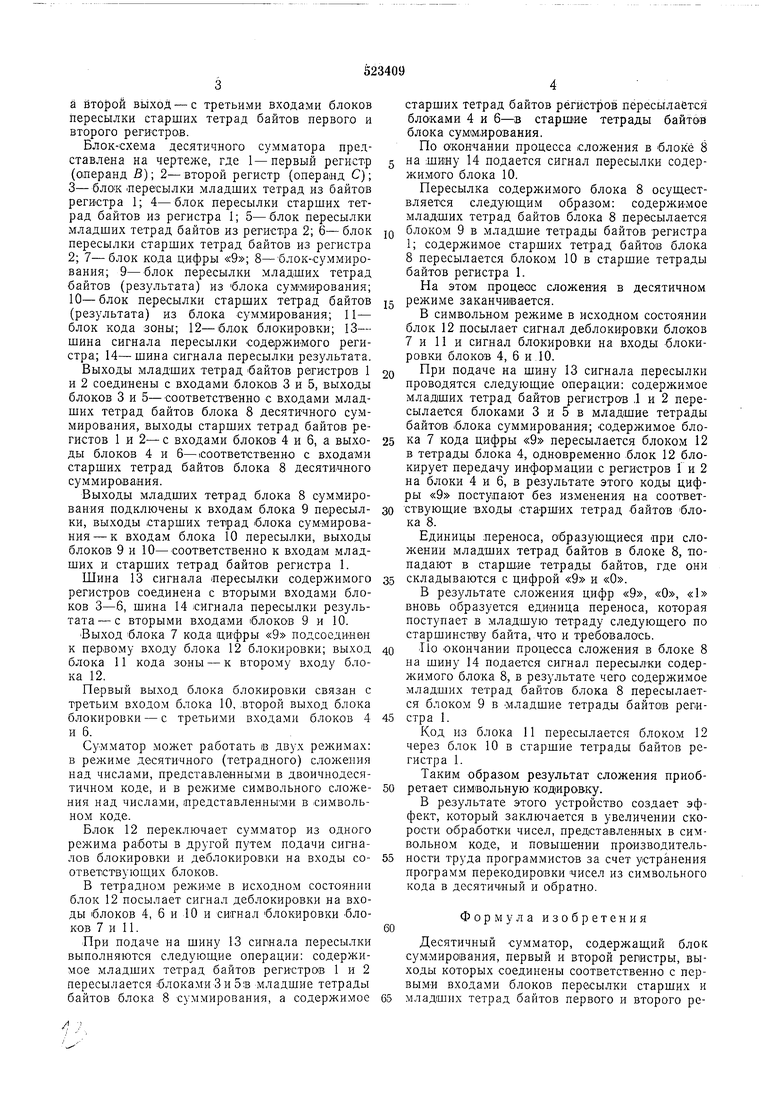

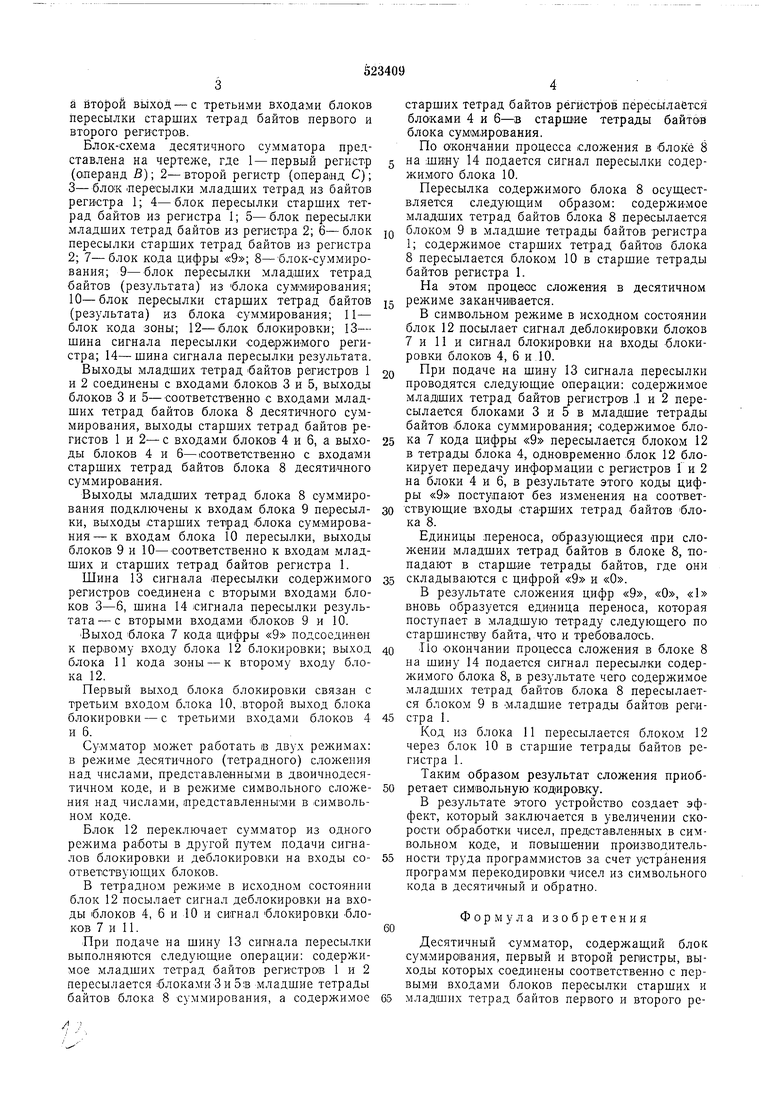

Блок-схема десятичного сумматора представлена на чертеже, где 1-первый регистр (олеранд В); 2-второй регистр (операнд С); 3-блокПересылки младших тетрад из байтов регистра 1; 4-блок пересылки старших тетрад байтов из регистра 1; 5 блок пересылки младших тетрад байтов из регистра 2; 6- блок пересылки старших тетрад байтов из регистра 2; 7-блок кода цифры 8-блок-суммирования; 9-блок пересылки младших тетрад байтов (результата) из блока суммирования; 10-блок пересылки старших тетрад байтов (результата) из блока суммирования; И- блок кода зоны; 12-блок блокировки; 13- шина сигнала пересылки содержимого регистра; 14-шина сигнала пересылки результата.

Выходы младших тетрад байтов регистров 1 и 2 соединены с входами блоков 3 и 5, выходы блоков 3 и 5-соответственно с входами младших тетрад байтов блока 8 десятичного суммирования, выходы старших тетрад байтов регистов 1 и 2- с входами блоков 4 и 6, а выходы блоков 4 и 6-соответственно с входами старших тетрад байтов блока 8 десятичного суммирования.

Выходы младших тетрад блока 8 суммирования подключены к входам блока 9 пересылки, выходы старших тетрад блока суММирования - к входам блока 10 пересылки, выходы блоков 9 и 10-соответственно к входам младших и старших тетрад байтов регистра 1.

Шина 13 сигнала пересылки содержимого регистров соединена с вторыми входами блоков 3-6, шина 14 сигнала пересылки результата- с вторыми входами блоков 9 и 10.

Выход блока 7 кода цифры «9 подсоединен к первому входу блока 12 блокировки; выход блока 11 кода зоны - к второму входу блока 12.

Первый выход блока блокировки связан с третьим входом блока 10, .второй выход блока блокировки - с третьими входами блоков 4 и 6.

Сумматор может работать в двух режимах: в режиме десятичного (тетрадного) сложения над числами, представле1нными в двоичнодесятичном коде, и в режиме символьного сложения над числами, представленными в символьном коде.

Блок 12 переключает сумматор из одного режима работы в другой путем подачи сигналов блокировки и деблокировки на входы соответствуюш,их блоков.

В тетрадном режиме в исходном состоянии блок 12 посылает сигнал деблокировки на входы блоков 4, 6 и 10 и сигнал блокировки блоков 7 и 11.

При подаче на шину 13 сигнала пересылки выполняются следующие операции: содержимое младших тетрад байтов регистров 1 и 2 пересылается блоками 3 и 5в младшие тетрады байтов блока 8 суммирования, а содержимое

старших тетрад байтов регистров пересылается блоками 4 и 6-в старшие тетрады байтов блока суммирования.

По окончании процесса сложения в блоке 8 на шину 14 подается сигнал пересылки содержимого блока 10.

Пересылка содержимого блока 8 осуществляется следующим образом: содержимое младших тетрад байтов блока 8 пересылается

блоком 9 в младщие тетрады байтов регистра 1; содержимое старших тетрад байтов блока 8 пересылается блоком 10 в старшие тетрады байтов регистра 1.

На этом процесс сложения в десятичном

режиме заканчивается.

В символьном режиме в исходном состоянии блок 12 посылает сигнал деблокировки блоков 7 и И и сигнал блокировки на входы блокировки блоков 4, 6 и,10.

При подаче на шину 13 сигнала пересылки проводятся следующие операции: содержимое младших тетрад байтов регистров .1 и 2 пересылает1ся блоками 3 и 5 в младшие тетрады байтов блока суммирования; содержимое блока 7 кода цифры «9 пересылается блоком 12 в тетрады блока 4, одновременно блок 12 блокирует передачу информации с регистров Г и 2 на блоки 4 и 6, в результате этого коды цифры «9 поступают без изменения на соответствующие входы Старших тетрад байтов блока 8.

Единицы переноса, образующиеся при сложении младших тетрад байтов в блоке 8, попадают в старшие тетрады байтов, где они

складываются с цифрой «9 и «О.

В результате сложения цифр «9, «О, «1 вновь образуется единица переноса, которая поступает в младшую тетраду следующего по старшинст1ву байта, что и требовалось.

Г1о Окончании процесса сложения в блоке 8 на шину 14 подается сигнал пересылки содержимого блока 8, в результате чего содержимое младших тетрад байтов блока 8 пересылается блоком 9 в Младшие тетрады байтов репистра 1.

Код из блока 11 пересылается блоком 12 через блок 10 в старшие тетрады байтов регистра 1. Таким образом результат сложения приобретает символьную кодировку.

В результате этого устройство создает эффект, который заключается в увеличении скорости Обработки чисел, представленных в символьном коде, и повышении производительности труда программистОВ за счет устранения программ перекодировки чисел из символьного кода в десятичный и обратно.

Формула изобретения

Десятичный сумматор, содержащий блок суммирования, первый и второй регистры, выходы которых соединены соответственно с первыми входами блоков пересылки старших и младших тетрад байтов первого и второго регистров, Ёторые входы которых соединены с шиной сигнала пересылки содержимого регистров, а выходы соединены с соответствующими входами блока суммирования, выходы младших и старших тетрад байтов которого соединены с первыми входами блоков пересылки младших и старших тетрад байтов результата, вторые входы которых соединены с шиной сигнала пересылки результата, а выходы соединены с соответствующими входами первого регистра, отличающийся тем, что,

с целью повышения бьтстроДёйствия, он содержит дополнительно блок кода цифры «9, блок кода зоны и блок ;блокировки, первый и второй входы которого соединены соответственно

с выходом блока кода цифры «9 и выходом блока кода зоны, а первый выход соединен с третьим входом блока пересылки старших тетрад байтов результата, второй выход соединен с третьими входами блоков пересылки

старших тетрад байтов первого и второго регистров.

| название | год | авторы | номер документа |

|---|---|---|---|

| Арифметическое устройство | 1978 |

|

SU687982A1 |

| Матричное устройство для умножения | 1985 |

|

SU1267408A1 |

| Устройство для умножения | 1985 |

|

SU1262484A1 |

| Устройство для умножения чисел | 1989 |

|

SU1817091A1 |

| Устройство для умножения | 1989 |

|

SU1668979A1 |

| Множительное устройство | 1982 |

|

SU1053104A1 |

| Устройство для обработки данных переменной длины | 1986 |

|

SU1675897A1 |

| Множительное устройство | 1982 |

|

SU1116427A1 |

| Микропрограммный процессор | 1980 |

|

SU868766A1 |

| Устройство для умножения | 1982 |

|

SU1229758A1 |

Авторы

Даты

1976-07-30—Публикация

1974-06-18—Подача