(54) УСТРОЙСТВО ДЛЯ РЕШЕНИЯ АЛГЕБРАИЧЕСКИХ УРАВНЕНИЙ

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой функциональный преобразователь | 1980 |

|

SU928347A1 |

| Вичислительное устройство | 1979 |

|

SU783804A1 |

| Функциональный генератор напряжения | 1976 |

|

SU734746A2 |

| Функциональный преобразователь | 1984 |

|

SU1211756A1 |

| Функциональный преобразователь | 1984 |

|

SU1171774A1 |

| Генератор функций | 1984 |

|

SU1241219A1 |

| Устройство для вычисления функций синуса и косинуса | 1984 |

|

SU1205140A1 |

| Устройство для решения систем ли-НЕйНыХ АлгЕбРАичЕСКиХ уРАВНЕНий | 1978 |

|

SU811275A1 |

| Последовательное множительное устройство | 1981 |

|

SU1067500A1 |

| Вычислительное устройство | 1982 |

|

SU1040493A1 |

1

Изобретение относится к гибридной вычислительной технике и может быть использовано при разработке специализированных гибридных зычисдитрльных машин и вычислителей для решения конечных уравнений.

Известны аналоговые и квазианалоговые моделирующие устройства, предназначенные для решения конечных уравнений, реализующие метод минимизации штрафной функции . Наиболее близким техническим реше- нием является устройство для решения алгебраических уравнений, содержащее одноразрядный сумматор, селектор нулевого кода, реверсивный счетчик, выходы старших разрядов которого соединены со входами дешиф ратора, а выходы младших разрядов - с первым входом блока умножения, второй вход которого подключен к выходу первого сумматора, а выход соединен с первым входом второго сумматора, элемент И, первый вход которого соединен с выходом генератора импульсов, а выход подключен к счетному входу реверсивного счетчика, входы первого сумматора подключены соответственно к выходам первого и второго блоков

;памяти, а второй и третий входы второго сумматора соединены соответственно с выходами третьего и четвертого блоков памяти f23 .

Недостатками таких устройств являются ограниченный класс решаемых задач и сравнительно сложная структура.

С целью расширения класса решаемых задач в предложенном устройстве входы блоков памяти подключены к соответствую- шдм выходам дешифратора, выход второго сумматора через селектор нулевого кода подключен ко второму входу элемента И, а выходы знаковых разрядов первого и второго сумматоров соединены со входами одноразрядного сумматора, выход которого подключен к управляющему входу реверсивного счетчика.

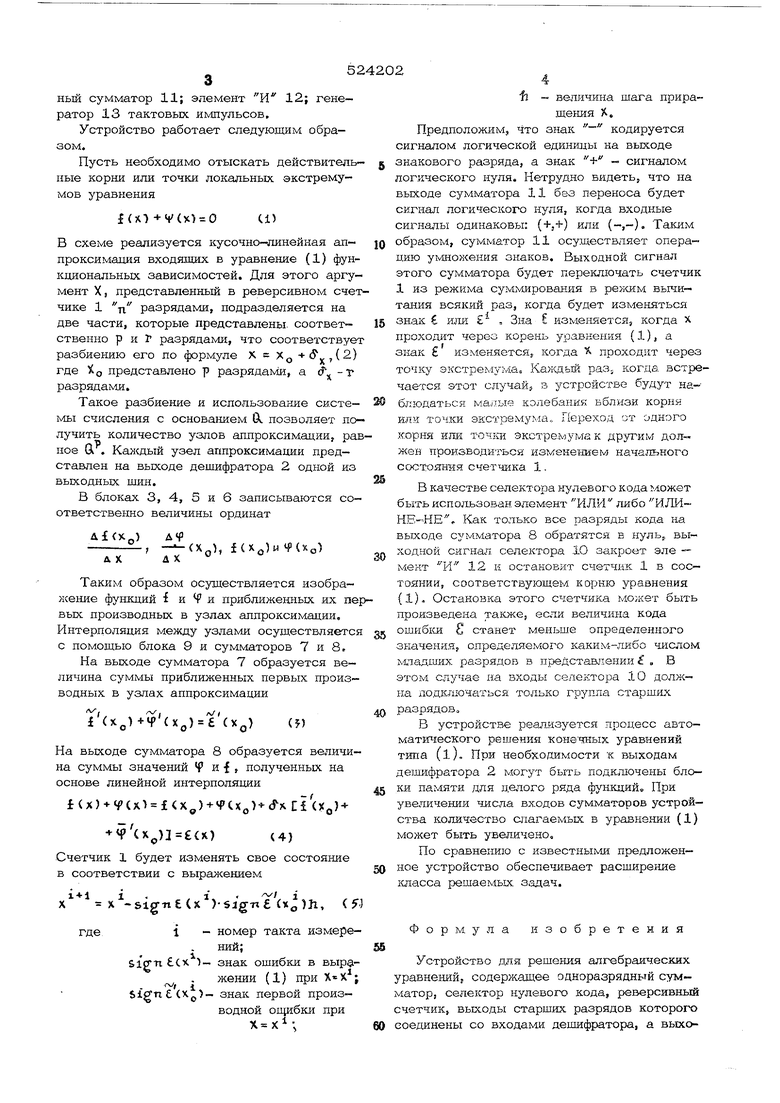

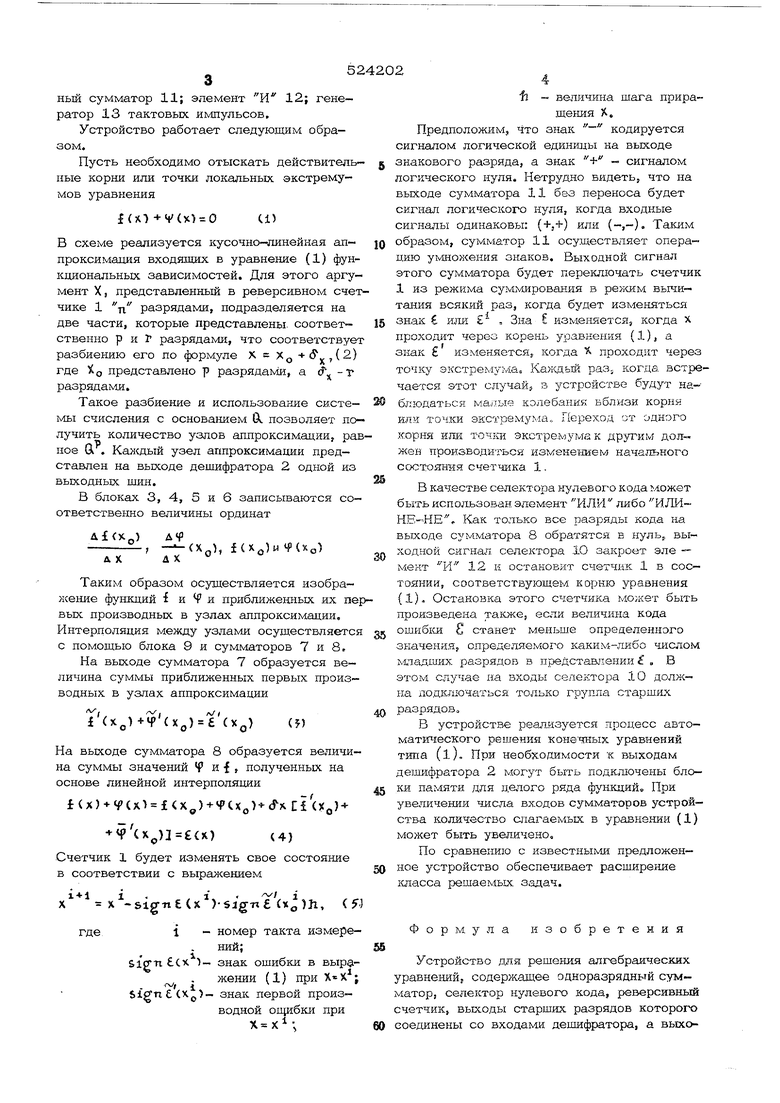

На чертеже приведена схема предложенного устройства.

Устройство содержит реверсивный счетчик 1; дешифратор 2; блоки 3, 4, 5 и 6 памяти; сумматоры 7 и 8; блок 9 умножения; селектор 10 нулевого кода; одноразрядный сумматор 11; элемент И 12; генератор 13 тактовых импульсов. Устройство работает следующим образом. Пусть необходимо отыскать действитель ные корни или точки локальных экстремумов уравнения f (хО +V(x 0 В схеме реализуется кусочно-линейная ал- проксимация входящих в уравнение (1) фун кциональных зависимостей. Для этого аргу мент X, представленный в реверсивном сче чике 1 тт. разрядами, подразделяется на две части, которые представлены, соответственно р и 1 разрядами, что соответствуе разбиению его по формуле X XQ +6 (2 где iCg представлено р разрядами, а ,-T разрядами. Такое разбиение и использование систе мы счисления с основанием (X позволяет по лучить количество узлов аппроксимации, ра ное Q . Каждый узел аппроксимации представлен на выходе дешифратора 2 одной из выходных шин. В блоках 3, 4, 5 и 6 записываются со ответственно величины ординат о Х ), f (Хд)иЧ1(Хо) Д X Таким образом осуществляется изобра- лсение функций f и Ч и приближенных их пе вых производных в узлах аппроксимации. Интерполяция между узлами осуществляетс с помощью блока 9 и сумматоров 7 и 8. На выходе сумматора 7 образуется величина суммы приближенных первых произ водных в узлах аппроксимации i х)+ЧСх„) (х„) На выходе сумматора 8 образуется величи на суммы значений V и f , полученных на основе линейной интерполяции f (X) t-Ч (х f х)+ ЧСХо) cSx С UQ) (Х)Д(х) Счетчик 1 будет изменять свое состояние в соответствии с выражением X х -&ig-ti(x )-sjg7t (Хд )}г.

1 - номер такта измерений;

blVn сч 1- знак ошибки в выр$ . жении (1) при Х«К ; (Xjj)- знак первой производной ощибки при X X ;

ормула изобретения

Ф

Устройство для решения алгебраических уравнений, содержащее одноразрядный сумматор, селектор нулевого кода, реверсивный счетчик, выходы старших разрядов которого соединены со входами дешифратора, а выхоfi величина щага приращения К. Предположим, что знак кодируется сигналом логической единицы на выходе знакового разряда, а знак + - сигналом логического пуля. Нетрудно видеть, что на выходе сумматора 11 без переноса будет сигнал логического нуля, когда входные сигналы одинаковы: (+,+) или (-,-). Таким образом, сумматор 11 осуществляет операцию умножения знаков. Выходной сигнал этого сумматора будет переключать счетчик 1 из режима суммирования в режим вычи- та11ия всякий раз, когда будет изменяться знак С или , Зна изменяется, когда i проходит через корень уравнения (1), а знак изменяется, когда проходит через точку экстремума. Ка)5одый раЗ; когда встречается этот случай, 3 устройстве будут наблюдаться Majjbie кэлебаник вблизи корни или точки экстремума,. Переход от одного корня или точки SKCTpe.Mytvfa к другим дол- жен производиться изменениеГЛ начального состоян-ия счетчика 1. В качестве селектора нулевого кода может быть использован элемент ИЛИ либо ИЛИНЕ--НЕ, Как только все разряды кода на выходе сумматора 8 обратятся в нуль., выходной сигнал селектора 10 закроет эле - мент И 12 и остановит счетчик 1 в состоянии, соответствующем корню уравнения (1). Остановка этого счетчика может быть произведена также, если величина кода ошиб1ш станет меньше определенпого значения, определяемого каким-либо 4iicnoM младших разрядов в преДставлт.ении , В этом слугае на входы селектора 10 должна подключаться только группа старших разрядов. В устройстве реализуется процесс автоматического решения конечных уравнений типа (l). При необходимости к выходам дешифратора 2 могут быть подключены блоки памяти для целого ряда функций При увеличении числа входов сумматоров устройства количество слагаемых в уравнении (1) может быть увеличено. По сравнению с известными предложенное устройство обеспечивает расширение 1шасса ре,шаемых, задач.

ды младших разрядов - с первым входом блока умножения, второй вход которого подключен к выходу первого сумматора, а выход соединен с первым входом второго сумматора, элемент И, первый вход которого соединен с выходом генератора импульсов, а выход подключен к счетному входу реверсивного счетчика, входы первого сумматора подключены соответственно к выходам первого и второго блоков памяти, а второй и третий входы второго сумматора соединены соответственно с выходами третьего и четвертого блоков памяти, отличающееся тем, что, с целью расширения класса решаемых уравнений, входы блоков памяти подключены

к выходам дешифратора, выход второго сумматора через селектор нулевого кода подключен ко второму входу элемента И, а выходы знаковых разрядов первого и второго сумматоров соединены со входами одноразрядного сумматора, выход которого подключен к управляюшему входу реверсивного счетчика.

Источники информации, принятые во внимание при экспертизе:

1,Авт. св. СССР № 304600, кл. G 06 С 7/26, 1969 г.

Авторы

Даты

1976-08-05—Публикация

1974-12-27—Подача