(54) АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ

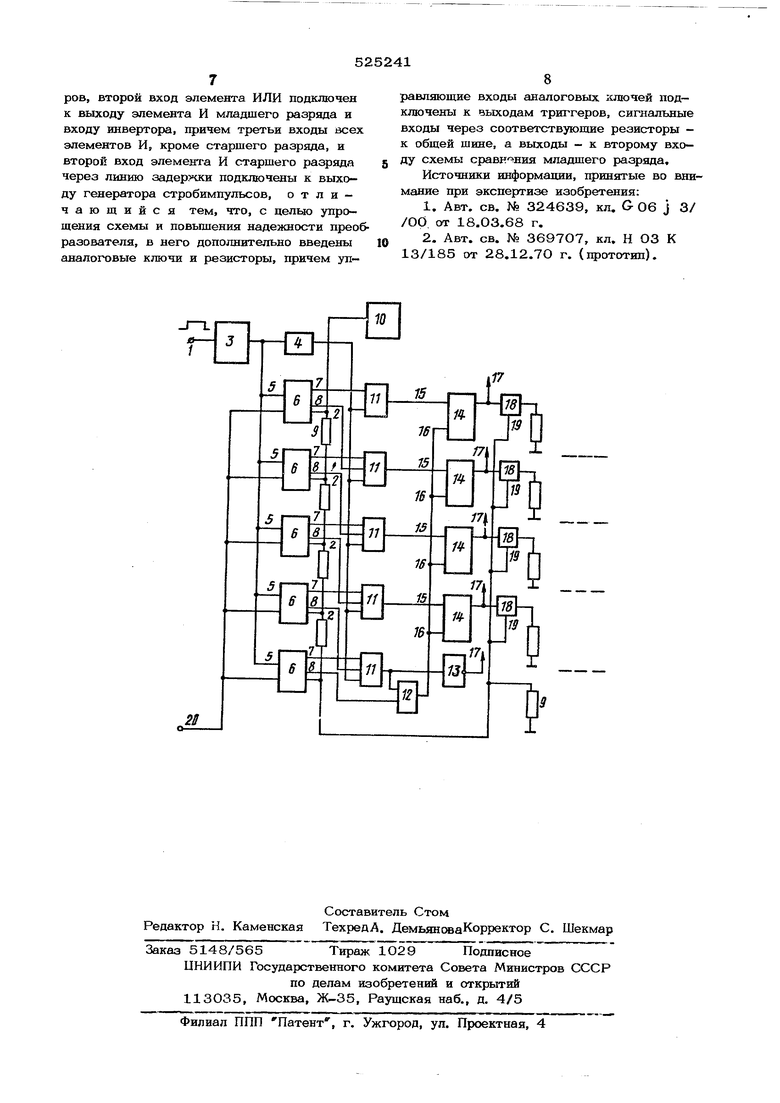

ных процессов непосредственно в самом преобразователе отсутетву т, Эдго, в особенности при неидеальности элементов, приводит к хаотичному наложению переходных процессов переключения схем сравнения при резких изменениях входного напряжения, триггеров и логических элементов. Поэтому схемы сравнения рабитагот в тяжелом режиме многократного несинхронного переключения из одного состогШия в другое из-за I помех, возникающих } на выходах триггеров, что снижает надежность работы преобразо- | вателя. Целью изобретения является упрощение схемы преобразователя и увеличение надежности его раббты. Это достигается тем, что в преобразователь дополнительно введены аналоговые ключи и резисторы, причем управл55аощне . входы аналоговых ключей подключены к выходам триггеров, сигнальные входы через соответствующие резисторы - к обшей шине, а выходы - к второму входу схемыj сравнения младшего разряда. Такая структура; Iпреобразователя позволяет исключить прог рессивное возрастание количества логических.элементов, ключей, цифровых управляемых сопротивлений, триггеров в зависимости от разрядности и упрощает конструкцию 1 преобразо.вателя. На чертеже показана блок-схема предлагаемого преобразователя где: 1 - управляю- ций вход генератора стробимпульсов, 2 - аналоговые входы схемы сравнения, 3 - ге-. нератор стробимпульсоЬ, 4 - лшгия задержк&, 5 - управляющий вход схемы сравнения, 6 - схемы сравнения, 7 - первый выход схемы сравнения, 8 - второй выход схемы сравнения, 9 резистивный делитель, 10 источник эталонного напряжения, 11 - элемент И| 12 - элемент ИЛИ, 13 - инвертор, 14 - триггер, 15 - первый вход триггера, 16 - второй вход триггера, 17 - выход параллельного кода, 18 - аналоговый ключ, 19 - выход аналогового ключа, 20 - входная щина. ; Выход генератора стробимпульсоа 3 соединен с управляющими входами 5 схем сравнения 6, первые аналоговые входы хегорыхХ Подклйчены к входной шине 19 преобразователя, вторые аналоговые входы 2 - к узлам |эезистивного делителя 9, один вывод которо го подключен к выходу источника эталонного напряжения 10, а другой - к общей шине, первые выходы 7 каншой схемы сравнения через соответствующие элементы 11 И соединены с первыми входами 15 триггеров 14 а вторые выходы 8 всех схем сравнения, I кроме схемы сравнения младшего разряда, подключены к вторым входам элементов И

Прёдыдущйх разрядов, второй выход 8 схемы сравнения младшего разряда соединен через элемент 12 ИЛИ со вторыми входами 16i

триггеров, второй вход элемента 12 ИЛИ подключен к выходу элемента 11 И младшего разряда и входу инвертора 13, причем третьи; входы всех элементов 11 и кроме старшего ; разряда, и вход элемента И старшего разряда через линию задержки 4 подключены к выходу генератора стробимпульсов 3, управляюшие входы аналоговых ключей 10 подключены к выходам триггеров 14, сигнальные входы череа соответствующие рв«зисторы - к общей шине,.а выходы- к вто:раму входу 2 схемы сравнения 6 младшего разряда. Резисторы резистивного делителя 9, включенные последовательно, имиот распределение весов в соответствии с двоичным законом, то есть, резистор 9, подклю-ченный к источнику эталонного напряжения 1О имеет вес, равный восьми условным единицам, следующий - четырем, следующийдвум и так далее до одного. Напряжение на аналоговом входе 2 схемы сравнения 6 |младшег-о разряда определяется весом парап-; лельно включе1шых аналоговых ключей 18 ;И резистора резистивного делителя 9 младшего разрада, суммарный вес которых равен 1. За исходное примем состояние, когда входное напряжение равно нулю, а на входе 1 отсутствует управляющий потенциал. В исходном состоянии все аналоговые ключи is включены и на входах 2 схем срав- : нения 6{напряжения представлены в условных единицах следующим рядом: 6; 8; 4; 2; 1, (начиная со старшего разряда)-; на выходах 17 сигналы соответствуют логическому нулю; генератор стробимпульсов 3 выклю чен, на входах 5, 15, 1.6 и-выходах 7,; | 8 - сигналы логического нуля. Преобразователь работает следующим об- разом.i При подаче разрешающего потенциала на вход 1 включается Генератор 3 и начинается периодический опрос импульсными сигналами логической единицы схем сравнения 6, Ч&,рез интервал Т , определяемый линией задержки 4, осуществляется огфос элементов 11 И. Величина Т определяется задержкой, срабатывания схем сравнения 6 и может быть весьма малой (единицы не ). Предположим, что по входу 2О действует напряжение величиной одиннадцать условных единиц. При воздействии стробимпульса происходит срабатывание всех, кроме стар- . ией, схем сравнения 6, в результате чего на выходах 7 появляется сигнал логической единицы, а на выходах 8 - логический ноль. Срабатывание логических элементов 11 И , во всех разрядах, кроме четвертого, взаимко блокируется. Действующий через время сигнал производит опрос элементов НИ при установившихся состояниях выходов 7, 8 схем сравнения 6, поэтому помехи на вы ходах элементов 11 И отсутствуют. Это существенно увеличивает (надежность работы преобразователя.,-.Сигнал с выхода элемента 11 И третьего разряда включит по входу 15 триггер 14 На выходе 17 этого разряда ПОЕЗЙТСЯ сиг-. нал i погической единьоы и аналоговый ключ |18 отюяочит цифровое управляемое сопротав ление от выкода 19. В результате суммар |ный вес резистора младшего разряда иэ мекк1Сй, а именно увеличится пропоршшналыю весу включе шого разряда, то есть На восемь условных единиц. Таким образом шкала порогов схем сравнения 6 изменится и соответствии со следующим i разбиением В условных едшпишх напряжения 24; 16; il2j 10; 9 (начгшая со старшего разряда). Следующий стробимпульс произведет опро схем сравнения 6, в результате чего сработает триггер разряда, соответствующего 2 , Шкала порогов изменится в соответствии с числами: 26; 18; 114; 12; 11. В следующем такте сработает схема сравнения младшего разряда 2, произойдет установка через элемент 12 ИЛИ всех триггеров, придем переход на выходах 17 всех разрядов фиксирует код, соответствующий коду 1, а отсутствие такого пере хода Iсоответствует коду О, В случае, начиная со старшего разряда,будем иметь код .01011, то есть одизянадцать Период повторения стробимпульс о в равен суммарной задержке в последовательное цепи: логический элемент 11 И, триггер 14 аналоговый ключ. 18. Таким образом, в зависимости от применяемых элементов доотаточно лишь варьировать частоту повторений строГ1.мпульсов, чтобы обеспечить скихроии™ 3aaiao переходных процессов в преобразова(теле. Очевидно, что воздействие урааново|Шиваюшэго напряжения на схему сраЕнения jnpoHcxDAHT в промежутках между стробируюиимя сигна/шми, что облегчает режим ее работы в динамике. Опрос схем сравнения производится в установившемся режиме. Это уменьшает винамяческ ю погрешность и увв- |ЛичиЕает надежность работы, Режим раЗоты преобрезоватепя является ;Квазз5адантявным по (Угношению к|велич1Шв :и скорости измерения входного сигнала. При 1 мапой скоростииэме.нения входного сигнала |Бремя преобразований определяется числом строб;:.; 4jjJiHnfl: в зависклюстй от величины JHaiu лжени й на входе 20 может потребовать СЕ одно или HecicoJibKo стробнрованнй до мо|меита выдачи параллельного кода. Например, для напряжения, равного одиннадцати условным единицам потребовалось три стробимпул1 са, для напряжения, равного |семнадцати условным единицам - два. В первом случае необходимое время преобразования состоит из двух периодов повторения стробимпульсов, во втором - из одного. 1 Количество стробимпульс ов определяется срабатыванием {схемы сравнения 6 младшего разряда 2 . напряжение по вхо ду 20 превышает пороговое напряжение на ее входе 2, а запрещающий сигнал с выхеда 8 схемы сравнения 6 предшествующего разряда отсутствует, то сигнал с выхода 7 схемы сравнения 6 младщего |ра эяда фиксирует окончание цикла преобразования. Если напряжение на входе 20 меньше порогового на входе 2 схемы сравнений 6 младщего рязряда, то сигнал на выходе 8 этой схемы также фиксирует окончание цикла преобразования. Такой принцип действия дает преимущества при реэких изменениях exoRHofo напряжения больших величин веса младшего разряда. Если резкое изменение величины входного напряжения совпадает с темпом преобразования, то цикл преобразования не прерывается, а точная оценка выдается в конце цикла. Зсли это изменение не согласовано, то цикл преобразования прекращается, при этом выдается значение напряжения в цифровом коде до момента I изменения и начинается ювый цикл преобразования. Таким образом, обеспечивается квазиадаЬтивный выбор длительности цикла преобразования в зависимости от Iскорости изменения и знака производной входного напряжения. Это увеличивает надежность работы. Формула изобретения Аналого-цифровой преобразователь, содержащий генератор стробимпульсов, выход ко|торого соединен с управляющими входами схем сравнения, первые (аналоговые входы которых подключены к входной шине Щ)й6бразователя, вторые аналоговые входы - к узлам резистивного делителя, один вывод которого подключен к выходу источника enraU лонного напряжения, а другой вывод - к об)щей шине, первые выходы каждой схемы срав1ения через соответствующие элементы И соединены с первыми входами триггеров, а вторые выходы всех схем сравнения, кроме хемы сравнения младшего разряда, подключены к вторым входам элементов И предыущих разрядов, второй выход схемы cpaa-i ения младиего разряда соедш{ен через цемент ИЛИ со вторыми входами триггеров, второй вход элемента ИЛИ подключен к выходу элемента И младшего разряда и входу инвертора, причем третьи входы всех элементов И, кроме старшего разряда, и второй вход элемента И старшего разр5ща через линию задер чки подключены к выходу генератора стробимпульсов, отличающийся тем, что, с целью упрощения схемы и повьш1ения надежности преобразователя, в него дополнительно введены аналоговые ключи и резисторы, причем управляющие входы аналоговых ключей подключены к выходам триггеров, сигнальные входы через соответствующие резисторы к общей шине, а выходы - к второму входу схемы сравн ния младшего разряда.

Источники информации, принятые во внимание при экспертизе изобретения:

1.Авт. св. № 324639, кл. G Об j 3/ /ОО от 18.03.68 г.

2.Авт. св. № 3697О7, кл. Н ОЗ К 13/185 от 28.12.7О г. (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровой преобразователь | 1976 |

|

SU610295A2 |

| Аналого-цифровой преобразователь | 1980 |

|

SU1117835A1 |

| Аналого-цифровой преобразователь | 1984 |

|

SU1251326A1 |

| Аналого-цифровой преобразователь | 1983 |

|

SU1095389A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ С САМОКОНТРОЛЕМ | 2010 |

|

RU2431233C1 |

| Аналого-цифровой преобразователь | 1983 |

|

SU1132357A1 |

| Аналого-цифровой преобразователь | 1981 |

|

SU970680A1 |

| Аналого-цифровой преобразователь с самоконтролем | 1980 |

|

SU886236A2 |

| Цифроаналоговый преобразователь | 1981 |

|

SU1027811A1 |

| СПОСОБ ИЗМЕРЕНИЯ СКОРОСТИ ВРАЩЕНИЯ ВАЛА И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1991 |

|

RU2017156C1 |

Авторы

Даты

1976-08-15—Публикация

1975-04-11—Подача