1

Изобретение относится к области импульсной техники, в частности к устройствам аналого-цифрового преобразователя, и может быть использовано в системах обработки информации.

Известен аналого-цифровой преобразователь параллельного взвешивания с высоким быстродействием, содержащий схемы сравнения, эталонный источник тока, триггеры, аналоговые ключи, логические элементы. Разбиение диапазона входной величины осуществляется неравномерным распределением порогов срабатывания схем при введении смещения значений порогов. Смещение вводит ся в зависимости от веса срабатывающих схем сравнения l.

Недостатком известного преобразователя является необходимость прогрессивного (в зависимости от разрядности наращивания оборудования, что усложняет устройство, приводит при практической реализации к снижению быстродействия и надежности работы.

По основному авт.св. I 525241 известен аналого-цифровой преобразователь, содержащий в каждом разряде схему сравнения с выходами сложения И вычитания, триггер, элементы комбинационной логики И, ИЛИ, цифровые

управляемые резисторы и ключи/ подключенные к выходам триггеров, источни| этсшонного тока и генератор стробимпульсов .

Однако при преобразовании быстроизменяющихся напряжений, время изменения которых существенно меньше времени такта, а производная имеет положительный знак, возможно возникновение сбоев в работе преобразователя на время такого положительного выброса. Сбои выражаются в затормаживании процесса преобразования на время дей- ствия такого положительного выброса. Аналогичная ситуация возникает и при действии помех. Это сопровождается ошибками преобразования и уменьшает надежность работы преобразователя. Это уменьшает надежность работы преобразователя и точность при преобразовании быстроизменяющихся напряжений

Целью изобретения является повыше ние надежности работы и точности преобразования.

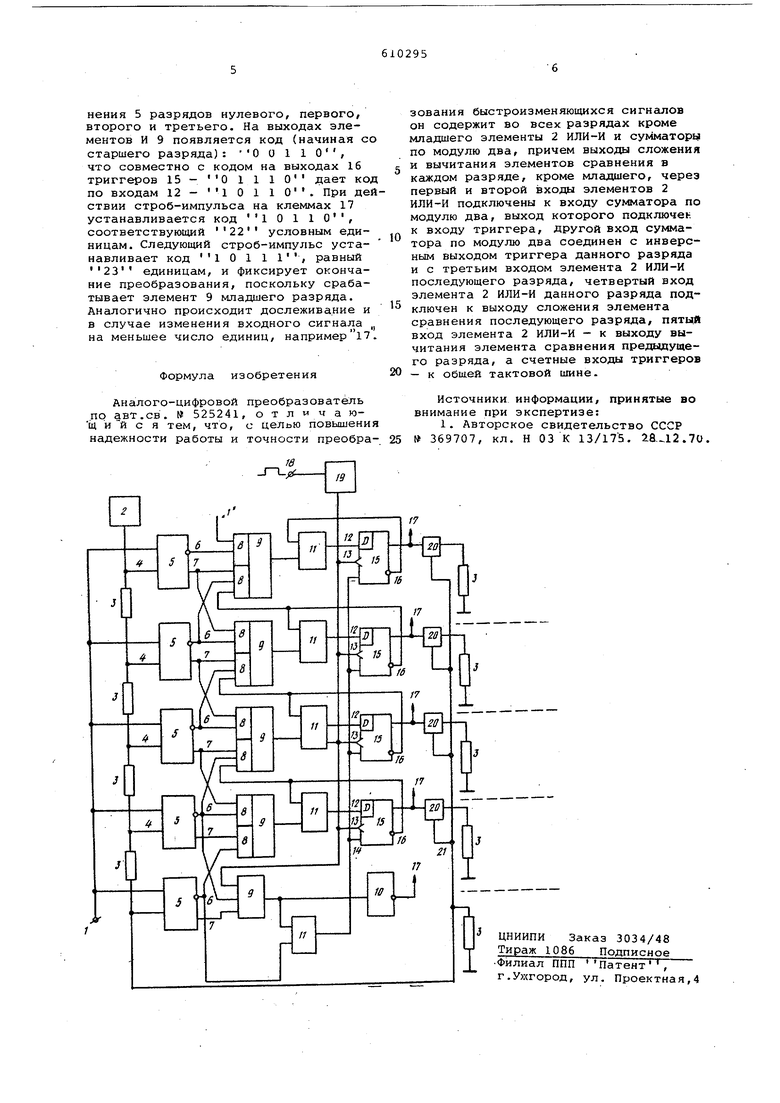

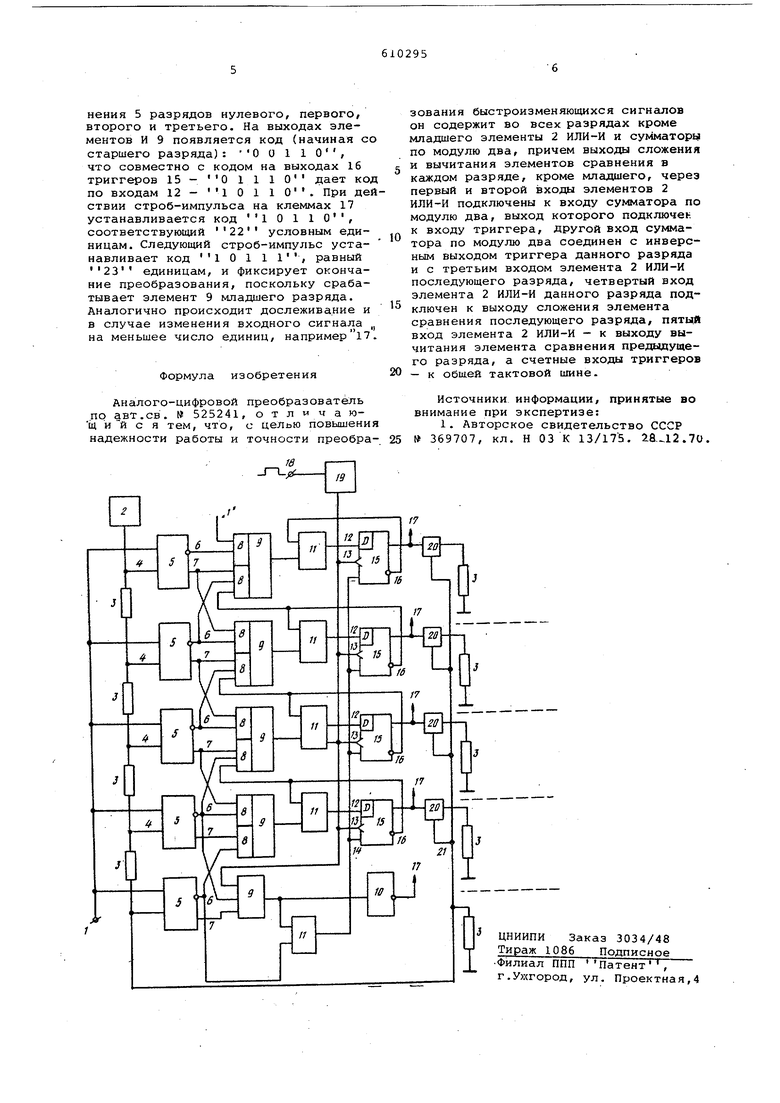

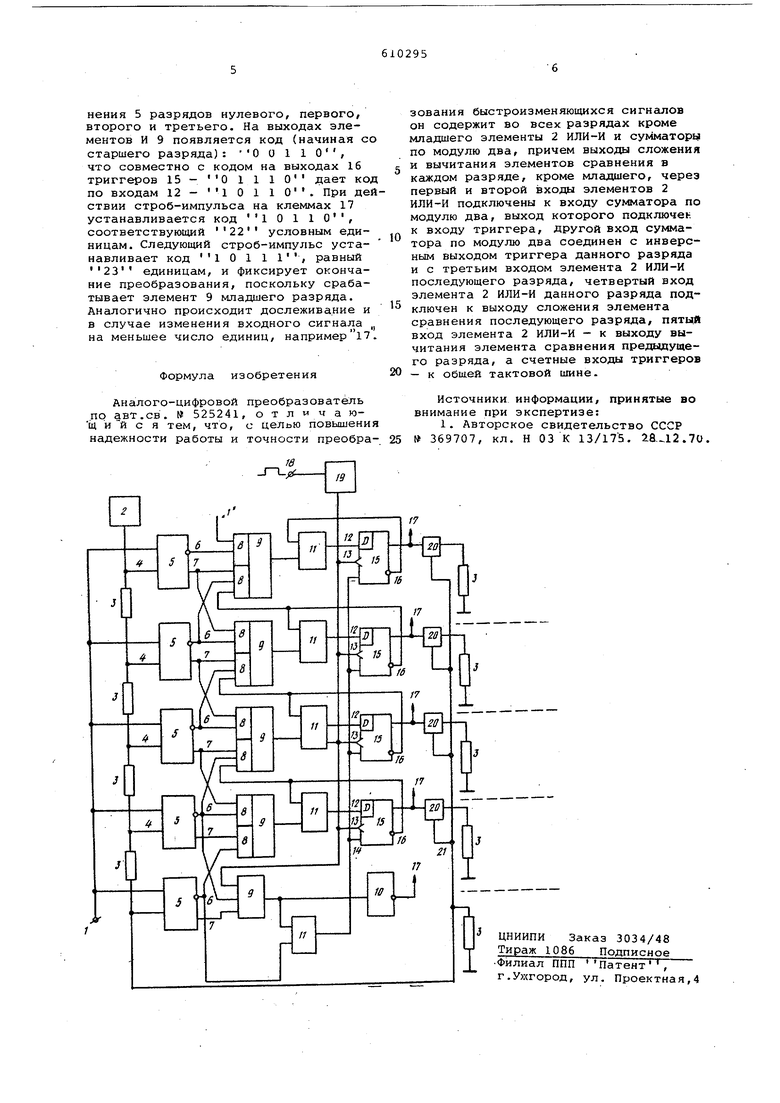

Эта цель достигается тем, что в аналого-цифровой преобразователь, содержащий в каждом разряде схему сравнения с выходами сложения и вычитания, триггер, элементы комбинационной логики И, ИЛИ, цифровые управляемые сопротивления и ключи, подключен ные к выходам триггеров,введены во все разряды, кроме младшего, элементы 2 ИЛИ-И и сумматоры по модулю два причем выходы сложения и вычитания элементов сравнения в каждом разряде кроме младшего, через первый и второй входы элементов 2 ИЛИ-И подключены к входу сумматора по модулюдва, выход которого подключен к входу триггера, другой вход сумматора по моду лю два соединен с инверсным выходом триггера данного разряда и с третьим входом элемента 2 ИЛИ-И последующего разряда, четвертый вход элемента 2 ИЛИ-И данного разряда подключен к выходу сложения элемента сравнения последующего разряда, пятый вход эле мента 2 ИЛИ-И к выходу вычитания элемента сравнения предыдущего разряда, а счетные входы триггеров - к общей тактовой шине. Это исключает сбои в работе преобразователя и повышает точность его ра боты за счет скоростного отслеживани подобных изменений. Надежность работы повышается также и потому, что исключается элемент задержки и критичность к длительности строб-импульсов при сохранении синхронности работы. На чертеже показана структурная схема преобразователя. Она включает клемму 1 преобразователя, источник 2 эталонного тока, весовые резисторы 3, аналоговые входы 4 элемента сравнения, элементы сравнения 5, выходы 6 вычитания элемента сравнения, выходы 7 сложения элемента сравнения, элементы ИЛИ 8, элементы И 9, инвертор 10, сумматоры 11 по модулю два, входы 12 триггеров, счетные входы 13 триггеров, вход 14 установки триггеров, триггеры 15, инверсные выходы 16 триггеров, входные клем мы 17 параллельного кода, клемма 18 управляющего -входа генератора .стробимпульсов, генератор 19 строб-импульсов, аналоговые ключи 20, аналоговый выход 21 аналоговых ключей 20. Весовые резисторы 3, включенные последовательно, имеют распределение весов в соответствии с двоичным законом, т.е. резистор 3, подключенный к источнику 2, имеет вес, равный восьми условным единицам, следующий - четырем, следующий - двум и так далее до одного. Напряжение на входе 4 элемента 5 сравнения младшего разряда определяется состоянием ключей 20 и резистора 3 младшего разряда, суммарный вес которых равен единице. За исходное примем состояние, когда напряжение на клемме 1 равно нулю, а на клемме 18 отсутствует управляющий потенциал. В исходном состоянии все ключи 20 включены и на входах 4 элементов 5 сравнения напряжения предста ены в условных единицах следующим рядом (начиная со старшего разряда) 16; 8; 4; 2У 1 На выходах 16 сигналы соответствуют логической единице. Генератор 19 выключен, на входах 12-14, на выходах элемента сравнения 7 и элемент 9 - сигналы логического нуля. Преобразователь работает следующим образом. При подаче разрешающего потенциала на 1 пемму 18 включается генератор 19 и начинается периодический опрос импульсными сигналами логической единицы триггеров 15 по счетным входам 13. Предположим, что на клемму 1 действует напряжение, величиной 14 условных единиц. Срабатывают все, кроме старшего, элементы сравнения 5. Ь результате на выходах 7 появляется сигнал логической единицы, а на выходах 6 - логический нуль. Строб-импульс с выхода генератора 19 производит опрос триггеров 15,в результате производится запись в триггер 15 четвертого разряда. Это регламентируется состоянием входов и выходов сумматоров по модулю два. В предшествующий появлению первого строб-импульса момент времени со:тояния выходов элементов И 9 (начиная со старшего разряда) : 1 О 1 О . С учетом состояНИИ вь1ходов 16 триггеров 15 (начиная со старших разрядов): 1 1 1 1 1 на выходах сумматоров 11, подключенных к входам 12 триггеров 15, будет код (начиная со старших разрядов): О 1 000. На клеммах 17 триггера 15 четвертого разряда появляется сигнал логической единицы, и ключ 20 отключит цифровое управляемое сопротивление от выхода 21. В результате суммарный вес резистора младшего разряда увеличится пропорционально весу включенного разряда, т.е. на восемь условных единиц. Таким образом, шкала порогов элементовсравнения 5 изменится в соответствии со следующим разбиением в условных единицах напряжения (начиная со старшего разряда): 24; 16; 12; 10; 9 . Действие двух последующих строб-сигналов производит установку триггеров разрядов второго и первого соответст- . венно. В результате шкала порогов элементов 5 сравнения изменится в соответствии со следующим разбиением: 30, 22, 18, 16, 15. Если сигнал на клемме 1 сохраняет свое значение, то в следующем такте сработает элемент,5 младшего разряда, произойдет установка в О через элемент В всех триггеров по входам 14. В данном случае, начиная со старшего разряда, будем иметь код 01110. Если в момент между последним и редпоследним строб-импульсами сигнал а клемме 1 резко изменяется диниц, то срабатывают элементы срав

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровой преобразователь | 1975 |

|

SU525241A1 |

| Аналого-цифровой преобразователь с коррекцией динамических погрешностей | 1976 |

|

SU660240A1 |

| Аналого-цифровой преобразователь | 1979 |

|

SU841110A1 |

| СКОРОСТНОЙ ПРЕОБРАЗОВАТЕЛЬ "АНАЛОГ - ЦИФРА - АНАЛОГ" С БЕСТАКТОВЫМ ПОРАЗРЯДНЫМ УРАВНОВЕШИВАНИЕМ | 2012 |

|

RU2491715C1 |

| Аналого-цифровой преобразователь с самоконтролем | 1980 |

|

SU886236A2 |

| АНАЛОГО-ЦИФРОВОЕ ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО | 1997 |

|

RU2123720C1 |

| Устройство для контроля аналоговых объектов | 1986 |

|

SU1397941A1 |

| Аналого-цифровой преобразователь | 1986 |

|

SU1562971A1 |

| Цифровой измерительный неуравновешанный мост | 1978 |

|

SU789767A1 |

| Аналого-цифровой преобразователь с коррекцией динамических погрешностей | 1979 |

|

SU782147A2 |

Авторы

Даты

1978-06-05—Публикация

1976-04-09—Подача