1

Изобретение относится к вычислительной технике и, в частности, к проектированию многопрограммных MHoronfJOueccopHbix систем, работаюших в реальном масштабе времени.

В мнтпроцессосрных многопрограммных вычислитель Ш1х системах, работающих в реальней, масштабе времени, исключительно Бажной является проблема диспетчеризации, т. е. выбора для исполнения на процессорах наиболее важных программ из очереди программ, ждущих исполнения.

Решение этой проблемы программнь1ми способами для таких, систем является неудовлетворительным, I вследствие больших заТрат машянногб времени на выполнение диспетчерских функций. Требуемый уровень производительности в системах реального времени может быть достигнут при возложении Диспетчерских функций на аппаратуру.

; В вычислительной системе с изменяемой Конфигурацией на аппаратуру, выполнякяпую функции диспетчеризация, накладывается дополнительное требование, состоящее, в том, процессоры, отсоединяемою отсистемы

при реконфигурации, должны исключаться из набора оборудования, участвутс щего ;в диспетчеровании программ. Если при реконфигурации система разделяется на несколько независимых подсистем, то в каждой подсистеме должна выполняться собственная npow. цедура диспетчеризации на оборудован1Ш, BXoJ шшем 1только в эту подсистему. Если жевыдаслительная система должна также обладать повышенной живучестью, то аппаратура,, выполн$пошая функции диспетчеризации, должна быть децентрализована, т. е. распределена среди процессоров. В противном случае отказ одного-устройства, именно того, кото- рое выполняет диспетчерские функции, приводит к выходу из строя всей системы.

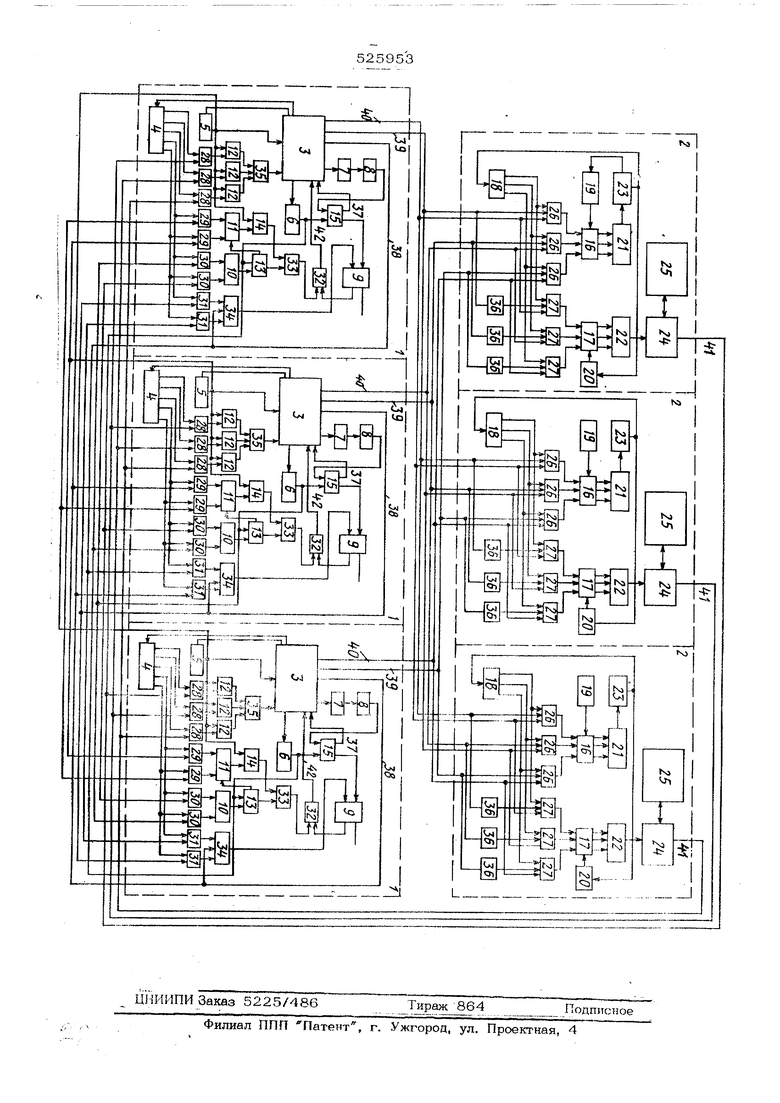

Известны многопроцессорные вычислительные системы с изменяемой конфигурацией, содержащие процессоры и устройства памяти, причем первый выход каждого из процессоров соединен с соответствующим входом )гте -flOi( группы входов других процессоров, второй выход каждого из процессоров соединен с соответствующим входом второй гругаты входов других процессоров, третий выход каждого из процессоров соединен с соответ-. ствукацим входом третьей группы входов дру гих процессоров, четвертый выход каждого из- процессоров соединей с сортветствующим входом первой группы входов каждого из ус ; тройств naMSTTH, пятый выход каждого из про цессоров соединен с соответствующим входо второй группы входов каждого из устройств памяти, первый выход каждого иэ устройств памяти соединен с .соответсвуюишм входом четвертой группы входов каждого из процессоров. Однако этим многопроцессорным систе« мам свойственна сложность организации многопрограммного режима работы при иЗ менении конфигурации и большие дополнительные затраты времени. Цель изобретения - повышение быстро™ действия и надежности системы. Предлагаемая многопроцессорная вычислительная система с изменяемой конфигурацией отличается от известных тем, что в ней каждый процессор содержит операционный блок, регистр конфигурации, регистр noзиционного номера цроцессора, регистр текущего приоритета, регистр заполнения программных очередей, триггер блокировки, nepByiq вторую и третью схемы выбора, груп пу схемы сравнения, первую, вторую, третью и четвертую группы элементов И, элемент И, первый, второй и третий элементы ИЛИ, причем, первый выход операционного блока соединен с входом регистра конфигурации, первая труппа выходов которого соединена с первыми входами соответствующих элемен тов И первой группы элементов И, вторая группа выходов соединена с первыми входами соответствующих элементов И второй, |Третьей и четвертой групп элементов И, ВТ& |рые входы элементов И первой, второй, Третьей и четвертой групп соединены с со™ ответствуюишми входами соответс гвенно четвертой, первой, второй и третьей групп .входов процессора, выходы первой группы элементов И соединены с первыми входами соответствукщих схем сравнения группы схем -сравнения, вторые входы которых сое Динены с первым выходом процессора, с вы ходом регистра позиционного, номера процес™ сора, с первыми входами операционного бпо ка и первой схемы сравнения, а выходы - . соединены с входами первого элемента ИЛИ Выход этого элемента соединен с вторым входом операционного блока, второй выход которого соединен с входом регистра зaпoлнения программных очередей, выход которого соединен с входом первой схемы выбора а ее выход соединен с первым входом второй схемы сравнения, второй вход которой соединен с вторыnvj выходом процессора, с первым входом третьей схемы сравнения м « с выходом текущего приоритета. Первый выход аторой схемы сравнение соедиен с третьим входом операционного бдрка, а второ й выход соединен с едиш{чнь м .входом риггера блокировки, нулевой выход которо- го соединен с первым вдсодом элемента И, выход которого шиной выбора списка соедкнен с четвертым уходом операциошюго, блока, а его третий вьосод 1ШйнШ аанёсения в очередь соединен с третьим выходом працессора и с первым входом второго элемен та ИДИ, другие входы которого соединены с выходами четвертой гру1шы элементов И, а выход соединен с нулевым входом тригге ра блокировки, выходы элементов И третьей группы соединены с входами второй схемы выбора, выход которой соединен с вторым входом третьей схемы сравнения, первый выход которой соединен с первым входом третьего элемента ИЛИ, а второй выход со™ единен с первым входом третьей схемы вы бора, другие входы которой соединены с выходами элементов И второй группы, а выход соединен с вторым входом первой схемы сравнения, выход которой соединен с вторым входом третьего элемента ИЛИ, выход ко торого соединен с вторым входом элемента И, четв зртый, пятый, шестой и седьмой ВЫ ходы операционного блока соединены соответственно информационной шиной с четвертым выходом процессора, шиной привилегИ рованного режима с пятым выходом процес- сора, с входом регистра позиционного номе- ра процессора и с входом регистра текущего приоритета. Каждое устройство памяти содержит запоминающий блок, блок управления выборкой, блок снстемпых операций, регистр конфигу™ рации, регистр пози хионного номера, регистр логического номера, первую и вторую cxeMbj сравнения, первый и второй приоритетные коммутаторы, первую и вторую группы эл& -ментов И, группу элементов НЕ, причем, первый выход блока системных операш1й со единен с входами регистра логического но мера и регистра конфигурации, выходы кото, рого соединены с nepBbihysi-i входами соответ ствующих элементов И первой и второй групп, вторые входа которых соединены с соответствующими входами первой rpjTini.s входов устройства памяти, третьи входы первой группы элементов И непосредственно,а вто рой группы элементов И через элементы НЕ соединены с соответствующими входами вто рой группы входов устройства памяти, выхо ды первой группы элементов И соединены с первыми входами первой схемы сравнения, ВЫХОД. которой соеяинекы с входами первоГО приоритетного коммутатореj выход кого- рого соединен со входом блока системных «операций, второй выход которого соединен с входом регистра позиционного номера, выход которого соединен со вторым входом первой схемы сравнения, выходы второй группы эле ментов И соединены с первыми входами второй схемы сравнения, второй вход которой соединен с-Тбых55оН7регистра логического н мера, а выходы соединены со входами второго приоритетного коммутатора, выход которого соединен с входом блока управления выборкой, связанного с запоминающим блоком, выход блока управления выборкой соединен информационной шиной с выходоч устройства памяти. На чертеже дана структурная электри ческая схема многопроцёссорной вычислительной системы с изменяемой конфигурацией. Предлагаемая многопроцессорная вычис лительная система содержит процессор 1, |модуль 2 оперативной памяти (устройства памяти), операционный блок 3, регистр 4 конфигурации процессора, регистр 5 позиционного номера процессора, регистр 6 текущего приоритета, регистр 7 заполнения программных очередей, первую схему 8 выбора (старшего номера), триггер блоюфовки 9, вторую схему 10 выбора (младшего приоритета), третью схему 11 выбора (младшего номера), схемы 12-17 сравнения (группа схем сравнения 12), регистр 18 конфигурации памяти, регистр 19 позиционного номера памяти, регистр 20 логического номера памяти, первый и второй приоритетные коммутаторы 21, 22, блок 23 системных операций, блок 24 зггфавления выборкой, запоминающий блок 25, группы 26-31 элемен тов И, элемент И 32, элементы ИЛИ 33-3 группу 36 элементов НЕ, шину 37 прерывания, шину 38 занесения в очередь, шину 39 привилегированного режима, информационные шины 40 процессора, информационные щины 41 памяти, шину 42 выборки списка. Многопроцессорная вычислительная систе ма содержит несколько процессоров 1 и не сколько модулей памяти 2. Каждый процессор имеет регистр 5 позиционного номера процессора (выполненный, например, на тум блерах), который устанавливается постоянным для данной вычислительной системы. Все процессоры имеют различные позишюн™ ные номера. Каждый модуль памяти 2 также имеет .регистр 19 позициоаногх) номера памяти, ко |Торый в ка.жд6м модуле устанавливается пос Тояйным для данной вычислительной систе-j мы. Все модули памяти 2 имеют различные позиционные номера. Каждый модуль памяти | 2 имеет регистр 20 логического номера па-в мяти, содержимое которого определяет, к 1сакому модулю памяти 2 адресовано обращение процессора 1. Конфигурация многопроцессорной системы .определяется содержикалм регистра 4 конфиРураУошпроцессора и регистра 18 конфигурации памяти. Если все разряды этих регистров установлены в положёние I, то система образует один комплекс, в состав которого входят все процессоры 1 и все модули памяа-и 2. Связь между ними для обмена информацией в этом случае проиэ- I водится следующим образом. Операционный блок 3 процессора 1 возбуждает .-на информационных шинах 40 процессора адрес ячейки памяти, к которой производится обращение, я информаш ю, которую необходимо записать по указанному адресув случае one- I рации записи, а также позишюн1{ый номор из регистра 5 позиционного номера процессора. При этом на шине 39 привилегирова -, ного режима сигнал отсутствует и вых6дь1 группы 36 элементов НЕ модулей памяти 2 значение . Сигналы с информационных шин 40 процессе ора проходят при указанных выше условиях через первую группу 27 элементов И всех модулей памяти 2 и попадают на входы вторых схем 17 сравнения, которые сравнивают старшие разряды адреса с содержимьц регистра 20 логического номера памяти и, в случае совпадения, коммутируют входную ;информацию на вход второго приоритетного коммутатора 22. Второй приоритетный коммутатор 22 в случае одновременного обращения к модулю памяти 2 нескслыоо: процессоров 1 выбирает и коммутирует на свой выход информацию с одного из входов по позиционному приоритету. Блок 24 т1раБления выборкой производит обращение к запоминающему блоку 25 по принятокту а.цресу и коммутирует на информационные шины. 41 кюдуля позиционный номер процессора из соответствующих разрядов с выхода второго приоритетного коммутатора 22. Ситна.гы с информационгш1х шин модуля 41 проходят через первую группу 28 элементов И процессора 1 я поступают на входы схем 12 сравнения, где сравниваются с содержикллм регистра 5 позиционного : номера гфоцессо1 а. Совпадение номеров означает, что модуль памят.и 2 принял запрос на обращение от данного процессора 1 и прист111ил к выполнению операции, заданной процессором. При этом, в случае операции записи, схема сравнения 12 через первый -;,;эл;емент ИЛИ 35 вьшает сигнал в onepaiui. онный блок 3, фиксирукмций окончание сеанса связи процессора с модулем памяти 2. При выполнении операции чтения модуль па МИТИ 2 возбуждает на информациошльос 5 Haxj41 памятл кроме позищ онногчз номера процессора также прочитанную информацию из указанной- ячейки запоминающего 6ло.ка25. Схема 12 сравнения через эдвмент ИЛИ 35 коммутирует информацию с ккформаимо№кых IQ шин 41 г1амяти в операцконный блок 3, ко-. торый: по одной из информационных шин 40 процессора сигнализирует модулю гхамяти 2 об окончании сеанса связи.

Многопрограммная работа в данной мна« 15 гопроцессорной системе организуется сие ;дующим образом. ,

i Операционная сисэема, размещая прозграмй. |мы в памяти, присваивает .каждой программе приоритет (возможно jijjHCBoeiiKe одинаково«.2о |го приоритета нескольким программам)., Для ,;.каж.дого .из возможньгх значений приоритета операционная система формирует йчеред) :программ, при часть очередей может быть пустой, если в текущий момент в теме отсутствуют йаявзш на выполнение про грамм с дан1пыми приоритетам -. Для опреде--. ления не пустых очередей программ опера « ционная система записывает в факсиротзанной ячейке памяти (например, в модуле с иуле« 30 вым логическим номером) едикиго т в разря™ дах, соответствующих тш пустым .тм,

I При выполнении гфограм; ГЫ на процеосо--ре- 1 в ре.гистр 6 текущего приоритета за-- д носится приоритет выполнгемой программьи После окончания рыиолнег-шя nporpaNSMb ре-гистр. текущего пр.иорктета Ггэситс.я. Ллшарат фа процессоров непрерывно сравк-янает , приоритеты : рьшопияемых .}о гюех о процессорах и тот про.тессЬр, гья програглгла имеет сэмый икз.к.кй лркоркт-ет , кгтювктс канйидатом на прерываггае. Этот процессор проверяет, есть ли в синске очередей про-;Грамма с приоритетом более -высоким, чем g та, которую orf испо;шйет„ Если такая грамма есть, то процессор каяккиВт на яра™ рыванке прерьгвает исполнение текущей програмгА,, заносит ее в сгшсок очередей и вы-бнрает из списка шет исполнения ггрограм му jjj с высшим приоритетом.

Работа аппаратуры при &том Ррог чШЛгсит- ся следующим образом.

При выполнемш текущей п|:юг--р« тмьг Г я:ерационнь й блок 3 з лноскт со приорит&г в щ 6 текущего npjioji rreia. Ищпрт-вт мя з регкегра текущего приоритета квжпог) процессора поступает перез группу :О

;а втопыо схемь; . О выбора

элбмеитов

(младщего ггркоритета) прокессоров .1.,Г

В Кс«кдом upoueccoj 3 втора.-.г схема 10 вы бора (младшего приоритета) осушествл.Еет сравнение текущих приоритетов других . цессоров и коммутирует на вы.ход код мпадшего из сравниБаемьгх текушш: приори тетов. При равенстве кодов -екушж;- приоря- тегов на входдх. вт-орой IW выбора на е.е вькгсод комм тируе1:ч;я код сравниваемых, текущих приоритетов. Код с выхода второй схемы 10 вьГ5ора ностртает на вход трегь ей сжемы 13 сравнения (приоритетов) для сравнения с содержимьгм регистра 6 теку щего приоритета данного процессора. Если содерм1 мое этого регистра текуи.1ег5 прио. .ритета данного процессора кода., зырвбатывйвмого второй схемы 10 выбора, то долшьгй процессор Еыполнйетзадачу с caMbiM низким приоритетом и становктся К2нд.адатом на прерывание При эт-ом третья схема 13 с|эа.внения вырабатывает сигнал гш CBO&hi втором выходв, который чвреэ трв тий эл8ме.1т или 33 HOCTyiiaeT на вход эле.лента И 32.Если содержимое регистра 6 тегсущего приоритета данного процессора больше кода, вырабатываемого второ.й схемой 10 эыборн, то данньй процессор пе ;шляется кандидн--том на прёрывакие и первый к второй выходы третьей схемы 13 сравпелия равны нулю I Есаи содержимое регистра 6 текущех о приоритета равую коду мльдшего текущего Приоритета, то это означает, два ишт болеа процессора 1 кпитчлняют программы одинакового приорктета, В этом случае процессор кандидат пя прорызатгре вь бкрается по КЕладпему (Тоз.) ж.меру трегьП. Кчи схемами 1 выбор;-; (млядшего номера.) и скемамй J-- срввке ;.;и;, работаiouiK vrn вив-лог. 0 i-infJopa и сяе/лам 13 cpaBHGHHS соогвегеГ-;;ййно„

Г1р.и этом сшнал на ныхопе тр8«« ьей сясмь; 13 с:равкени.я равен , а ка ее первом пылоде вырабатьтвчтся сагпап, включающий треть схему 1.1 выбора, на I В5С.ОД которой p.fopyio г-руппу 29 э.ггв ментов И sTopTjTiaeT ин{1х:фм;-1ция с выходов . регистров 5 позииионт-л : номеров ггрояессоров J., Код по.з пуюнного тюмера с 11ы;:ода третьей схемь выбора 11 nc-cTjTJaeT ка вхоп первой cxfif fbi С;адвггонп 14, те с| авяивается с содр-р; шмым POJ-HCITр« 5 позйдконпого номера паииогт) np-Hiec-сора .1,

Нсли соиержкиое регистра 5 позкш10г1Г1 го номера прош ссора меньше кода м.;)«л.:|гс;ч ЯО.ЭКП.ЙО1ШОГО номера, то схома cpfiir-. кенкя 11 ibipfmaTbinanr сих-пял, который Третий злемотгт 1-1/1И 3 поступает- на влод элемента И 32. 11рн этом, сели триг-.гер 9 6jiOKHjDOBiai (трерьшаний) стоит в по- ложении О то элемент И 32 возбуждает сигнап на шв:не 42 ныбор1Ш списка, соедаг- недыый с входом операционного блока 3. Операциош1ый блок 3 выбирает из naM.si ти в регистр 7 запсшнения гфограммньхх оче редей содержимое фшссированной ггчейки, хра нящей указателиjне пустых очередей программ. Схема выбора 8 (старшего номера) Ъыбирает из регистра 7 (заполнения про- (граммных очередей старший но мер Ггрйори. тета программ, находжщосся в списке очередей,. и передает этот помер на вход вто« рой схемы 15 сравнения (приоритетов) ко .торая сравнивает .его с содерлсиг/я-лм регис- 1тра 6 текущего приоритета. Есаи содерлси мое регистра 6 тею/щего приоритета мень-. ше кода приоритета ирограмгугы со савршим приоритетом из списка очередей, то вторая схема сравнения 15 вырабатывает С1сгнап на шине 37 прерывания. При этом процес- сор 1 прерывает выполне1-ше текуш,ей про.граммы и заносит ее в список очередей программ 1 с приоритетом, соответствующим содерн имому регистра 6 текущего приоритета. Затем процессор 1 выбирает из списка очередей программу с паивысшим приоритетом и передает ее приоритет в регистр 6 текущего приоритета и прист ттает к выполнению этой програм1-.ш1. Если содерясимое регистра 6 те5с;.тлего приоритета болыие кода приорагге-га програм« мы со старшим приоритетом из очереди, то это означает, что в очереди программь кме ют приоритет I меньш5:й, чем приоритет исполняемой ггрограммы. При этом вторая схема 15 сравнения вырабатьвает скшал, устанавливающий в прпожение триггер бло1ШрйВ1а1 S; к&лорый эахрыйает опе1ло;гг И 32. Триггер бло1шров2ш 9 сбрасывается в положешю О при занесенин .гпобым процессором 1 программы в список очередей. При этом процессор 1 вырабатыВает сигь нал на Ш1ше 38 занесе шя в очередь, который костртает tia. вход собственного второго элемента ИЛИ 34 л через четвертую грул.« зу И 31 элемектоз fa входьз элемектов ИЛ 34 другьх нроцессороз 1о С ВЫ;СОДБ элемен та И,Г1.И 34 скгаа.к постуаает на вход гаше-- йЖй триггера блО- счровтш 9,, ИоменэнЕЗ Т 5нфв7урятт11к скстемт / уншн iляeтc peг ir;тpaмн 4 кокф рурагг:щ;: прсцес-. соров и регкстраь.13 18 конфигурадлк . Установка регксгра 4 конфиг фалщк процессора ПРОИЗВОДИТСЯ оиерйшюкшлм блотсом 3« Часть разрядов рег истра 4 когфягурадкк Лроиессора служит .чля отключен от npoixec соров 1 модулей памй;гк 2, Осумдествллется это отключений с лсглсщыо запинания первой жтов И, Другаз часть разрядов регистра 4 конфигуращш процессора служит для исключения о продессоров 1 из многопрограммной систе к-гы работы. При siTOM вторая группа 29 эл&меытов И служит для исключения отключаемого процессора из процедуры сравнения по зкщгонных номеров, третья группа 30 элементов И . для исключения из процедуры сравнеаия текущих приоритетов и четвертая группа 31 элементов И для исключения процеосоров 1 из процедуры сброса триггеров блоKHpoBKji 9. Регистр 18 конфигуращш памяти слуjiaiT для отключения от модулей памяти 2 гфоцессоров 1. Установка регистра 18 конфигурации памят15 производится операдион- , ным блоком 3. одного из процессоров 1. При этом операционный блок 3 вырабатывает сигнал на шине 39 привилегированного режима и в модулях памяти 2 «ткрываются соответствующие группы 26 элементов И, а группа 36 элементов НЕ закрывает группу 27 элементов И. В привилегированном режиме работы с модулями 2 оперативной памяти производится по поз1 ционному номеру, хранимому в регистре 19 позишюнного номера памяти. При этом старшие разряды адреса через первую группу 26 элементов И поступают на вход схем сравнеш1я 16, где сравниваются с соде регистра 19 позиционного номера памяти, В том модуле оперативной памяти, где эти номера совпадаюа схема сравнения 16 передает информахшю на ЕКОД приоритетного з-соммутатора 21, который в случае одновременного обращения нескольких процессоров 1 выбирает и коммутирует на свой выход информацию с одного извходов по позлниокному приоритету,I Блок 23 системных операций в соответ-; ствии с пр1пгятой ин4юрмащ1ей управляет yo-i танЪвкой регистра 18 конфигурации памяти и регистра 20 логического номера памяти. Изменяя содержимое регистра 4 конфиг фа.щш процессора, регистра 18 конфигуращш памяти, и регистра 20 логического номера памяти, можно отключать неисправные процессоры 1 к модули 2 оперативйой { пзмятИ} а таюке форгуцфовать отдельные мно| гопрограммньш, многопроцессорные подсио- Teivibin Например, можно организовать две такие иодскстеь&т, установив попарно ош наковые логические комер модулей памяти 2, от- i ключЕЗ с регистров 18 конфигура-J шги памяти i.Tpoiieccopbi одной подсистем1-11 от модулей оперативной памяти 2 другой по деисте;vibi п отключив с помошыо регист- ; процессора модули од-; . процессоров другой под-/Ч ной подсистемы от системы и процессоры одной подсистемы от аппаратуры многопрограммной работы другой подсистемы. При этом аппаратура авто матически обеспечивает многопрограммный .режим работы каждой подсистемы. Формула изобретения Многопроцессорная вычислительная система с изменяемой конфигурацией, содер жащая процессоры и устройства памяти, при чем первый выход каждого из процессоров соединен с соответствующим входом первой группы входов других процессоров, вторЬй выход ка кдого из процессоров соединен с соответствующим входом второй группы ВйО- дов других процессорюв, третий выход каждо го из процессоров соединен с соответствующим входом третьей группы входов других процессоров, четвертый выход каждого из процессоров соединен с соответствующим вх дом первой группы входов каждого из устройств памяти, пятый выход каждого из процессоров соединен с соответствующим входом второй группы входов каждого из устройств памяти, первый выход каждого из устройств памяти соединен с соответствую- щим входом четвертой группы входов каждого из процессоров, отличающая- .с я тем, что, с целью повышения быстро действия и надежности системы, каждый процессор содержит операционный блок, ре гистр конфигураш{и, регистр позиционного номера процессора, {югистр текущего прио ритета, регистр заполнения программШ)1х оче редей, триггер блокировш}, первую, вторую и третью схемы выбора, группу схем сравнения, первую, вторую и третью схемы сраБ нения, первую, вторую, третью и четвертую группы элементов И, элемент И, первый, второй и третий элементы ИЛИ, причем, пер вый выход операционного блока соединен с входом регистра конфигурации, первая груп па выходов которого соединена с первыми .-входами соответствующих элементов И перБОЙ группы элементов И, вторая группа вы« ходов соединена с первыми входами соответ ствующих элементов И второй, третьей и четвертой групп элементов И, вторые входы элементов И первой, второй, третьей и чет вертой грутш соединены с соответствующими входами соответственно четвертой, первой, второй и третьей групп входов процессора, выходы первой группы элементов И соедине ны с первыми входами соответствующих схе сравнения группы схем сравнения, вторые входы которых соединены с первым выходом процессора, с выходом регистра позиционног номера процессора, с первыми входами one рационного блока и первой схемы сравнения, 5 53 --52S, - а выходы - соединены с входами первого элемента ИЛИ, выход которого соединен с вторым входом операиионного. блока, второй выход которого соединен с входом регистра заполнения программных очередей, выход которого соединен с вд;одом первой схемы j выбора, выход которой соединенг первым входом второй схемы сравнения, второй вход которой соединен с вторым выходом процес- сора, с первым входом третьей схемы сравнения и с выходом егистра текущего прио- ритета, первьЕЙ выход второй схемы сра&нения соединен с третьим входом операционного блока, а второй выход соединен с единичным входом триггера бло1шровки, нулевой выход которого соединен ,с первым входом элемента И, выход которого шиной выбора списка соединен с четвертым входом опера- ционного блока, третий выход которого ши- : ной занесения в очередь соединен с третьим ; выходом процессора и с первым входом второго элемента ИЛИ, другие входы которого соединены с выходами четвертой группы элеметов И, а выход соединен с нулевым входом триггера блокировки, выходы элементов И третьей группы соединены с входами второй схемы выбора, выход которой соединен со вторым входом третьей схемы сравнения, первый выход которой соединен с первым входом третьего элемента ИЛИ, а второй выход соединен с первым входом третьей схемы выбора, другие входы которой соеди- 1 нены с выходами элементов И второй группы, а выход соединен с вторым входом пер- вой сравнения, выход которой соеди- , нен с вторым входом третьего элемента ИЛИ, выход которого соединен с вторым входом элемента И, четвертый, пятый, шестой и седьмой выходы операционного блока соеди нены соответственно информационной шиной с четвертым выходом процессора, шиной привилегированного режима с пятым выходом процессора, с входом регистра позици- : онного номера процессора и с входом регисЧ тра текущего приоритета, а каждое устрой- I ство памяти содерл ит запоминающий блок, | блок управления выборкой, блок системных | операций, регистр конфигурации, регистр позиционного номера, регистр логического но мера, первую и вторую схемы сравнения, первый и второй приоритетные коммутаторы, первую и вторую группы элементов И, груп-ч пу элементов НЕ, причем, первый выход I блока системных операций соединен с вхо : дами регистра логического номера и регис- тра конфигурации, выходы которого соеди- нены с первыми входами соответствующих элементов И первой и второй , вторые входы которых соединены с соответствую щими входами первой группы входов устройства памяти, третьи входы первой группы элементов И непосредственно, а второй грушхы элементов И через элементы НЕ соединены с соотеетствуняоими входами второй груш1ы входрв устройства памяти, выходы первой группы элементов И соединены с первыми шсодами первой схемы сравнения, вы;ходы которт)й соединены с входами первого приоритетного коммутатора, выход которого соединен с входом блока системных операций, второй выход которого соединен с «кодом регистра позиционного номера,

выход которого соединен с входом первой схемы сравнения, выходы второй группы элементов И соединены с первыми входами второй схемы сравнения, второй вход которой соединен с выходом регистра логического номера, а выходы соединены с входами второго приоритетного 1Й)ммутатс ра, выход которого соединен с входом блока управления выборкой, связанного с запо минаюошм блоком, выход блока управления выборкой соединен информационной шиной с выходом устройства памяти.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многопроцессорная вычислительная система | 1977 |

|

SU670937A1 |

| Устройство сопряжения процессоров в многопроцессорной вычислительной системе с изменяемой конфигурацией | 1984 |

|

SU1259278A1 |

| Устройство для распределения заданий процессорам | 1985 |

|

SU1291983A1 |

| Устройство для обмена информацией | 1983 |

|

SU1198528A1 |

| Процессор | 1983 |

|

SU1213485A1 |

| Микропрограммное устройство управления с контролем | 1983 |

|

SU1136162A1 |

| Устройство для сопряжения оперативной памяти с внешними устройствами | 1981 |

|

SU993237A1 |

| Мультиплексный канал | 1980 |

|

SU924693A1 |

| Устройство для сопряжения процессоров в вычислительной системе | 1985 |

|

SU1332327A1 |

| Многоканальное устройство для обмена информацией | 1984 |

|

SU1359781A1 |

Авторы

Даты

1976-08-25—Публикация

1974-05-29—Подача