I

Изобретение относится к вычислительной технике и, в частности, к проектированию многопрограммных, многопроцессорных систем, работающих в реальном масштабе времени.

Цель изобретения - повьппение надежности и живучести системы.

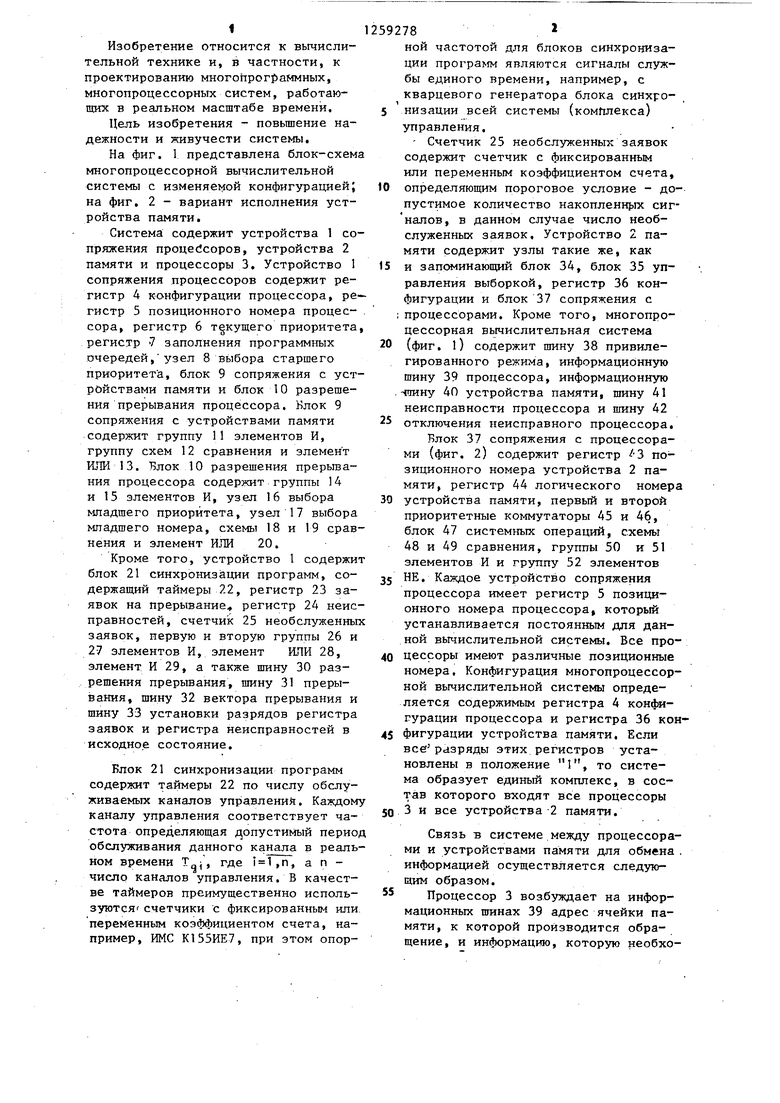

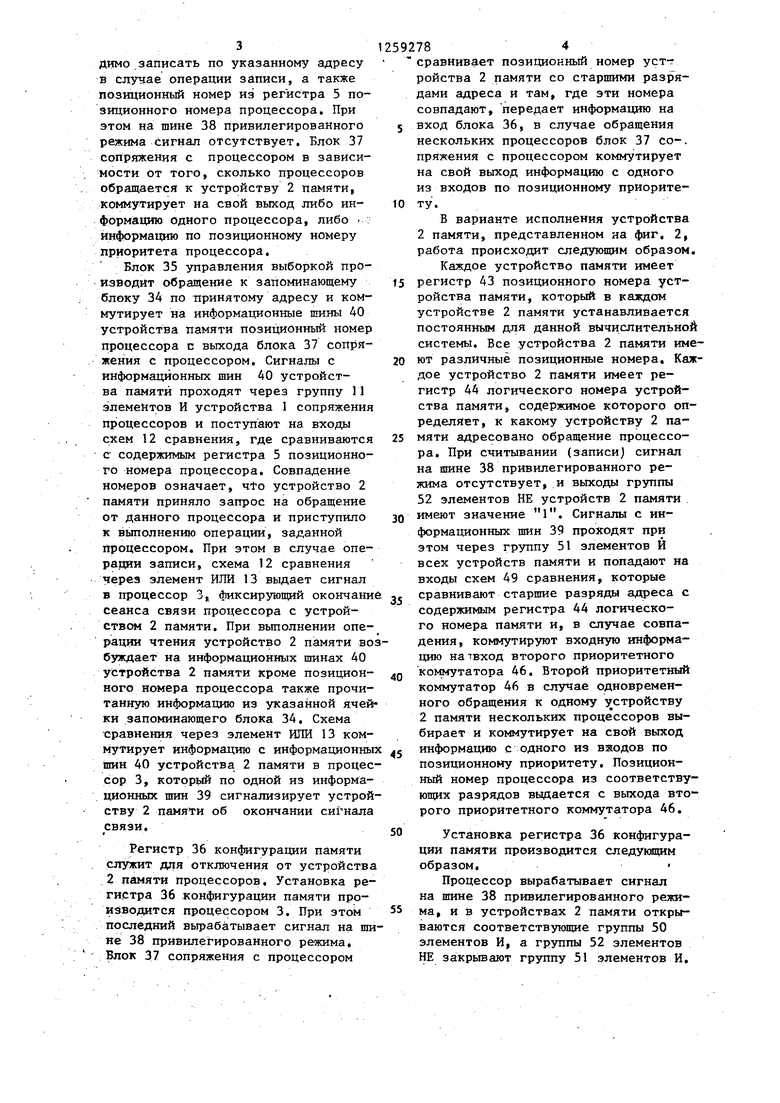

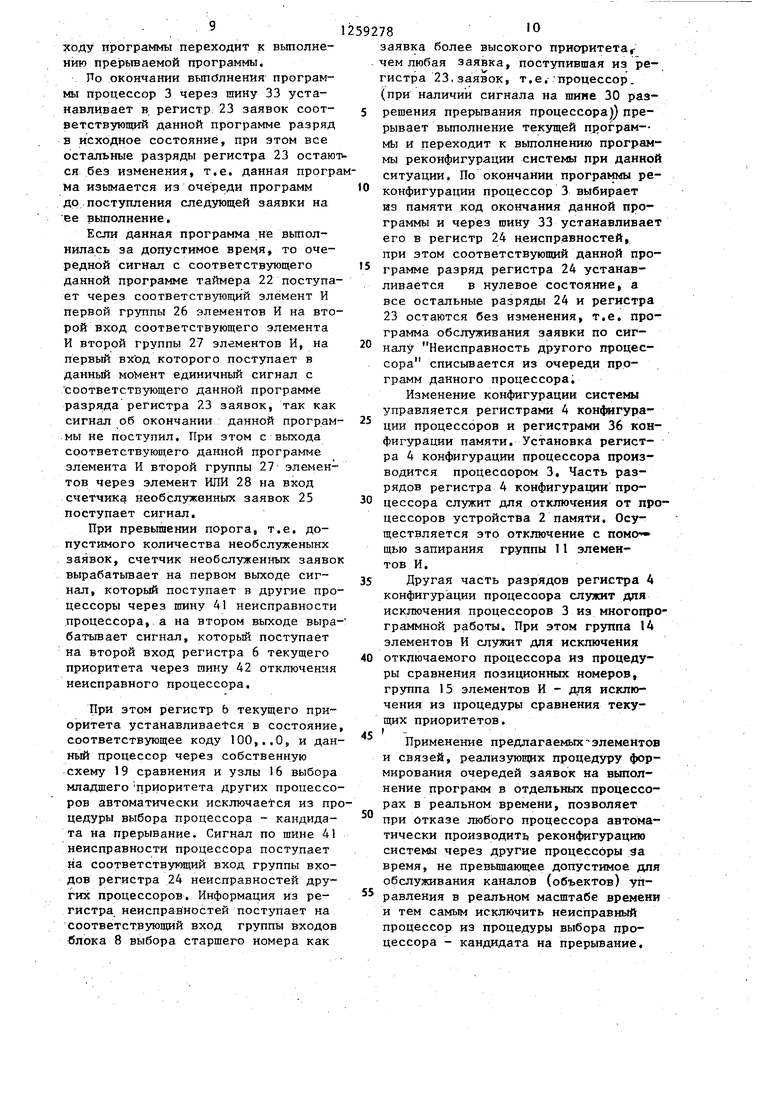

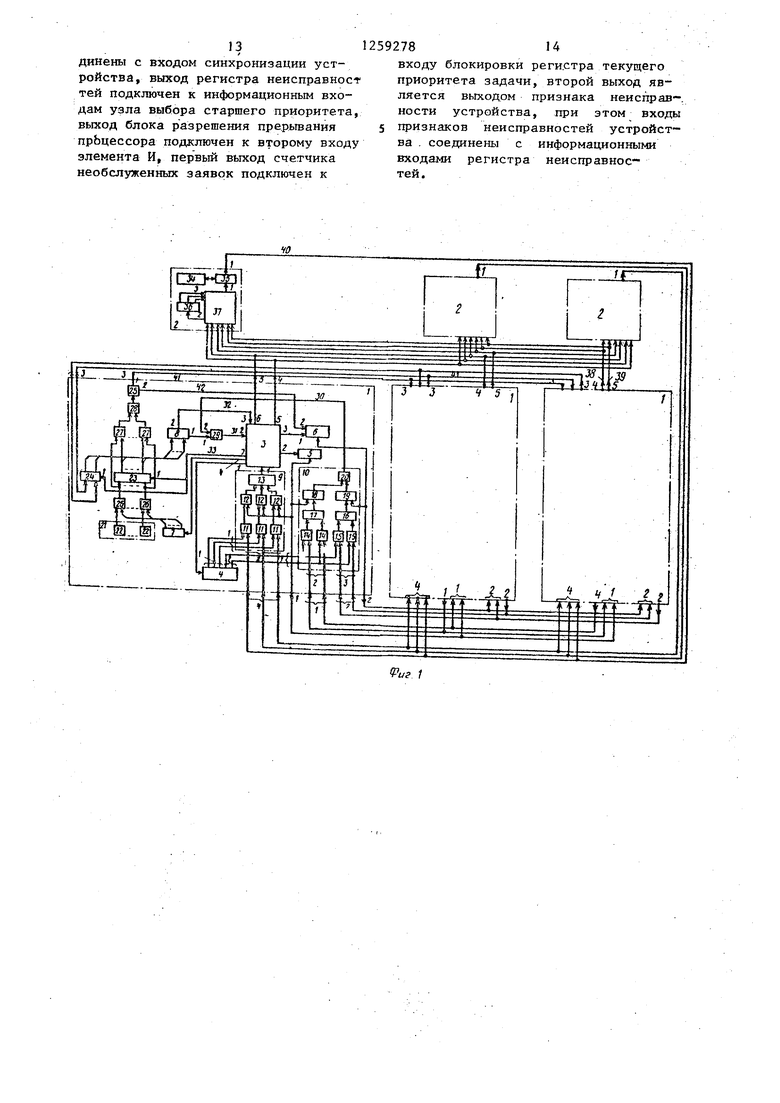

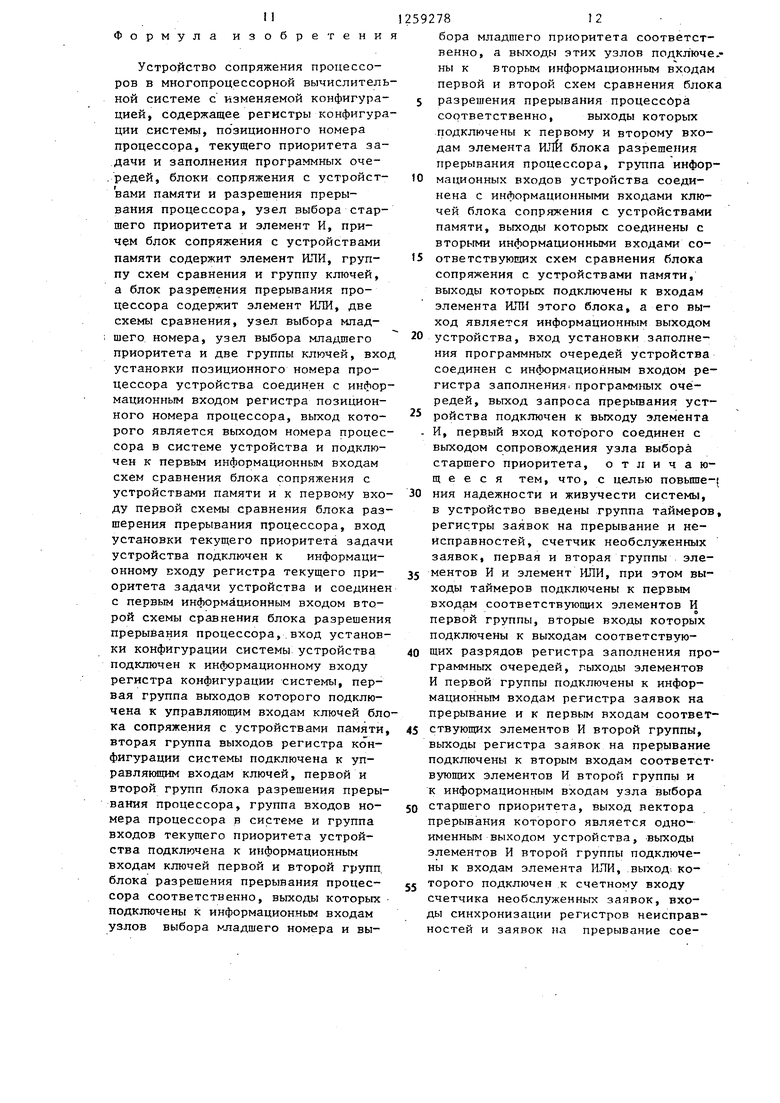

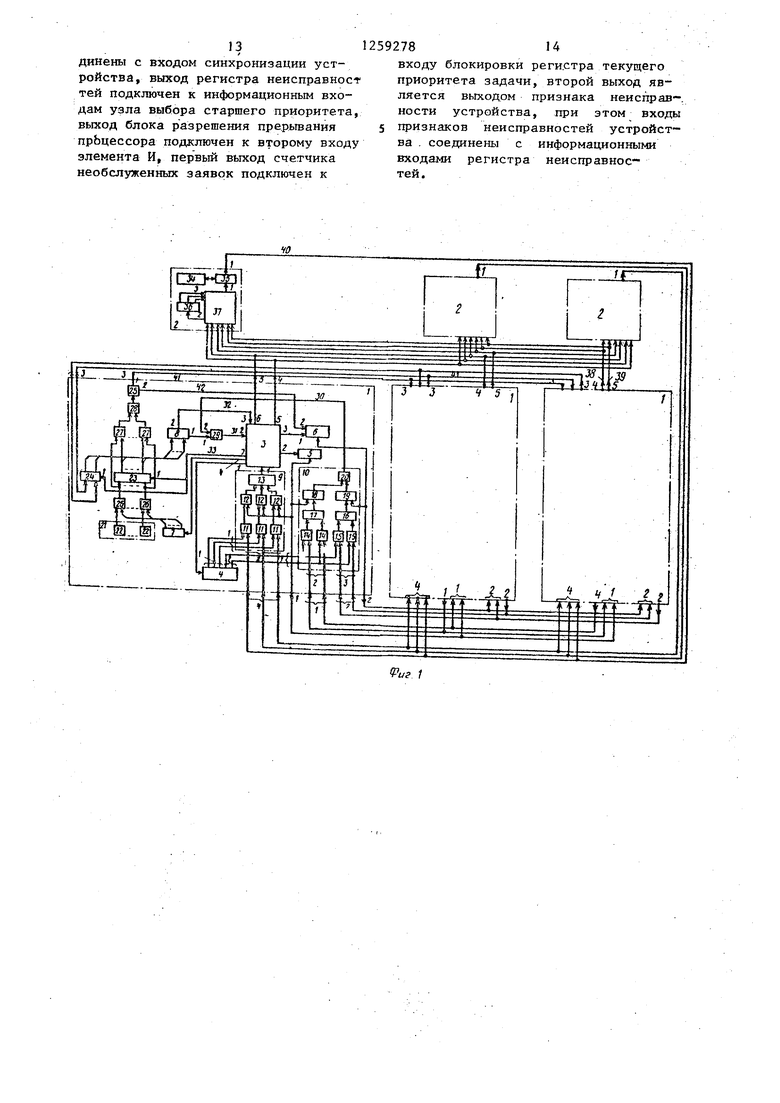

На фиг. 1 представлена блок-схема многопроцессорной вычислительной системы с изменяемой конфигурацией; на фиг. 2 - вариант исполнения устройства памяти.

Система содержит устройства 1 сопряжения процейсоров, устройства 2 памяти и процессоры 3, Устройство 1 сопряжения процессоров содержит регистр 4 конфигурации процессора, регистр 5 позиционного номера процессора, регистр 6 текущего приоритета, регистр 7 заполнения программных очередей, узел 8 выбора старшего приоритета, блок 9 сопряжения с устройствами памяти и блок 10 разрешения прерывания процессора. Блок 9 сопряжения с устройствами памяти содержит группу 11 элементов И, группу схем 12 сравнения и элемент ИЛИ 13. Блок 10 разрешения прерьша- ния процессора содержит группы 14 и 15 элементов И, узел 16 выбора младшего приоритета, узел 17 выбора младшего номера, схемы 18 и 19 сравнения и элемент ИЛИ 20.

Кроме того, устройство 1 содержит блок 21 синхронизации программ, содержащий таймеры 22, регистр 23 заявок на прерывание регистр 24 неисправностей, счетчик 25 необслуженных заявок, первую и вторую группы 26 и 27 элементов И, элемент ИЛИ 28, элемент И 29, а также шину 30 разрешения прерывания, шину 3 прерывания, шину 32 вектора прерывания и шину 33 установки разрядов регистра заявок и регистра неисправностей в исходное состояние.

Блок 21 синхронизации программ содержит таймеры 22 по числу обслуживаемых каналов управлений. Каждому каналу управления соответствует частота определяющая д опустимый перио обслуживания данного канала в реальном времени Т„, где ,п, а п - число каналов управления. В качестве таймеров преимущественно используются счетчики с фиксированным или переменным коэффициентом счета, например, ИМС К155ИЕ7, при этом опор25

59278

ной частотой для блоков синхронизации программ являются сигналы службы единого времени, например, с кварцевого генератора блока синхро5 низации всей системы (комЛпекса) управления.

- Счетчик 25 необслуженных заявок содержит счетчик с фиксированным или переменным коэффициентом счета,

10 определяющим пороговое условие - допустимое количество накопленщ гх сиг- налов, в данном случае число необслуженных заявок. Устройство 2 памяти содержит узлы такие же, как

15 и запоминающий блок 34, блок 35 управления выборкой, регистр 36 конфигурации и блок 37 сопряжения с : процессорами. Кроме того, многопроцессорная вычислительная система

20 (фиг. О содержит шину 38 привилегированного режима, информационную шину 39 процессора, информационную .-пину 40 устройства памяти, шину 41 неисправности процессора и шину 42 отключения неисправного процессора. Блок 37 сопряжения с процессорами (фиг. 2) содержит регистр 3 позиционного номера устройства 2 памяти, регистр 44 логического номера

30 устройства памяти, первый и второй приоритетные коммутаторы 45 и 46, блок 47 системных операций, схемы 48 и 49 сравнения, группы 50 и 51 элементов И и группу 52 элементов

35 НЕ. Каждое устройство сопряжения процессора имеет регистр 5 позиционного номера процессора, который устанавливается постоянным для данной вычислительной системы. Все про40 цессоры имеют различные позиционные номера. Конфигурация многопроцессорной вычислительной системы оцреде- ляется содержимьш регистра 4 гурации процессора и регистра 36 кон45 фигурации устройства памяти. Если все разряды этих регистров установлены в положение 1, то система образует единый комплекс, в состав которого входят все процессоры

50 3 и все устройства 2 памяти.

Связь в системе между процессорами и устройствами памяти для обмена . информацией осуществляется следующим образом.

55 Процессор 3 возбуждает на информационных шинах 39 адрес ячейки памяти, к которой производится обращение, и информацию, которую необхо3

димо записать по указанному адресу в случае операции записи, а также позиционный номер из регистра 5 позиционного номера процессора. При этом на шине 38 привилегированного режима сигнал отсутствует. Блок 37 сопряясения с процессором в зависимости от того, сколько процессоров обращается к устройству 2 памяти, коммутирует на свой выход либо информацию одного процессора, либо Информацию по позиционному номеру приоритета процессора.

Блок 35 управления выборкой производит обращение к запоминающему блоку 34 по принятому адресу и коммутирует на информационные шины 40 устройства памяти позиционный номер процессора с выхода блока 37 сопряжения с процессором. Сигналы с информационных шин 40 устройства памяти проходят через группу 11 элементов И устройства 1 сопряжения процессоров и поступают на входы схем 12 сравнения, где сравниваются с содержимым регистра 5 позиционного номера процессора. Совпадение номеров означает, 4to устройство 2 памяти приняло запрос на обращение от данного процессора и приступило к вьшолнению операции, заданной процессором. При этом в случае операции записи, схема 12 сравнения через элемент ИЛИ 13 выдает сигнал в процессор 3, фиксирующий окончани сеанса связи процессора с устройством 2 памяти. При выполнении операции чтения устройство 2 памяти вобуждает на информационных шинах 40 устройства 2 памяти кроме позиционного номера процессора также прочитанную информацию из указанной ячейки запоминающего блока 34. Схема сравнения через элемент ИЛИ 13 коммутирует информацию с информационны шин 40 устройства 2 памяти в процессор 3, который по одной из информационных щин 39 сигнализирует устройству 2 памяти об окончании сигнала связи.

Регистр 36 конфигурации памяти служит для отключения от устройства 2 памяти процессоров. Установка регистра 36 конфигурации памяти про- изводатся процессором 3. При этом последний вырабатывает сигнал на шине 38 привилегированного режима, Блок 37 сопряжения с процессором

592784

сравнивает позиционный номер устройства 2 памяти со старшими разрядами адреса и там, где эти номера совпадают, передает информацию на 5 вход блока 36, в случае обращения нескольких процессоров блок 37 со-, пряжения с процессором коммутирует на свой выход информацию с одного из входов по позиционнс гу приорите10 ту.

В варианте исполнения устройства 2 памяти, представленном на фиг. 2, работа происходит следующим образом. Каждое устройство памяти имеет

15 регистр 43 позиционного номера устройства памяти, который в каждом устройстве 2 памяти устанавливается постоянным для данной вычислительной системы. Все устройства 2 памяти име20 ют различные позиционные номера. Каждое устройство 2 памяти имеет регистр 44 логического номера устройства памяти, содержимое которого определяет, к какому устройству 2 па25 мяти адресовано обращение процессора, При считывании (записи) сигнал на шине 38 привилегированного режима отсутствует,.и выходы группы 52 элементов НЕ устройств 2 памяти

имеют значение 1. Сигналы с информационных шин 39 проходят при этом через группу 51 элементов И всех устройств памяти и попадают на входы схем 49 сравнения, которые

сравнивают старшие разряды адреса с содержимым регистра 44 логического номера памяти и, в случае совпадения, коммутируют входную информацию натвход второго приоритетного

ком-гутатора 46. Второй приоритетный коммутатор 46 в случае одновременного обращения к одному з стройству 2 памяти нескольких процессоров выбирает и коммутирует иа свой выход

информацию с одного из входов по позиционному приоритету. Позиционный номер процессора из соответствующих разрядов выдается с выхода вто - рого приоритетного коммутатора 46.

Установка регистра 36 конфигурации памяти производится следующим образом.

Процессор вырабатывает сигнал на шине 38 привилегированного режима, ив устройствах 2 памяти открываются соответствующие группы 50 элементов И, а группы 52 элементов НЕ закрьюают группу 51 элементов И.

. . 5

Позиционный номер в регистре 43 позиционного номера сравнивается со старшими разрядами адреса, которые через группу 50 элементов И поступают на вход схем 48 сравнения. В том устройстве 2 памяти, где эти номера совпадают, схема 48 сравнения передает информацию на вход приоритетного коммутатора 45, который, в случае одновременного обращения не- скольких процессоров, выбирает и коммутирует на свой выход информацию с одного из входов по позиционному приоритету. Блок 47 системных операций в соответствии с принятой информацией управляет установкой регистра 36 конфигурации памяти и регистра 44 логического номера устройства памяти, и

Многопрограммная работа в данной многопроцессорной системе организуется .следующим образом.

Предполагается, что система выполняет п программ по обслуживанию в реальном-времени, соответствующих п каналам (объектам) управления, Операцнонная система на каждом этапе логико-временной диаграммы работы назначает к выполнению системой соответствующий набор программ формирует код набора программ и записывает его в фиксированную ячейку памяти. Каждому разряду ячейки соответствует одна из п программ. Единица в разряде - условие включе- ния данной программы в набор, т.е. признак ее установки в очередь программ, нуль в разряде - признак отсутствия данной программы в наборе. Код набора программ переписывается из ячейки запоминающего устройства в .регистр 7 заполнения программных очередей .процессоров и поступает в аппаратуру фop шpoвaния и реализаци очереди заявок на выполнение программ. Регистр 23 заявок формирует очередь заявок для данного процессора, и если в очередь поступает заявка на вьтолнение программы более высокого приоритета, чем текущий приоритет выполняемой процессором программы, и блок 10 разрешения прерывания процессора формирует сигнал разрешения прерывания процессора,то аппаратура процессора производит прерывание текущей программы, стави ее в очередь и приступает к выполнению более приоритетной программы.

592786

Если заявка на вьтолнение программы не была обслужена за допустимое время, то заявка считается необслуженной. Счетчик 25 необслу- 5 женных заявок производит накопление необслуженных заявок и при пре- вМшении порогового условия (допустимого количества необслуженных заявок) вырабатывает сигнал Неиспоав- 10 иость процессора, который поступает как заявка высшего приоритета в другие процессоры на регистр 24 неисправностей, и процессоры через регистры 4 конфигурации процессоров 15 и регистры 36 конфигурации устройств памяти производят реконфигурацию вычислительной системы для данной , ситуации. Аппаратура при этом рабо- ; тает следующим образом.

20 Процессор 3 выбирает из устрой- . ства 2 памяти в регистр 7 заполнения программных очередей содержимое фиксированной ячейки, хранящей код набора программы. Информация из ре25 гистра 7 через первую группу 26 зле- ментов И поступает в регистр 23 заявок на прерывание, при зтом момент поступления на соответствующий разряд регистра 23 заявок синхронизиру30 ется сигналами с соответствующего таймера 22 блока 21 синхронизащга программ. При поступлении заявки в регистр 23 узел 8 выбора старшего приоритета производит сравнение при5 оритета поступившей заявки с приоритетами ранее поступивших и еще не обслуженных заявок. Если приоритет поступившей заявки ниже находящихся в системе, то заявка запоминается в

0 регистре 23 заявок на прерывание и и «ставится в очередь. Если приоритет поступившей заявки вьшге находящихся в системе, то узел 8 выбора старшего номера вырабатывает сиг5 нал прерьтания, который через эле мейт И 29 и шину 31 прерывания поступает в процессор 3, если блок 10 разрешения прерывания выработал сигнал на шина 30 разрешения прерыва0 ния.

Формирование сигнала разрешения прерьгоания на шине 30 разрешения, прерьгоания в рассматриваемой многопроцессорной вычислительной систе5 ме производится следующим образом.

При вьтолнении текущей программы процессор 3 заносит ее приоритет в

- . 1

регистр 6 текущего приоритета. Информация из регистра текущего приоритета каждого процессора поступает через группу 15 элементов; И на узел 16 выбора млддшего приоритета д{ у- гих процессоров, В каждом процессоре узел 16 выбора младщего приоритета осуществляет сравнение текущих приоритетов других процессоров и коммутирует на свой выход код младшего из сравниваемых текущих приоритетов. При равенстве кодов текзпдих приоритетов на входах узла 16 выбора на ее выход коммутируется код сравниваемьгё текущих приоритетов. Код с выхода узла 16 выбора поступает на вход схемы 19 сравнения (приоритетов) для сравнения с содержимым регистра 6 текущего приоритета«данного процесг сора. Если содержимое этого регистра текущего приоритета данного процессора меньше кода, вырабатываемого узлом 16 выбора младшего приоритета, то данный процессор вьшолняет задачу с самым низким приоритетом и стано- вится кандидатом на прерывание. При этом схема 19 сравнения вьфабатыва- ет на своем втором выходе :сигнал, который через элемент ИЛИ 20 поступает на выход блока 10 разрешения прерывания. Если содержимое регистра 6 текущего приоритета данного процессора больше кода, вырабатыва- .емого узлом 16 выбора, то данный процессор не является кандидатом на прерывание, и первый и второй выходы схемы 19 сравнения равны нулю.

Если содержимое регистра 6 текущего приоритета равно коду младшего текущего приоритета, то это означает, что два или более процессоров вьшолняют программы одинакового приоритета. В этом случае процессор кандидат на прерывание выбирается по младшему позиционному номеру узлами 17 выбора младщего номера и схемами 18 сравнения, работающими аналогично узлам 16 выбора и схемам 19 сравнения соответственно. При этом сигнал на втором выходе схемы 19 сравнения равен нулю, а на ее первом выходе вырабатывается сигнал, включающий третий узел 17 выбора, на вход которой через группу 14 элементов И поступает информация с выходов регистров 5 позиционных номеров других процессоров. Код младшего позиционного номера с выхода

592788

узла 17 выбора поступает на вход схемы 18 сравнения, где сравнувает- ся с содержимым регистра 5 позиционного номера данного процессора. 5 Если содержимое регистра 5 позиционного номера процессора меньше кода младщего позиционного номера, то схема 18 сравнения вырабатывает сигнал, который через элемент ИЛИ 20 10 поступает на выход блока 10 разрешения прерывания.

Регистр 6 текущего приоритета содержит 1+п разрядов, где первый (старший) разряд соответствует сиг- 15 налу неисправности данного процессора и устанавливается в единичное состояние, если на шине 32 отключения неисправного процессора вьфабо- тался сигнал, остальные п разрядов 20 соответствуют h вьтолняемым программам, т.е. в текущий момент только один из разрядов может быть установлен в состояние 1, причем йог мер разряда определяет номер текуще- 2 го приоритета. Если на щине 32 выработался сигнал, то все п разрядов регистра 6 данного процессора устанавливаются в нулевое состояние. При этом на схему 19 сравнения по- 30 ступают 1+п разрядов регистра 6,

а на вторые входы групп 15 элементбв И других процессоров поступают п разрядов из регистра 6 текущего приоритета данного процессора, 35 Процессор 3 при поступлении сигнала Прерывание по шине 3 прерывает выполнение данным процессором 3 текущей программы и переходит к выполнению программ операционной сис- Q темы. При этом процессор 3 -списьгеа- ет из блока 8 выбора старшего номера через шину 32 вектора прерьгаания код прерываемой программы и записывает его в фиксированную ячейку, срав- 45 нивает код прерываемой программы с кодом набора программ, вьтолняемых в данный момент другими процессорами системы. Если данная программа уже вьтолняется одним из процессоров, то 5(j операционный блок через шину 33 устанавливает в регистр 23 заявок соответствующий данной программе разряд в исходное состояние и списывает эту программу из очереди программ к 5J данному процессору.

Если данная программа не вьтолняется ни одним из .процессоров системы, то операционный блок по

выполне-

ходу программы переходит к нию прерьгааемой программы.

По окончании выполнения программы процессор 3 через шину 33 устанавливает в регистр 23 заявок соответствующий данной программе разряд в исходное состояние, при этом все остальные разряды регистра 23 остаю ся без изменения, т.е. данная прогрма изымается из очереди программ до поступления следующей заявки на ее выполнение.

Если данная программа не вьшол- нилась за допустимое время, то очередной сигнал с соответствующего данной программе таймера 22 поступает через соответствующий элемент И первой группы 26 элементов И на второй вход соответствующего элемента И второй группы 27 элементов И, на первый вход которого поступает в данный момент единичный сигнал с соответствующего данной программе разряда регистра 23 заявок, так как сигнал об окончании данной программы не поступил. При этом с выхода соответствующего данной программе элемента И второй группы 27 элементов через элемент ИЛИ 28 на вход счетчика необслуженных заявок 25 поступает сигнал.

При превьшении порога, т.е. допустимого количества необслуженынх заявок, счетчик необслуженных заяв вырабатьтает на первом выходе сигнал, который поступает в другие прцессоры через шину 41 неисправност .процессора, а на втором выходе выр батьгоает сигнал, который поступает на второй вход регистра 6 текущего приоритета через тину 42 отключени неисправного процессора.

При этом регистр 6 текущего приоритета устанавливается в состояни соответствующее коду 100,..О, и даный процессор через собственную схему 19 сравнения и узлы 16 выбор младщего -приоритета других процессров автоматически исключается из пцедуры выбора процессора - кандидата на прерывание. Сигнал по щи.не 4 неисправности процессора поступает на соответствующий вход группы входов регистра 24 неисправностей других процессоров. Информация из регистра неисправностей поступает на соответствующий вход группв входо блока 8 выбора старшего номера как

10

9278 заявка

0

5

0

5

0

5

0

45

более высокого приоритетаг чем любая заявка, поступившая из регистра 23,заявок, т.е.-процессор, (при наличии сигнала на щиие 30 раз решения прерывания процессора)) прерывает вьщолнение текущей програм- мы и переходит к выполнению программы реконфигурации системы при данной ситуации. По окончанин программы реконфигурации процессор 3 выбирает из памяти код окончания данной про- граммь и через шину 33 устанавливает его в регистр 24 неисправностей, при этом соответствующий данной программе разряд регистра 24 устанавливается в нулевое состояние, а все остальные разряды 24 и регистра 23 остаются без изменения, т.е. программа обслуживания заявки по сигналу Неисправность другого процессора списывается из очереди программ данного процессора.

Изменение конфигурации системы управляется регистрами 4 конфигурации процессоров и регистрами 36 конфигурации памяти. Установка регистра 4 конфигурации процессора производится процессором 3, Часть разрядов регистра 4 конфигурации процессора служит для отключения от процессоров устройства 2 памяти. Осуществляется это отключение с помо- щью запирания группы 11 элементов И.

Другая часть разрядов регистра 4 конфигурации процессора служит для исключения процессоров 3 из многопрограммной работы. При этом группа 14 элементов И служит дпя исключения отключаемого процессора из процедуры сравнения позиционных номеров, группа 15 элементов И - для исключения из процедуры сравнения текущих приоритетов. I

50

Применение предлагаемых элементов и связей, реализующих процедуру формирования очередей заявок на выполнение программ в отдельных процессорах в реальном времеии, позволяет при Отказе любого процессора автоматически производить реконфигурацию системы через другие процессоры За время, не превьш1ающее допустимое для обслуживания каналов (объектов) уп- 55 равления в реальном масштабе времени и тем самым исключить неисправный процессор из процедуры выбора процессора - кандидата на прерывание.

и

Формула изобретения

Устройство сопряжения процессоров в многопроцессорной вычислительной системе с изменяемой конфигурацией, содержащее регистры конфигурации системы, по зиционного номера процессора, текущего приоритета задачи и заполнения программных оче- . редей, блоки сопряжения с устройствами памяти и разрешения прерывания процессора, узел выбора старшего приоритета и элемент И, причем блок сопряжения с устройствами памяти содержит элемент ИЛИ, группу схем сравнения и группу ключей, а блок разрешения прерывания процессора содержит элемент ИЛИ, две схемы сравнения, узел выбора младшего номера, узел выбора младшего приоритета и две группы ключей, вход установки позиционного номера процессора устройства соединен с информационным входом регистра позиционного номера процессора, выход которого является выходом номера процессора в системе устройства и подключен к первым информационным входам схем сравнения блока сопряжения с устройствами памяти и к первому входу первой схемы сравнения блока раз- шерения прерывания процессора, вход установки текущего приоритета задачи устройства подключен к информационному входу регистра текущего приоритета задачи устройства и соединен с первым информационным входом второй схемы сравнения блока разрешения прерывания процессора, вход установки конфигурации системы устройства подключен к информационному входу регистра конфигурации системы, первая группа выходов которого подключена к управляющим входам ключей блока сопряжения с устройствами памяти, вторая группа выходов регистра конфигурации системы подключена к уп- равляницим входам ключей, первой и второй групп блока разрешения прерывания процессора, группа входов номера процессора в системе и группа входов текущего приоритета устройства подключена к информационным входам ключей первой и второй групп, блока разрешения прерывания процессора соответственно, выходы которых подключены к информационным входам узлов выбора младшего номера и вы5927812

бора младшего приоритета соответственно, а выходы этих узлов подключе.- ны к вторым информационным входам первой и второй схем сравнения блока 5 разрешения прерывания процессора соответственно, выходы которых подключены к первому и второму входам элемента ИЛИ блока разрешения прерывания процессора, группа инфор- 10 мационных входов устройства соединена с информационными входами ключей блока сопряжения с устройствами памяти, выходы которых соединены с вторыми информационными входами со- 15 ответствующих схем сравнения блока сопряжения с устройствами памяти, выходы которых подключены к входам элемента ИЛИ этого блока, а его выход является информационным выходом 20 устройства, вход установки заполнения программных очередей устройства соединен с информационным входом регистра заполнения, программных очередей, выход запроса прерьшания уст- 25 ройства подключен к выходу элемента . И, первый вход которого соединен с выходом сопровождения узла выбора старшего приоритета, о т л и ч а ю- щ е е с я тем, что, с целью повьппе- 30 ния надежности и живучести системы, в устройство введены группа таймеров, регистры заявок на прерывание и неисправностей, счетчик необслуженных заявок, первая и вторая группы эле- 5 ментов И и элемент ИЛИ, при этом выходы таймеров подключены к первым входам соответствующих элементов И первой группы, вторые входы которых подключены к выходам соответствую- 0 Щих разрядов регистра заполнения программных очередей, г.ыходы элементов И первой группы подключены к информационным входам регистра заявок на прерывание и к первым входам соответ- 5 ствующих элементов И второй группы, выходы регистра заявок на прерывание подключены к вторым входам соответствующих элементов И второй группы и к информационным входам узла выбора 0 старшего приоритета, выход вектора прерывания которого является одноименным выходом устройства, выходы элементов И второй группы подключены к входам элемента ИЛИ, выход ко- 5 торого подключен к счетному входу счетчика необслуженных заявок, входы синхронизации регистров неисправностей и заявок на прерывание сое13

динены с входом синхронизации устройства, выход регистра неисправное тей подключен к информационным входам узла выбора старшего приоритета, выход блока разрешения прерьшания прЬцессора подключен к второму входу элемента И, первый выход счетчика необслуженных заявок подключен к

12592781

входу блокировки регистра текущего приоритета задачи, второй выход является выходом признака неисправ-. ности устройства, при этом входы 5 признаков неисправностей устройства . соединены с информационными входами регистра неисправностей.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многопроцессорная вычислительная система с изменяемой конфигурацией | 1974 |

|

SU525953A1 |

| Микропрограммное устройство управления с контролем | 1983 |

|

SU1136162A1 |

| Селекторный канал | 1983 |

|

SU1226477A1 |

| Многопроцессорная вычислительная система | 1977 |

|

SU670937A1 |

| Мультипроцессорная система | 1983 |

|

SU1156088A1 |

| Устройство для обмена информацией управляющей вычислительной машины с объектами управления | 1982 |

|

SU1030792A1 |

| Устройство для управления прерыванием программ | 1981 |

|

SU962950A1 |

| Вычислительная система | 1977 |

|

SU692400A1 |

| Устройство для обмена двухмашинного вычислительного комплекса | 1981 |

|

SU991403A1 |

| Устройство для сопряжения периферийных устройств с процессором и оперативной памятью | 1983 |

|

SU1156084A1 |

Изобретение относится к вычислительной технике, в частности к многопрогпяммным, многопроцессорным системам, работающих в реальном масштабе времени. Цель изобретения - повьшение надежности и живучести системы за счет исключения ситуации, при которой система перестает реагировать на поступление заявок на обслуживание при отказах процессоров- кандидатов на прерывание. В устройство сопряжения процессоров введены дополнительно таймеры, регистр заявок на прерывание, регистр неисправностей, счетчик необслуженных заявок, первая и вторая группы элементов И, элемент ИЛИ. Если заявка на выполнение программы не была обслужена за допустимое время, она считается необслуженной. Счетчик необслуженных заявок производит накопление количества необслуженных заявок и при превышении порогового уровня (допустимого количества не- обслуж,енных заявок) вырабатывает сигнал неисправность процессора,ко- Topbtff поступает как заявка высшего приоритета в другие устройства сопряжения процессов на регистры не- исправностей. Процессоры через регистры конфигурации процессоров и регистры конфигурации устройств памяти производят конфигурацию вычислительной системы для данной ситуации. Это позволяет при отказе любо- го процессора-кандидата на прерьта- ние автоматически производить реконфигурацию систеь ы через устройства сопряжения процессоров за время, не превьпаающее допустимое для обслуживания каналов (объектов) управления в реальном масштабе времени, и тем самым исключить неисправный процессор из Процедуры выбора процессора- кандидата на прерывание. 2 ил с (Л ел

| Авторское свидетельство СССР №551648, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Многопроцессорная вычислительная система с изменяемой конфигурацией | 1974 |

|

SU525953A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-09-23—Публикация

1984-09-26—Подача