1

Изобретение относится к вычислительной технике, в частиости к нроектированию многопрограммных, многопроцессорных систем.

Известна многопроцессорная вычислительная система 1, содержащая связанные между собой процессоры, блок управления прерыванием и оперативное запоминающее устройство (ОЗУ), причем каждый процессор включает в себя блок сопряжеиия с ОЗУ, операционный блок, блок управления и синхронизации, регистр текущего приоритета, схемы сравнения и блок контроля.

К недостатку данной системы относятся большие затраты времени на переключение задач.

Из известных многопроцессорных вычислительных систем наиболее близкой по технической сущности к изобретенню является многопроцессорная вычислительная система 2. Она содержит нроцессоры, устройство управления прерыванием и оперативное запоминающее устройство, входы и выходы которого соединены соответственно с первымн выходом и входом каждого нз процессоров, второй выход каждого из процессоров подключен к соответствующим входам других процессоров, причем каждый из процессоров содержит блок сопряжения, первые вход и выход которого соединены соответствеьло с нервыми входом и выходом процессора, блок выполнения операцнй, первый выход которого соединен с вторым входом блока сопряжения, второй выход которого соединен с первым входом блока выполнения операций, вторым выходом подключенного к входу блока контроля. Выход блока контроля соединен с первым входом блока управлення и

синхроннзации, первый выход которого связан с вторым входом блока выполнения операций, третий выход которого через последовательно соединенные первый элемент И и элемент ИЛИ подключен к первому

входу регистра текущего приоритета. Второй вход последнего соединен е вторым выходом блока управления и синхронизации, а выход - с вторым входом процессора, первым входом схемы сравнения приоритетов и первым входом схемы сравнения, выход которой соедннен с вторым входом блока управления и спнхронизации, третьим выходом подключенного через группу триггеров блокировки к первым входам

группы элементов И, вторые входы которых соединены с соответствующими входами процессора, а выходы - с входами схемы сравнення приоритетов. Выход последней связан с вторым входом схемы сравнения,

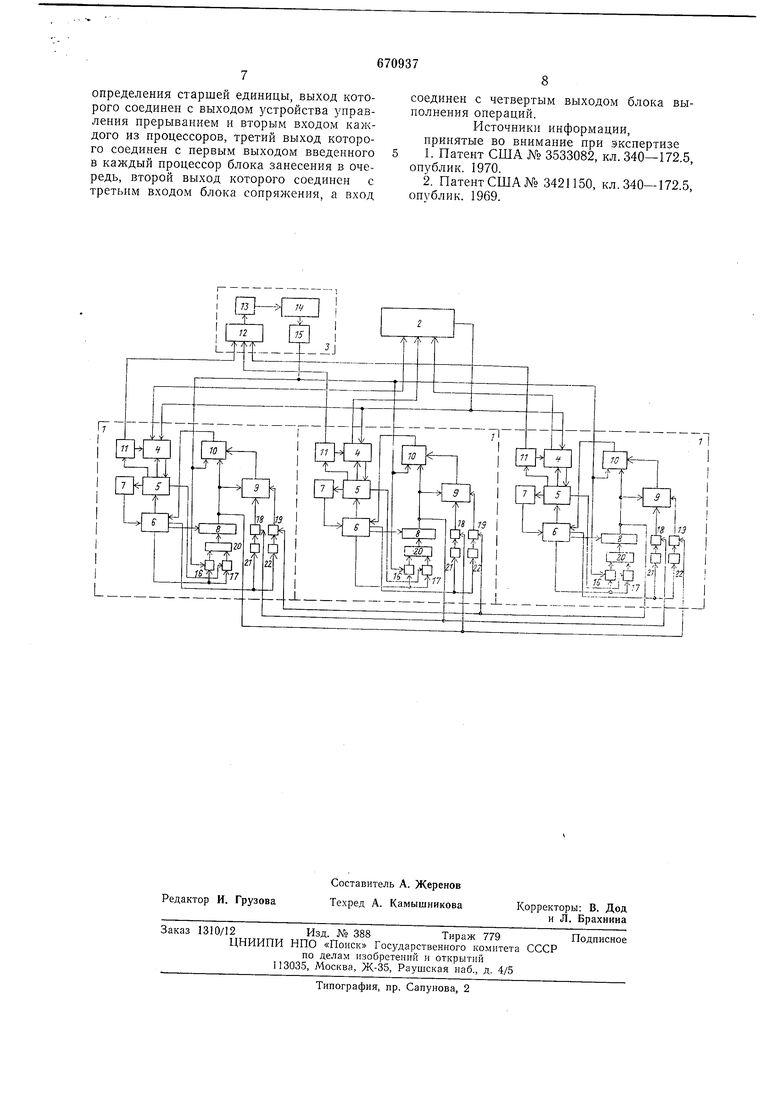

третий вход которой соединен с вторым входом процессора и с первым входом второго элемента И, выход которого подключен к входу элемента ИЛИ, а второй вход соединен с вторым входом первого элемента И и четвертым выходом блока правлення и синхроннзации. Недостатками известно многопроцессорной вычислительной системЕз являются большие затраты оборудования на реализацию приоритетного распределения задач по процессорам и большие затраты времени на переключение задач. Цель изобретения - упрощение и увеличение быстродействия системы. Поставленная цель достигается тем, что в многоироцессорной вычислительной системе устройство управления прерыванием содержит блок приоритетного выбора запросов, блок установки регистра заполненных очередей, регистр заполненных очередей и блок определения старшей единицы, причем третьи выходы процессоров соединены с входами устройства управления прерыванием и входами блока приоритетного выбора запросов, выходом подключенного к входу блока установки регистра заполненных очередей, выход которого через регистр заполненных очередей соединен с входом блока определения старшей единицы, выходом связанного с выходом устройства унравления прерыванием и с вторым входом каждого из процессоров, третий выход которого подключен к первому выходу введенного в каждый процессор блока занесения в очередь, второй выход которого соединен с третьим входом блока сопряжения, а вход - с четвертым выходом блока выполнения операций. Схема системы показана на чертеже. Она содержит процессоры 1, оперативное запоминающее устройство (ОЗУ) 2, устройство 3 управления прерыванием, причем каждый из процессоров включает в себя блок 4 сопряжения, блок 5 выполнения операций, блок 6 управления и синхронизации, блок 7 контроля, регистр 8 текущего приоритета, схему 9 сравнения приоритетов, схему 10 сравнения, блок 11 занесения в очередь. Устройство 3 )шравления прерыванием содержит блок 12 приоритетного выбора запросов, блок 13 установки регистра заполненных очередей, регистр 14 заполненных очередей, блок 15 определения старшей единицы. В вычислительную систему входят также элементы И 16, 17, группа элементов И 18, 19, элемент ИЛИ 20, группа триггеров 21, 22 блокировки. Обработка информации в процессоре 1 производится блоком 5, который обменивается информацией с ОЗУ 2 с помощью блока 4 сопряжения. Управляющие и синхронизирующие импульсы, необходимые для функционирования процессора, вырабатываются блоком 6 управления и синхронизации. При этом первый его выход синхронизирует работу блока 5, второй выход - изменение регистра 8 текущего приоритета, третий выход - прием информации в триггеры 21, 22 блокировки, а четвертый выход - прием информации в регистр 8 текущего приоритета. Блок 7 контролирует работу блока 5. При наличии сбоя блок 7 контроля передает информацию о сбое в блок 6 управления и синхронизации, который через четвертый выход устанавливает наивысший приоритет в регистре 8 текущего приоритета и осуществляет переход в диагностический режим для локализации места неисправности. Многопрограммная работа в данной многопроцессорной системе организуется следующим образом. Операционная система, размещая программы в памяти, присваивает каждой программе приоритет (возможно присвоение одинакового приоритета нескольким программам). Для каждого из возможных значений приоритета операционная система формирует очередь программ. При этом часть очередей может быть пустой, если в текущий момент в системе отсутствуют заявки на выполнение программ с данными приоритетами. Распределение программ по процессорам происходит с помощью устройства 3 управления прерыванием. Занесение программы в очередь процессором 1 осуществляется путем передачи информации из блока 5 через его четвертый выход в блок 11 занесения в очередь, который через второй выход передает информацию программы в ОЗУ 2, а через первый выход - запрос и номер приоритета программы на третий выход процессора 1, который соединен с входом блока 12. Блок 12 приоритетного выбора запросов при одновременном обращении к нему нескольких процессоров 1 выбирает наиболее приоритетный (по позиционному приоритету) и передает номер приоритета программы в блок 13 установки регистра заполненных очередей, который устанавливает в «1 соответствующий разряд в регистре 14. Таким образом, по мере занесения операционной системой программы в очереди разных приоритетов в регистре 14 устанавливаются единицы в разрядах, соответствующих приоритетам непустых очередей. Блок 15 определения старщей единицы формирует на выходе двоичный код наиболее приоритетной непустой очереди. При выполнении текущей программы на процессоре 1 блок 5 через схемы И 17, ИЛИ 20 заносит приоритет выполняемой программы в регистр 8 текущего приоритета. Аппаратура процессоров непрерывно сравнивает приоритеты выполняемых программ во всех процессорах н тот процессор, чья программа имеет самый низкий приоритет, становится кандидатом на нрерывание. Этот процессор по состоянию регистра

14проверяет, есть ли в списке очередей программа с приоритетом более высоким, чем та, которую он исполняет. Если такая программа есть, то процессор - кандидат на прерывание прерывает исполнение текущей программы, заносит ее в список очередей и выбирает из списка для исполнения программу с высшим приоритетом.

Работает аппаратура следующим образом.

В каждом процессоре схема 9 сравнивает текущие приоритеты данного и других процессоров и вырабатывает на выходе единичный сигнал, если текущий приоритет данного процессора меньше текущих приоритетов других процессоров. Группа элементов И 18, 19, управляемых триггерами 21, 22 блокировки, служит для отключения от схемы 9 сравнения приоритетов процессоров, которые не участвуют в работе (например, процессоров, в которых зафиксирован отказ или которые находятся на профилактике). Установка триггеров блокировки осуществляется операционной системой через третий выход блока 6 управления и синхронизации.

При наличии единицы на выходе схемы 9 сравнения приоритетов включается схема 10, которая сравнивает содержимое регистра 8 текущего приоритета с выходом блока

15определения старшей единицы устройства 3 управления прерыванием. Если содержимое регистра текущего приоритета меньще кода на выходе блока определения старшей единицы, то это означает, что в списке очередей есть программа с приоритетом более высоким, чем программа, исполняемая данным процессором.

При этом выходной сигнал со схемы 10 сравнения поступает на второй вход блока 6 управления и синхронизации, который через блок 5 и блок И осуществляет занесение в очередь текущей программы, а через блок 4 сопряжения - выборку из ОЗУ 2 задачи из очереди с приоритетом, соответствующим коду на выходе блока 15 определения старшей единицы. Если из очереди данного приоритета выбрана последняя программа, то блок 5 через блоки 11, 12 и 13 гасит соответствующий разряд регистра 14.

Таким образом, устройство 3 управления прерыванием осуществляет распределение программ по процессорам 1, выбирая из очередей программы высшего приоритета.

Введение регистра 14 заполненных очередей и блока 15 определения старшей единицы в устройство 3 управления прерыванием позволяет непрерывно сравнивать приоритеты задач, решаемых на процессорах 1, и задач, занесенных в приоритетные очереди. Это сокращает время переключения задач и повышает быстродействие системы.

Формула изобретения

Многопроцессорная вычислительная система, содержащая процессоры, зстройство управления прерыванием и оперативное запоминающее устройство, входы и выходы

которого соединены соответственно с первыми выходом и входом каждого из процессоров, второй выход из процессоров соединен с соответствующими входами других процессоров, причем каждый из процессоров включает блок сопряжения, первые вход и выход которого соединены соответственно с первыми входом и выходом процессора, блок выполнения операций, первый выход которого соединен с вторым входом

блока сопряжения, второй выход которого соединен с первым входом блока выполнения операций, второй выход которого соединен с входом блока контроля, выход которого соединен с первым входом блока

управления и синхронизации, первый выход которого соединен с вторым входом блока выполнения операций, третий выход которого через последовательно соеднненные первый элемент И и элемент ИЛИ подключен

к первому входу регистра текущего приоритета, второй вход которого соединен с вторым выходом блока управления и синхронизации, а выход соединен с вторым входом процессора, первым входом схемы

сравнения приоритетов и первым входом схемы сравнения, выход которой соединен с вторым входом блока управления и синхронизации, третий выход которого через группу триггеров блокировки соединен с

первыми входами группы элементов И, вторые входы которых соединены с соответствующими входами процессора, а выходы - с входами схемы сравнения приоритетов, выход которой соединен с вторым входом

схемы сравнения, третий вход которой соединен с вторым входом процессора и с первым входом второго элемента И, выход которого подключен к входу элемента ИЛИ, а второй вход соединен с вторым входом

первого элемента И и четвертым выходом блока управления и синхронизации, отличающаяся тем, что, с целью упрощения и увеличения быстродействия, в ней устройство управления прерыванием содержит

блок приоритетного выбора запросов, блок установки регистра заполненных очередей, регистр заполненных очередей и блок определения старшей единицы, причем третьи выходы процессоров соединены с входами

устройства управления прерыванием и входами блока приоритетного выбора запросов, выход которого соединен с входом блока установки регистра заполненных очередей, выход которого через регистр заполненных очередей соединен с входом блока

определения старшей единицы, выход которого соединен с выходом устройства управления прерыванием и вторым входом каждого из процессоров, третий выход которого соединен с первым выходом введенного в каждый процессор блока занесения в очередь, второй выход которого соединен с третьим входом блока сопряжения, а вход

соединен с четвертым выходом блока выполнения операций.

Источники информации, принятые во внимание при экспертизе

1.Патент США № 3533082, кл. 340-172.5, опублик. 1970.

2.Патент США № 3421150, кл. 340-172.5, опублик. 1969.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многопроцессорная вычислительная система с изменяемой конфигурацией | 1974 |

|

SU525953A1 |

| Устройство сопряжения процессоров в многопроцессорной вычислительной системе с изменяемой конфигурацией | 1984 |

|

SU1259278A1 |

| Устройство управления прерываниями | 1982 |

|

SU1242948A1 |

| Управляющая векторная вычислительная система | 1982 |

|

SU1120340A1 |

| Устройство для распределения заданий процессорам | 1985 |

|

SU1291983A1 |

| Устройство для обмена данными | 1974 |

|

SU506847A1 |

| Устройство приоритетного прерывания для микро-ЭВМ | 1982 |

|

SU1113803A1 |

| Устройство для обмена информацией | 1989 |

|

SU1702378A1 |

| Устройство управления взаимным доступом процессора многопроцессорной системы | 1989 |

|

SU1631548A1 |

| Устройство для программного управления технологическим оборудованием | 1989 |

|

SU1714575A1 |

Авторы

Даты

1979-06-30—Публикация

1977-04-08—Подача