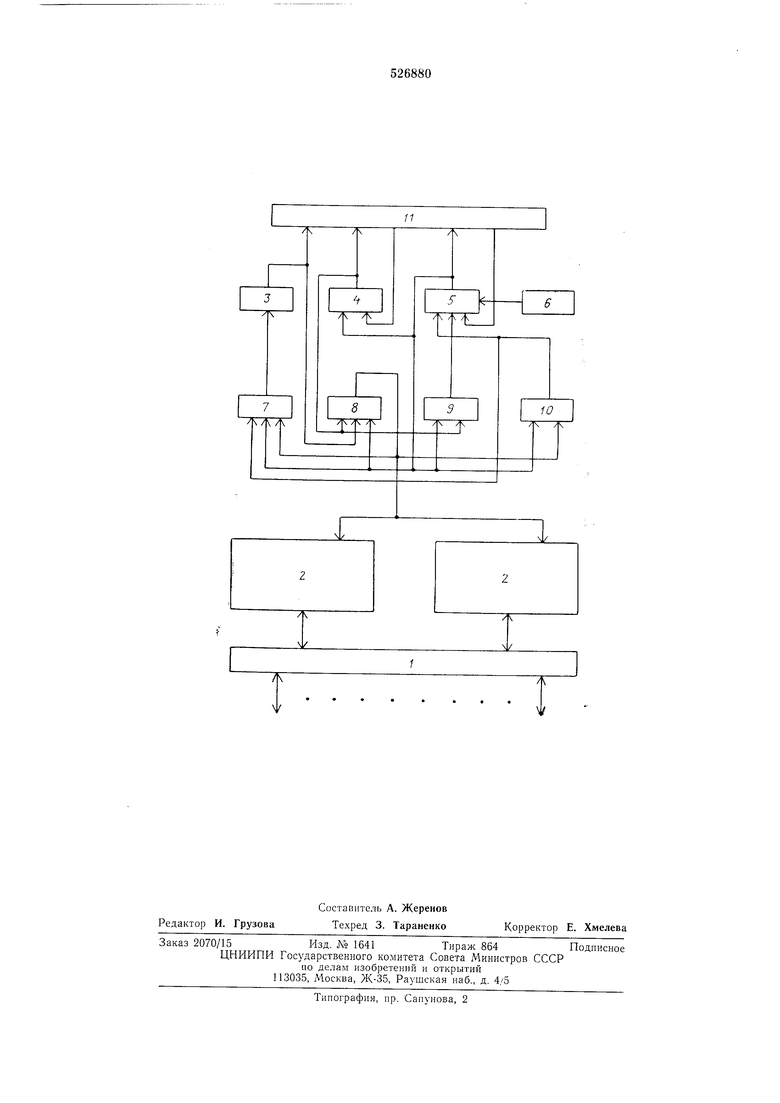

(54) УСТРОЙСТВО ДЛЯ ВЫВОДА ДАННЫХ ИЗ ПРОЦЕССОРА вход блока управления подсоединен к выходу генератора тактовой частоты, выход блока управления-к третьему входу процессора, к управляющим входам регистра обмена, блока анаоТиза управляющих слов и коммутатора каналов, выход этого коммутатора - к входам блоков сопряжения, сгзязанных с блоком согласования параметров, входы и выходы которого соединены соответственно с входами н выходами устройства. Это устройство имеет такие же недостатки, что п рассмотренные устройства 1,2. Цель изобретения - повыщение производительности работы устройства. Это достигается тем, что в устройство введены блок выбора канала передачи и блок задания режима вывода, входы которого подключены соответственно к выходам блока управления и коммутатора каналов, выход - к четвертому входу блока управления и первому входу блока выбора канала передачи, второй и третий входы которого соединены соответственно с выходами коммутатора каналов и блока управления, выход - с входом щифратора адреса. Такое выполнение устройства позволяет автоматически, без участия программы вывода процессора, проводить побитную выдачу в каналы связи, осуществляющие передачу на различных скоростях, что естественно приводит к оптимизации обмена с оперативной памятью процессора (уменьщепие времени обмена). Схема устройства представлена па чертеже. В ее состав входят: блок 1 согласования нараметров, преобразующий в режиме вывода уровни сигналов элементов, на которых выполняется устройство, в уровни сигналов передачи по каналам связи; блоки 2 сопряжения, осуществляющие выработку сигналов управления аппаратурой передачи данных; щифратор 3, обеспечивающий кодирование адресов управляющих слов и номера канала вывода; регистр 4, через который происходит информационный обмен с процессором; блок 5 управления для тактировки и синхронизации всех узлов устройства; генератор 6, задающий тактовую частоту устройства; блок 7 выбора канала нередачи; коммутатор 8 для переключения каналов нередачи; блок 9 анализа управляющих слов, задающий режимы передачи по каналу (передача служебной информации, информационный обмен); блок 10 задания режима вывода, инициирующий режим вывода в каналы связи; процессор 11, осуществляющий прием, обработку и передачи информации, поступающей по каналам связи. Сообщения, иоступающие по каналам связи на различных скоростях со множества терминальных пультов в процессор сбора, обработки и передачи данных, обрабатываются программами процессора. В случае, если процессор осуществляет вывод в канал, программы вывода формируют в оперативной памяти процессора канальный массив вывода. Каждому такому каналу соответствуют в фиксированной области онеративной памяти процессора управляющие слова вывода канала, в которые программы вывода заносят начальный и конечный адреса массива вывода, кроме того, предусматривается поле для текущего адреса выдачи, а также отведены информационное поле, в которое в соответствии с текущим адресом заносятся очередные байты выводимой информации, ноле количества переданных байт, поле служебных признаков; начало передачи, конец нередачи, поле кода константы скорости передачи по каналу. В другой фиксированной области памяти выделяются определенные участки (групповые ячейки вывода), число которых равно 1количеiCTBy ВОЗМОЖНЫХ Градаций скоростей обмена по каналу. В эти ячейки оперативной памяти одновременно с формированием канального массива вывода заносятся коды «1 в те разряды, которые соответствуют порядковому номеру канала выдачи. В эти же моменты времени программы вывода в соответствии с кодами констант скоростей передачи по данным каналам, которые записаны в управляющих словах вывода каналов, заносят в блок 10 задания режима вывода коды выдачи (код «1) на данной скорости в канал. По этим признакам, поступающим по выходным щинам блока 10 задания режима вывода в блок 5 управления, последнее формирует но тактовой частоте генератора 6 тактовой частоты еинхроимпульсы, соответствующие частотами передачи в канал. При приходе очередного синхроимпульса блок 7 выбора канала передачи в соответствии с кодами выдачи, записанными в блоке 10 задания режима вывода, выбирает грунну каналов, осуществляющих передачу на максимальной частоте и на своих выходных щинах задает номер этой группы скорости. Шифратор 3 адреса в соответствии с данным номером группы скорости задает на своих выходных щинах код адреса групповых ячеек, соответствующих данной градации скорости. По сигналу, вырабатываемому устройством уравления, цроцессор осуществляет чтение групповой ячейки по данному адресу из оперативной намяти, содержимое которой поступает на регистр 4 обмена. Информация с регистра 4 обмена через коммутатор 8 каналов поступает на блок 7 выбора канала передачи. Блок 7 выбора канала передачи обеспечивается поиск первой значащей «1 и на своих выходных щинах задает номер выбранного канала, что в соответствии с выбранной градацией скорости позволяет щифратору 3 адреса задать код управляющего слова данного канала, которое по сигналу блока 5 управления читается из оперативной памяти процессора, и поступает на регистр 4 обмена и анализируется блоком 9 анализа управляющих слов. При этом из разрядов регистра 4 обмена соответствующих информационному нолю, коммутатор 8 каналов в соответствии с кодом па выходных шинах шифратора 3 адреса выбирает очередной бит информации, передаваемой по данному каналу и записывает его в триггер вывода блока 2 сопряжения соответствующего канала. После этого управляющее слово модифицируется и записывается по этому же адресу в область управляющих слов канала оперативной памяти процессора. Затем устройство, аналогично описанному, переходит на отработку вывода бита информации по следующему каналу, осуществляющему вывод.

Следующий цикл вывода в каналы связи происходит по очередному сипхроимпульсу, выработанному блоком 5 управления. Когда заканчивается выдача заданного канального массива (равенство кодов текущего адреса выдачи и конечного адреса массива, заданных в управляющих словах вывода канала), код выдачи в соответствующей групповой ячейке и в блоке 10 задания режимов вывода гасится.

Формула изобретения

Устройство для вывода данных из процессора, содержащее блоки сопряжения, управления, согласования параметров, щифратор адреса, регистр обмена, генератор тактовой частоты, коммутатор каналов, блок анализа управляющих слов, причем выход щифратора адреса подключен к первым входам процессора и коммутатора каналов, выходы процессора подключены соответственно к первым входам блока управления и регистра обмена, выход которого подключен к вторым входам коммутатора каналов и процессора и входу блока

анализа управляющих слов, выход которого подключен к второму входу блока управления, третий вход которого подключен к выходу генератора тактовой частоты, выход блока управления подключен к третьему входу процессора, к управляющим входам регистра обмена, блока анализа управляющих слов и коммутатора каналов, выход которого подключен -к входа:м блоков сопряжения, соедиценных с блоком согласоваиияПараметров, входы и выходы которого соединены соответственно с входами п выходами устройства, отличающееся тем, что, с целью повыщения производительности работы, в него введены

блок выбора канала передачи и блок задания режима вывода, входы которого подключены соответственно к выходам блока управления и коммутатора каналов, выход подключен к четвертому входу блока управления и первому входу блока выбора канала передачи, второй и третий входы которого подключены соответственно к выходам коммутатора каналов и блока управления, выход соединен с входом шифратора адреса.

Источники информации, принятые во внимание при экспертизе:

1.Патент США, № 3587058, кл. 340-172.5, М. Кл. G 06f 3/00 1971.

2.Патент США, № 3564509 кл. 340-172.5, М. Кл. G 06f 15/16 1971.

3.Патент США кл. 340-172.5, № 3311889, 1967.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для синхронизации обменаМЕжду КОММуНиКАциОННыМ пРОцЕССОРОМи КАНАлАМи СВязи | 1979 |

|

SU809142A1 |

| Устройство для сопряжения процессора обмена с каналами связи | 1974 |

|

SU525939A1 |

| Двухканальная резервированная вычислительная система | 1989 |

|

SU1734251A1 |

| Устройство для связи процессоров | 1984 |

|

SU1193682A1 |

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1280642A2 |

| Система для отладки программ | 1987 |

|

SU1481774A1 |

| Мультиплексный канал | 1978 |

|

SU769522A1 |

| УСТРОЙСТВО КОНТРОЛЯ ПРОЧНОСТИ КРЫЛА ВОЗДУШНОГО СУДНА | 2011 |

|

RU2469289C1 |

| Устройство для синхронизацииВВОдА иНфОРМАции из КАНАлА СВязи | 1979 |

|

SU798774A1 |

| Распределенная система для программного управления технологическими процессами | 1990 |

|

SU1797096A1 |

Авторы

Даты

1976-08-30—Публикация

1975-01-06—Подача