Изобретение относится к цифрово вычислительной технике, ,в частности к процессора м.

Известен нроидессор 1, содержащий блок памяти, регистр микрокоманд, блОКи формирования -нриемов и выдач, блок регистров общего «азй.ачения, регистр адреса оперативного запоминающего устройства, клавишный регистр информации, регистр индикации, элементы «И, в ,которО:М визуальное отображение инфар;мации осуществляется программными средствам и.

Однако нри этОМ затраты времени на (визуальное отображение и нфармации значительные.

Микропро-граммные процессоры малых и средних вычислительных .машин, как правило, содержат в своем составе анпаратные или а1ппаратно- микр0пр01гра.ммные :средства для визуального .отобр)ажения информации.

Известен процессор 2, содержащий распределитель импульсов, регистр микрокоманды, соединенный через дешифраторы с блоками формирования Приемов н выдач, -межрегистровую магистраль, подключенную к клавишному регистру информации, регистру адреса онеративного запоминающего устройства, регистру сигналов обмена с оперативным запоминающим устройством, выходному регистру оноратиеного зацоминаюшего устройства, блоку регистров общего назначения и регистру индикации с подключенными к его выходам элементами индикации, схему сравнения, входы которой соединены с выходом клавишного регистра информации и выходом регистра адреса оперативного заноминающего устройства, клавишный регистр адреса, выход которого соединен с входом блока формирования выдач, выход которого соединен с входом межрегистровой магистрали, первый элемент «И, входы которого соединены соответственно с выходами блоков формирования приемов и выходом распределителя импульсов, а выход соединен с входом межрегистровой магистрали.

Однако быстродействие такого процессора невысокое. Оно ограничено временем распространения управляющих сигналов через по-следователыную цепь блоков и временем обмена информацией между регистром индикации и выбранными регистрами.

Цель изобретения - повышение быстродействия процессора.

Это достигается тем, что предлагаемый процессор содержит блоки управления индикацией, два триггера, элементы «И, элементы «ИЛИ, причем выходы клавишного регистра адреса соединены с первой группой входов блоков управления индикацией, вторая груипг. входов блоков управления индикацией соеди йена с выходам.и соответствующих блоков формирования приемов, третья группа входов блоков управления индикацией соединена с

«первым управляющим входом иродеосора, четвертая фуппа входов блоков управления индикацией соедииена ic единичным выходо м первого триггара и с .первым входом второго элемента «И, лятая лрулиа входов блоков управления индикацией соединена с выходами соответствующих блоков фО|р1МироваНЯя выдач и с входами элемента «ИЛИ, шестая группа входов блоков управления индикацией соединена С вт:0|рым управляющим ВХОДО.М процессора, выход элемента «ИЛИ соединен с вторым входом второго элемента «И, выход которого соединеп с единич1НЫ|М входоМ второго триггера:, выход которого соединен с первым входом третьего элемента «И, выход которого соединен с нулевым входо1М юервого тр-иггера, единичный вход первого триггера соединен с выходом четвертого элемента «И, первый вход которого соединен с выходом схемы сравнения, а второй - с выходом одного из разрядов регистра сигналов обмена с оперативным запоминающим устройством, выходы блоков управления индикацией соедиианы с входааш пятого элемента «И, выход которого соединен с управляющи1М входом регистра индикации, управляющий вход распределителя импульсов объединен с управляющими входааш блоков управлени.я индикацией, управляющими входами блоков формирования выдач, входами блокиров ки де Шифр1аторОВ и со единен с третьим управляющим входом процессора, выход распределителя импульсов соединен с входами третьего, четвертого и лятого элементов «И и с нулевым входом второго триггера.

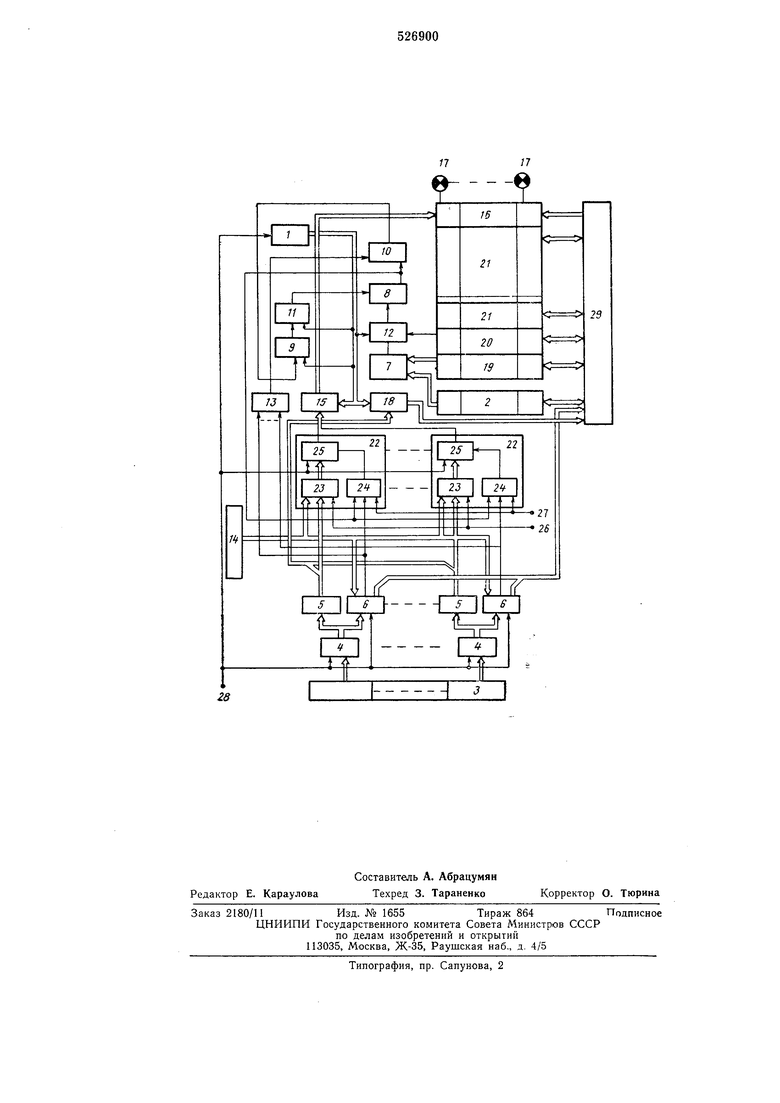

На чертеже покаеана функцианальная схема предл агаемого: процессор а.

Процессор содержит распределитель импульсов 1, 1кла1вишный регистр 2 информации, регистр 3 микрокоманды, дещифр-аторы 4 микроопераций регистровых пересылок, блоки 5 формирования приемов, блоки 6 фор1мирования выдач, схему сравнения 7, первый триггер 8, второй Т1риггер 9, первый элемент «И 10, второй элемент «И И, третий элемент «И 12, элемент .«ИЛИ 13, клавишный регистр 14 адреса, четвертый элемент «И 15, регистр индикации 16 с блоками 17 индикации, пятый элемент «И 18, регистр адреса 19 оперативного запоминающего: устрой:ства., регистр СйГналов обмена 20 с оперативным запоминающим устройством, ,а также регистры 21 о бщего и специального назначения, блоки управлеНия индикацией 22, каждый ,из которых включает в себя первый элемент «И 23, второй элемент «И 24 и элемент «ИЛИ 25.

Выходы регистра 3 микрокоманды .соедине1НЫ 1C входами дешифраторов 4 микроопераций регистровых пересылок, выходы дешифраторов 4 соединены с входа,ми блоков 5 и (э формирования приемов и выдач.

Выходы блоков 6 формирования выдач соединены с входами элемента «ИЛИ 13, с входами элементов «И 24 я с элементами выдачи информации в общую процессорную 1магистраль регистров 2, 19, 20 и 21. Выходы блоков 5 формирования приемов соединены с входа1ми соответствующих элементов «И 23 и с входами ;синхронизирующего элемента «И 18 у правления приемами в регистры 19, 20 и 21. ВыхОДы клавишного регистра 14 адреса соединены с входами элементов «И 23 и с входами блоков 6 фО:рмирования выдач. Выходы элементов 23 и 24 соединены с входами элемента «ИЛИ 25.

Выходы элементов «ИЛИ 25 :Соединены с входами Синхронизирующего элемента «И 15 управления приемами в .регистр 16 индикации. Выходы элемента «И 15 соединены с регистром 16. Входы схемы сравнения 7 подключены к выхода1М клавишного регистра 2 информации и к выходам регистра адреса 19 оперативного заноминающего устройства. Выход схемы сравнения 7 соединен с входом управляющего элемента: «И 12. Один из входов элемента «И 12 соединен с выходом разряда «Чтение регистра Силнааов обмена 20 с оперативным запоминающим устройством. Выход элемента «И 12 соединен с входом установки е:диницы триггера 8. Выход единичного плеча триггера 8 соединен с .одним из входов элемента «И 10 и с вхад:ами элементов «И 24. Выход эл:емента «И 10 соединен ic информационным ВХОД01М триггера 9. Выход единичного плеча триггера 9 соединен с одним из входов синхронизирующего элемента «И 11 выдачи информации ic этого триггера. Выход элемента «И 11 соединен с входом установки нуля триггера 8. Выход элемента «ИЛИ 13 соединен с одним из входов элемента: «И 10. Выходы распределителя 1 импульсов соединены с входами элементов «И 11, 12, с входами элементов «И 15 и 18, а также с входом триггера 9. Первый вход 26 задания .режимов индикации :соединен с входами эле.Ментов «И 23. Второй вход 27 задания режимов индикации соединен с входами элементов «И 24. Вход 28 устройства соединен С уцравляю:щим входом распределителя 1 им:пульсов, с входами элементов «ИЛИ 25, с входами блокиров:Ки дешифраторов 4 и :с управляющими входами блоков 6 формирования выдач.

Регистры 2, 16, 19, 20, 21 объединены магистр.алью 29.

В соответствии с управляющими сигналами приемов и выдач информации, поступающими с :выходов элементов 15, 18 и блока 6, :содержимое любого регистра (за исключением регистра индикации 16) может быть выдано в общую магистраль и переписано в один или несколько регистров этой структуры (за исключением клавишного регистра информации 2). Инфор:мация с .клаВишного регистр.а 2 может быть выдана в общую магистраль при наличии соответствующих сигналов выдачи, поступающих из блока 6. Регистр индикации 16 предназначен для дублирования информации, храня щейся в одном из регистров (в режиме «Ин.ди1ка1ция регистра) или в одной из ячеек памяти оперативного запоминающего устройства (в режиме «Индикация ячейки памяти). что позволяет в ходе ра|боты процессора следить за состоянием выбраяного регистра или выбраиной ячейки памяти. Адрес выбираемой для иидикации ячейки памяти «а|бир:ается на .клавишноад регистре 2. Адрес выбираемо-го регистра задается клавИШНым регистром 14. На регистре 3 микрокоманды фиксируется ynpaiBляющее слово, определяющее адреса «регистра-передатчика и «регистра-Прием1НИ1ка для каждого диокретного П1рОМежут1ка времени (фуикциОнального импульса), отведенного для элементарной процедуры передачи информации по общей магистрали. Число независимых полей микрокоманды равно числу функционашыных импульсов. Каждому -полю микрокоманды соответствует один дещифратор 4, один блок 5 формирования приемов и один блок 6 фООмированяя выдач. Схема сравнения 7 вырабатывает сигнал совпадения (логическую единицу) в том случае, когда а.дрес ячейки памяти, набранный на клавищном регистре 2. совпадает с содержимым регистра алреса 19 оперативного запоминающего устройства. Триггеры 8 и 9, а также элементы 10-13 служат для обеспечения режима работы «Индикация ячейкИ . Элементы синхронизации 15 и 18 предназначены для выработки требуемой временной последовательности вмпульсов приема информации в :регистры с Oi6щей магистрали. Синхронизирлющие импульсы вырабатываются распределителем импульсов 1. На вход 28 из микропрограммного УСТрОйства управления (на чертеже не показано) подается сигнал, равный единице, если процессор находится в состоянии «Останов, и равный нулю в противиом случае. Ниже рассмотрен принцип действия процессора. В режиме «Индикация регистра сигнал в точке 26 равен единице, сигналы в точках 27 и 28 равны нулю. При выполнении очередной микрокоманды может оказаться, что один или несколько блоков 5 вырабатывают сигналы приема в выбранный регистр по некоторым функциональным импульсам. В этом случае элементы 23 вырабатывают сигналы совладения, которые после прохождения через элементы 25 и 15 вызывают приемы информации в регистр индикации 16 с общей магистрали одновременно с приема1ми информации с той же магистрали в выбранный регистр. Таким образом, информ.ация в регистре индикации 16 дублирует инфор1мацию, хранящуюся в выбранном регистре, и с помощью блоков индикации 17. например светодиодов, вывоидится на пульт управления для визуального на блюдения. В режиме «Индикация ячейки памяти сигнал в точке 27 равен единице, сигналы в точках 26 и 28 нулю. При выполнении микрокоманды «Чтение из памяти один пз разрядов регистра сигналов обмена с оперативным запоминающим устройством, а именно разряд «Чтение из памяти, устанавливается в единицу. Если при этом содержимое регистра 19 адреса оперативного запоминающего устройства совпадает с адресом выбра-нной ячейки па;мяти, набранным на клавишном регистре 2, то сигнал с выхода элемента «И 12 устанавливает триггер 8 в единицу, подготавливая к работе элементы «И 24. Считанная из оперативного за-по.минающего устройства информация передается в выходной регистр памяти (один из регистров 21). Выдача информации с этого регистра в общую магистраль осуществляется при выполнении одной из последующих макрокоманд, в которых в качестве «регистра-передатчика указан выходной регистр памяти, а в качестве «регистра-приемника любой регистр структуры (за исключением регистров 2 и 16) или их сочетание. При появлении на регистре 3 первой микроком.анды указанного типа сигналы выдачи содержимого выходного регистра памяти, формируемые блока1ми 6, проходят через элементы 24, 25 и 15и вызывают приемы в регистр индикации 16одновременно с приемами в «регистры-прибмники. Таким образом, в данном режиме регистр иняикапии 16 дублирует информацию в выбранной ячейке оперативного запоминающего устройства. Сброс триггера 8 осуп1ествляе.тся следующим об.разом. Сигналы выдачи содержимого выхолного регистра проходят через ялемент «ИЛИ 13. а затем через элемент «И 10 (ПОСКОЛЬКУ на второй вход элемента 10 пост -пает елиничный с.игнал с выхода триггера 8 и лттанавливают триггер 9 в единицу, элемент «И 11 открывается в конце выполнения микрокоманды и у станавливает триггер 8 в нуль. При выполнении следмощей микрокоманды, если она не является микрокомандой чтения из выбранной ячейки памяти, в триггер 9 также заносится нуль. Еслн слеллющая микрокоманда является микрокомандой чтения из выбранной ячейки памяти, то триггер 8 снова устанавливается в единицу, и процесс передачи информации из ячейки памяти в регистр индикации 16 повторяется. В режиме «Останов регистр индикации дублирлет инфop тгцию в выбранном регистре независилю от логического состояния входов 26 и 27. В этом режиме сигнал на входе 28 равен единице, на выходах распределителя ИМПУЛЬСОВ 1 и на выходах элементов 25 постоянно присутствуют логические единицы, что приводит к ПОСТОЯННОМУ разращению приема в регистр индикации 16 с магистрали. Сигнал на входе 28 блокирует дешифраторы 4, т. е. запрещает расшифровку всех полей регистра 3 микрокоманды и осуществляет выдачу содержимого выбранного регистра в процессорную магистраль, воздействуя на входы блоков 6. Таким образом, в режиме «Останов содержимое выбранного регистра псстоянно выдается в общую магистраль и заносится в регистр :1 ЛИКаЦИИ. применение предлагаемых процессоров в составе малых и средних вычислительных машин позволяет выводить требуемую инфорнацию на регистр ивдикации без СНиженяя быстродействия машины.

Ф о ip м } л а и 3 о б р е тен и я

Процессор, -содержащий распределитель импульсов, регистр .микрокоманды, соединенный через дешифраторы с блоками формирования приемов и выдач, (межрегистровую магистраль, 1ПО:Д«люченную К клавишному регистру информа/ции, регистру адреса 0Пе1рати1В«ого запомигаающего устройства, регистру €игна,лов обмена с оперативным запоминающим устройством, выходному регистру опепативного заноминаюнтего устройства, блоку регистров Общего н.азначения и регистру пндт кации с ПОДкл оче ны;МИ к его выхода1М элементами инди.кации, схему сравнения, входы которой соелинены с выходом .клавишного регистра шгфо10 ма ПИИ и выходом регистра адреса ооеративяого запоминающего устройства, клавишный регистр адреса, выход (которого соединен с входом блОКа фор гирования выдач, выход которого соединен с входом межрегистровой магистрали, первый элемент «И, входы которого соединены соответственно с выходами блоков Лормироваиия приемов и выходом распределителя импульсов, а выход соединен с входом межрегистровой магистрали, о т л и ч а ЮЩ и и с я тем, что, с целью повышения быстродействия, процессор содержит блоки управления индикэашей, два триггера, элементы «И, элементы «ИЛИ, причем выходы клавишного регистр.а адреса соединены 1C нерв.ой группой входов блоков управления индикацией, вторая группа входов блоков управления индикаатией соединена с выхода МИ соответствуюп1их блоков формирования приемов, третья группа входов блоков управления .индикацией соединена с первым управляющим входом процессора, четвертая

группа ВХО.ДО.В блоков управления индикацией со.едине:на с единичным выходом .первого триггера и с первьш входом второго элемента «И, пятая группа входов блоков управления индинацией соединена с выхода1ми соответствующих блоков формирования выдач и с входами элемента «ИЛИ, .шестая группа входов блоков управления индикацией соединена с вторым управляющим вхо.дом процессора, выход

элемента «ИЛИ соединен с вторы входом второго элемента «И, выход которого соединен с единичным вхо.дом второго триггера, выход которого соединен -с первы М входом третьего элемента «И, выход .которого соединен с

нулевым входом первого триггера, единичный вход первого триггера соединен с выходом четвертого элемента «И, первый .вход которого соединен с выходо1М схемы .сравнения, а второй-с выходом одного из разрядов реги.стра си1гнало1в о.б.мена с оперативным заноми(Нающим устройством, выходы блоков управления индикацией соединены с входами пятого элемента «И, выход которого соединен iC упра-вляющим вхо.дом регистра индикации, управляющий вход распр.еделителя импульсо.в объединен с управляющими входами бло.ков управления шгдикацией, упраеляющими входами блоков формирования выдач, вхо.да1ми блокировки деш:ифраторов и соединен с третьим управляющим входом процесс.ор.а, выход распределителя импульсов соединен с входами третьего, четвертого и пятого элементов «И и с нулевым входом второго триггера. Источники информации, принятые во внимание при экспертизе:

I. Система резервирования и продажи билетов для пассажиров Московского авиаузла «Сирена-1. Технический проект. Том. II, стр. 1-43-152. НИИУВМ, Северо.донец К, 1967.

2. Патент США № 3750105, кл. 340-172. 5, 29.05.73.

| название | год | авторы | номер документа |

|---|---|---|---|

| Процессор | 1979 |

|

SU783795A2 |

| Процессор | 1974 |

|

SU526902A1 |

| Устройство для обучения | 1988 |

|

SU1663618A1 |

| Устройство для обмена информацией междуэлЕКТРОННОй ВычиСлиТЕльНОй МАшиНОй(эВМ) и уСТРОйСТВАМи ВВОдА и ВыВОдА | 1979 |

|

SU809140A1 |

| Процессор матричной вычислительной системы | 1987 |

|

SU1603395A1 |

| Мультиплексный канал | 1980 |

|

SU957199A1 |

| Микропрограммное устройство для управления и обмена данными | 1983 |

|

SU1129601A1 |

| Адаптивное вычислительное устройство | 1980 |

|

SU957214A1 |

| Микропрограммный процессор | 1982 |

|

SU1070557A1 |

| Процессор программируемого контроллера | 1985 |

|

SU1406595A1 |

Авторы

Даты

1976-08-30—Публикация

1974-10-07—Подача