(54)-ПРОЦЕССОР

1

Устройство относится к области вычислительной техники, может быть использовано при проектировании электронных цифровых вычислительных машин и является усовершенствованием известного устройства по авт. св. № 526900.

В основном изобретении по авт.св. № 526900 описан процессор 1 содержащий распределитель импульсов, регистр микрокоманды, блоки формирования приемов и выдач,клавишный регистр, клавишный регистр информации, регистр адреса запоминающего устройства, регистр сигналов обмена с оперативным запоминаисщим устройством, регистр индикации и блок регистров общего назначения . При этом все регистры подключены к межрегистровой магистрали, к которой подключены блоки формирования приемов и выдач, которые соединены с регистром микрокоманд.

Целью изобретения является повышение достоверности функционирования процессора.

Для достижения указанной цели в устройство по авт. св. 526900 введены регистр ошибок, регистр контрольных кодов, формирователь сигнала ошибки, элемент И, элемент ИЛИ и блок прерываний, выход которого соединен с входом блок|1 микропрограммного управления. Входы регистра

5 контрольных кодов подключены к выходам блока микропрограммного управления, а выходы регистра контрольных кодов - к межрегистровой магистрали, к которой подключен формирователь

0 сигнала ошибки, выходом соединенный с первым входом элемента И, второй вход которого связан с выходом элемента ИЛИ, подключенного своими входами к выходам блока формирования

15 приемов. При этом выход элемента И соединен с входом блока прерываний и с входом разрешения записи регистра ошибок, информационные входы которого подключены к выходам блока формирования вьщач, а выходы регистра ошибок подсоединены к межрегистровой магистрали.

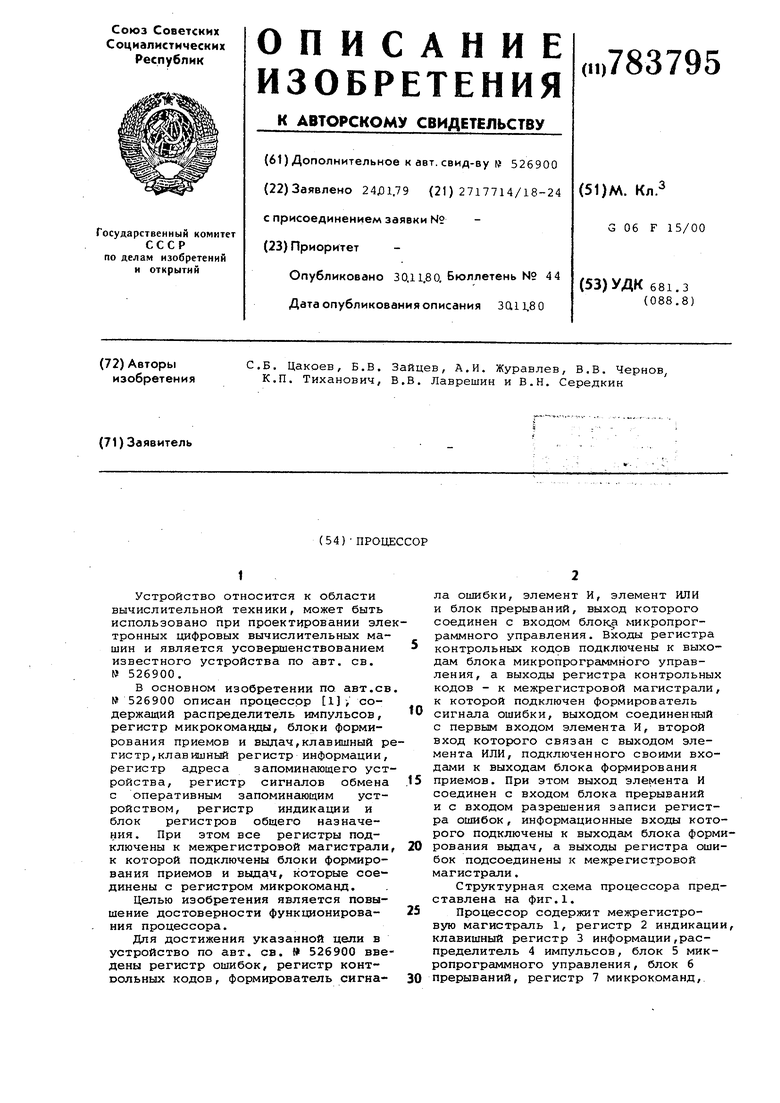

Структурная схема процессора представлена на фиг.1.

25 Процессор содержит межрегистровую магистраль 1, регистр 2 индикации, клавишный регистр 3 информации,распределитель 4 импульсов, блок 5 микропрограммного управления, блок 6

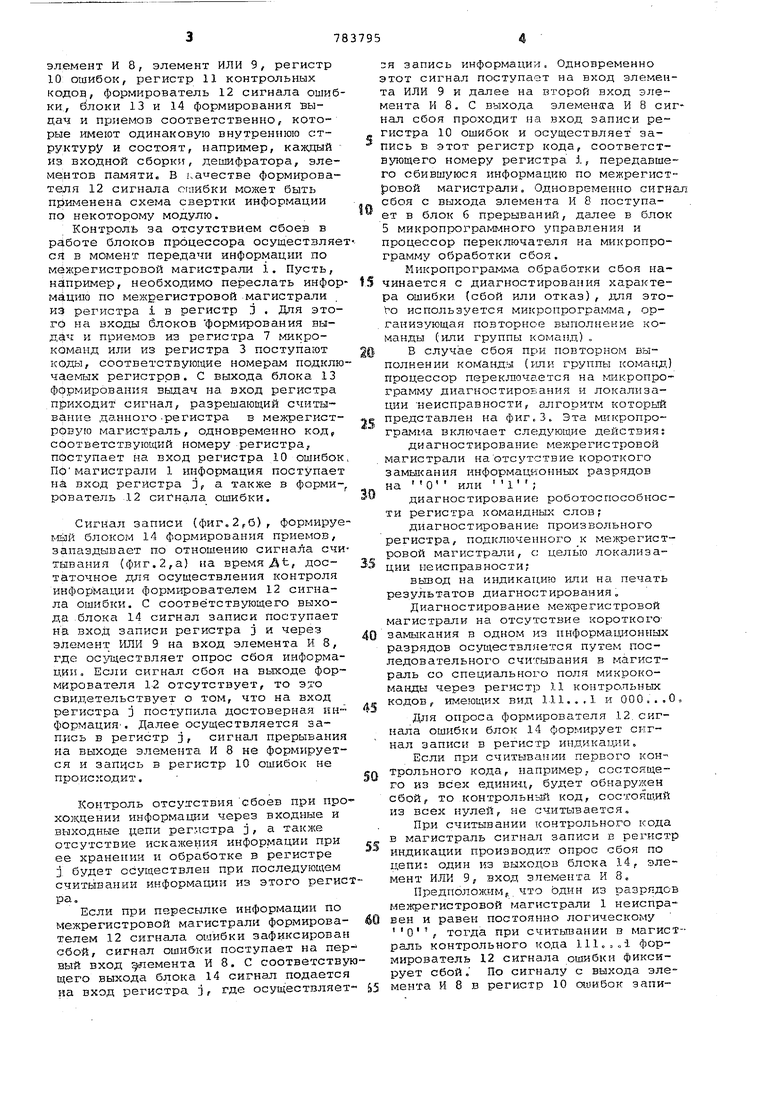

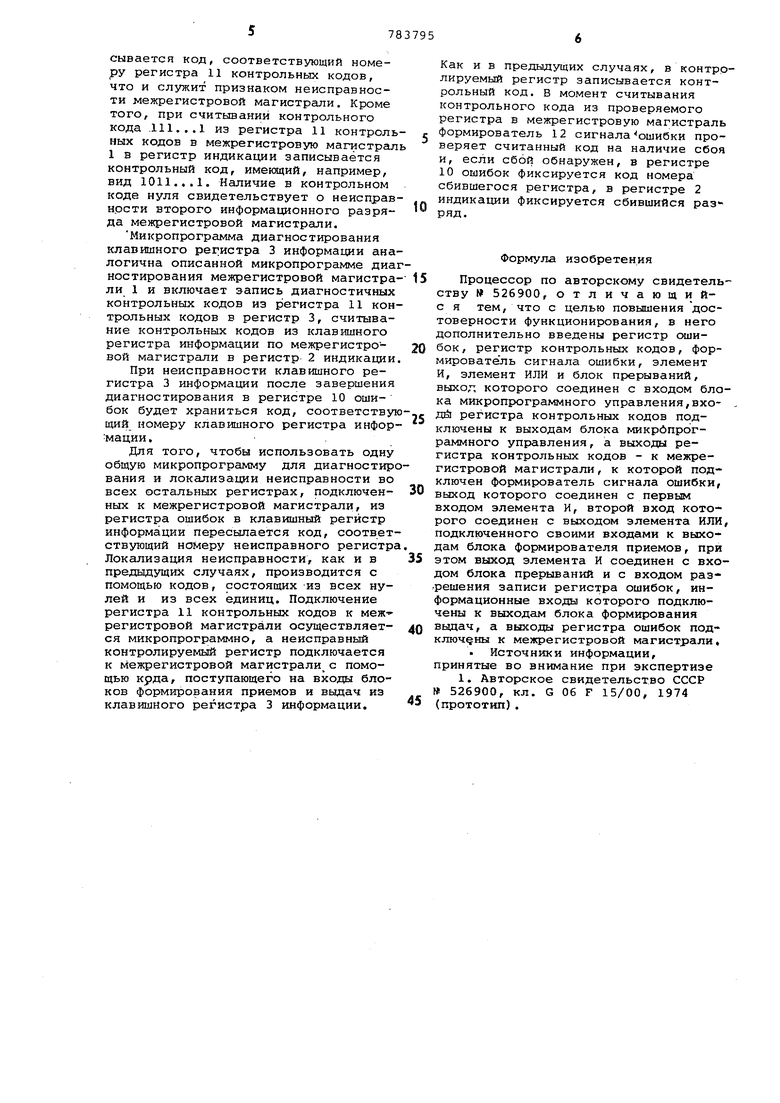

30 прерываний, регистр 7 микрокоманд. элемент И 8, элемент ИЛИ 9, регистр 10 ошибок, регистр 11 контрольных кодов, формирователь 12 сигнала ошиб ки,, блоки 13 и 14 формирования выдач и приемов соответственно, которые имеют одинаковую внутреннюю структуру и состоят, например, каждый из входной сборки, деитфратора, элементов памяти. В |.а естве формирователя 12 сигнала сшибки может быть пpи / eнeнa схема свертки информации по некоторому модулю. Контроль за отсутствием сбоев в работе блоков процессора осуществляе ся в момент передачи информации по межрегистровой магистрали 1. Пусть, например, необходимо переслать инфор мадию по межрегистровой м агистрали из регистра i в регистр j , Для этого на входы блоков формирования вырЛч и приемов из регистра 7 микрокоманд или из регистра 3 поступают коды, соответствующие номерам подклю чаемых регистров. С выхода блока 13 Формирования вьздач на. вход регистра приходит сигнал, разрешающий считывание данного-регистра в межрегистровую магистраль, одновременно код, соответствующий номеру регистра, поступает на вход регистра 10 ошибок ПО магистрали 1 информация поступает на вход регистра j, а также в формирователь 12 сигнала ошибки. Сигнал записи (фиг„2рб), формируе мйй блоком 14 формирования приемов, запаздывает по отношению сигнала счи тывания (фиг. 2,а) на время At, достаточное для осуществления контроля информации формирователем 12 сигнала ошибки. С соответствующего выхода блока 14 сигнал записи поступает на вкоД записи регистра j и через элемент J-UIH 9 на вход элемента И 8, где осуществляет опрос сбоя информации Если сигнал сбоя на выходе формирователя 12 отсутствует, то это свидетельствует о том, что на вход регистра j поступила достоверная информация. Далее осуществляется запись в регистр j, сигнал прерывания на выходе элемента И 8 не формируется и запись в регистр 10 ошибок не происходит. Контроль отсутствия сбоев при про хозкдении информации через входные и выходные цепи регистра j, а также отсутствие искажения информации при ее хранении и обработке в регистре j будет осуществлен при последующем считывании информации из этого регис ра. Если при пересылке информации по межрегистровой магистрали формирова телам 12 сигнала ошибки зафиксирова сбой, сигнал ошн&ки поступает на пер вый вход цемента И 8. С соответств щего выхода блока 14 сигнал подаетс ка вход регистра j г где осуществляе зи запись информации. Одновременно тот сигнал поступает на вход элемента ИЛИ 9 и далее на второй вход элемента И 8. С выхода элемента И 8 сигнал сбоя проходит на вход записи регистра 10 ошибок и осуществляет запись в этот регистр кода, соответствующего номеру регистра i, передавшего сбившуюся информацию по межрегистровой магистрали. Одновременно сигнал сбоя с выхода элемента И 8 поступает в блок б прерываний, далее в блок 5 MHKponporpafvsr-iHoro 5правления и процессор переключателя на микропрограмму обработки сбоя. Микропрограмма обработки сбоя начинается с диагностирования характера ошибки {сбой или отказ), для этоVo используется микропрограмма, организующая повторное выполнение команды (или группы команд), В случае сбоя при повторном выполнении команды (или группы команд) процессор переключается на кмкропрограмму диагностирования и локализации неисправности, алгоритм который представлен на фиг,3. Эта микропрограмма включает следующие действия; диагностирование межрегистровой магистрали на отсутствие короткого замыкания информационных разрядов на О или 1 ; диагностирование роботоспособности регистра командных слов диагностирование; произвольного регистра, подключенного к межрегистровой магистрали, с целью локализации неисправности; вывод на индикап,ию или на. печать результатов диагностирования„ Диагностирование мехфегистровой магистрали на отсутствие короткогозамыкания в одном из информаш онных разрядов осуществляется путем последовательного считывания в магистраль со специального поля микрокомагвды через регистр 11 контрольных кодов f имеющих вид 111,,, и 000 ... О , Для опроса формирователя 12. сигнала ошибки блок 14 формирует сигнал записи в регистр шщикац;- и„ Если при считывании первого коН трольного кода, например, состояодего из всех едини-ц будет обнаружен сбой, то контрольныг1 код, состоящ,ий из всех нулей, не считывается. При считывании контрольного кода в магистраль сигнал записи в регистр индикации производит опрос сбоя по цепи: один из выхо.цов блока 14, элемент ИЛИ 9, вход элемента И 8. Предположим что Один из разрядов межрегистровой магистрали 1 неисправен и равен постоянно логическому О, тогда при считывании в магистраль контрольного кода 111 „ oi формирователь 12 сигнала ошибки фиксирует сбой. По сигналу с выхода элемента И 8 в регистр 10 оюибок записывается код, соответствующий номеру регистра 11 контрольных кодов, что и служит признаком неисправности межрегистровой магистрали. Кроме того, при считьшаний контрольного кода .111...1 из регистра 11 контрольных кодов в межрегистровую магистрал 1 в регистр индикации записывается контрольный код, имеющий, например, вид 1011...1. Наличие в контрольном коде нуля свидетельствует о неисправности второго информационного разряда межрегистровой магистрали.

Микропрограмма диагностирования клавишного регистра 3 информации аналогична описанной микропрограмме диагностирования межрегистровой магистрали 1 и включает запись диагностичных контрольных кодов из регистра 11 контрольных кодов в регистр 3, считывание контрольных кодов из клавишного регистра информации по межрегистровой магистрали в регистр 2 индикации

При неисправности клавишного регистра 3 информации после завершения диагностирования в регистре 10 ошибок будет храниться код, соответствующий номеру клавишного регистра информации.

Для того, чтобы использовать одну общую микропрограмму для диагностирования и локализации неисправности во всех остальных регистрах, подключенных к межрегистровой магистрали, из регистра ошибок в клавишный регистр информации пересылается код, соответствующий номеру неисправного регистра Локализация неисправности, как и в предыдущих случаях, производится с помощью кодов, состоящих из всех нулей и из всех единиц. Подключение регистра 11 контрольных кодов к меж регистровой магистрали осуществляется микропрограммно, а неисправный контролируемый регистр подключается к межрегистровой магистрали с помощью крда, поступающего на входы блоков формирования приемов и выдач из клавишного регистра 3 информации.

Как и в предыдущих случаях, в контролируемый регистр записывается контрольный код. в момент считывания контрольного кода из проверяемого регистра в межрегистровую магистраль формирователь 12 сигнала ошибки проверяет считанный код на наличие сбоя и, если сбой обнаружен, в регистре 10 ошибок фиксируется код номера сбившегося регистра, в регистре 2 индикации фиксируется сбившийся разряд.

Формула изобретения

5

Процессор по авторскому свидетельству 526900, отличающийс я тем, что с целью повышения достоверности функционирования, в него дополнительно введены регистр ошибок , регистр контрольных кодов, фор0мирователь сигнала ошибки, элемент И, элемент ИЛИ и блок прерываний, выхол которого соединен с входом блока микропрограммного управления,вхо- . дй регистра контрольных кодов под5ключены к выходам блока микрбпрограммного управления, а выходы регистра контрольных кодов - к межрегистровой магистрали, к которой подключен формирователь сигнала ошибки,

0 ВЕлход которого соединен с первым входом элемента И, второй вход которого соединен с выходом элемента ИЛИ, подключенного своими входами к выходам блока формирователя приемов, при

5 этом выход элемента И соединен с входом блока прерываний и с входом раз-решения записи регистра ошибок, информационные входы которого подключены к выходам блока формирования выдач, а выходы регистра ошибок под0 к межрегистровой магистрали.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР 526900, кл. G 06 F 15/00, 1974

5 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обучения | 1987 |

|

SU1559366A1 |

| Устройство для сопряжения ЭВМ с накопителями на магнитных дисках | 1985 |

|

SU1280644A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1130865A1 |

| Устройство для сопряжения электронно-вычислительной машины с группой внешних устройств | 1989 |

|

SU1734098A1 |

| Многоканальная система для контроля и диагностики цифровых блоков | 1984 |

|

SU1269137A1 |

| Микропрограммное устройство управления с контролем | 1983 |

|

SU1270772A1 |

| Запоминающее устройство | 1987 |

|

SU1495849A1 |

| Многопроцессорная система | 1989 |

|

SU1686455A1 |

| Оперативное запоминающее устройство с исправлением ошибок | 1988 |

|

SU1674269A1 |

| Устройство для сопряжения ЭВМ с накопителем на магнитных дисках | 1986 |

|

SU1410046A1 |

Авторы

Даты

1980-11-30—Публикация

1979-01-24—Подача