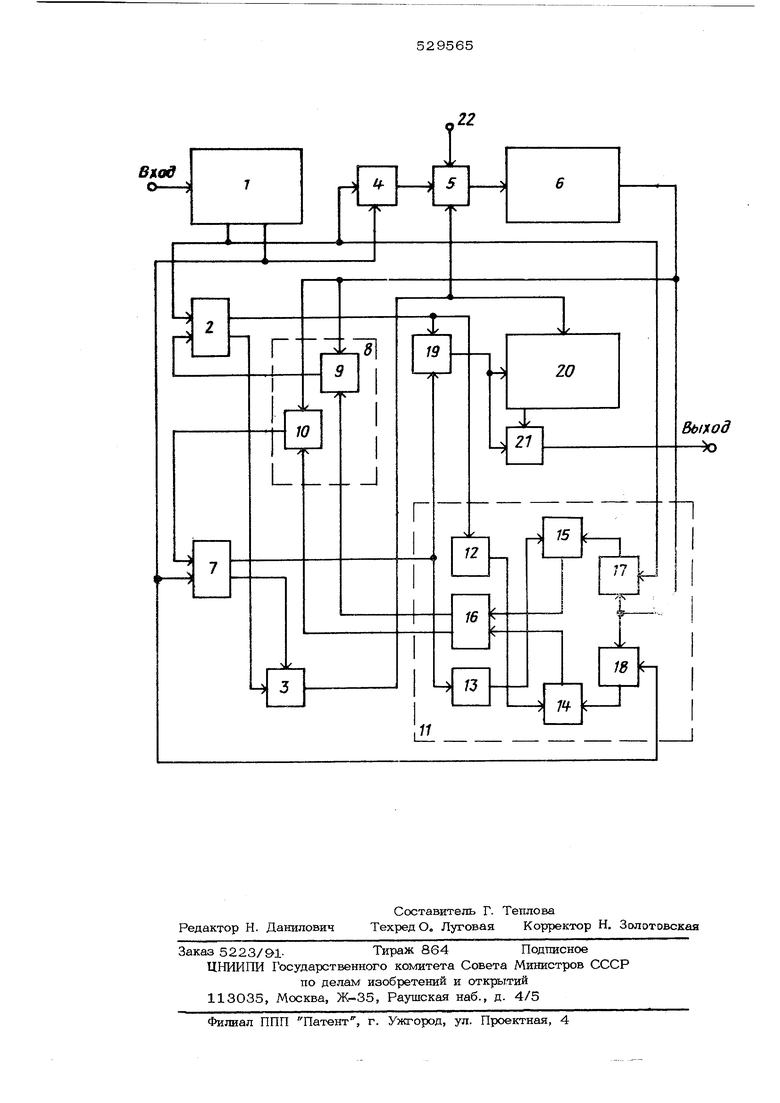

лов управления, при этом выход делителя тактовой частоты подключен к входам узла коммутации, а через узел формирования сш налов управления, узел коммутации8 анализирующий узел синхрогруппы первого вида, третий элемент ИЛИ - к соответствующим входам узла формирования сигналов управления, решающего узла и узла фазирования приемного распределителя, причем второй выход узла коммутации подключен через анализирующий узел синхрогруппы второго вида, соединенный с узлом формирования сигналов управления, и первый элемент ИЛИ к вторым входам узла управления и решающего узла. Таким образом, время обнаружения сийх росигнала, передаваемого в виде последовательности чередующихся синхрогрупп ДВУХ видов, уменьшается, так как осуществляет- зя взаимозависимый поиск этих синхрогруп На чертеже дана структурная электрическая схема устройства. Устройство синхронизации по циклам содержит дешифратор 1 синхрогруппы, один выход которого подключен через анализирующий узел 2 синхрогруппы первого вида к входу первого элемента ИЛИ 3, а через второй элемент ИЛИ 4, узел управления 3 - к входу деШГтеля 6 тактовой частоты, второй выход дешифратора 1 подключен к второму входу второго элемента ИЛИ 4и к входу анализирующего узла 7 синхрогруппы BTOpoi o вида, выход делителя 6 подключен к входам узла коммутации 8, состоящего из элементов И 9 и 10, а через узел формирования 11 сигналов управления, состоящий из элементов задержки 12, 13, эломентов ИЛИ 14 и 15, триггер 16 и Элементов И 17 и 18, узел коммутации 8, анализирующий узел 2-к соответствующему входу узла формироваш-гя 11 и дополнительно через третий элемент ИЛ 1 9 - к соответствующим входам последовательно соединенных решающего узла 20 и узла фазирования 21 приемного распределителя., причем второй выход узла формиро вания 11 подключен через узел коммутаций 8, анализирующий узел 7, соединенный с узлом формирования 11. и первый элемент ИЛИ 3 к вторым входак узла управления 5 и решающего узла 20. Узел формирования 11 соединен также непосредствен}ю с дешифратором 1, анализирующим узлом 7 и вторым входом третьего элемента ИЛИ 19 Вход дешифратора 1 и выход узла фазирования 21 являются соответственно входом и выходом устройства, вход 22 узла управлени 5является входом импульсов тактовой часУстройство работает следующим образом Импульсно-кодовый сшнал с входа устройства поступает на дешифратор 1, на вы- ходе которого образую1тся сигналы откликов как на синхрогруппы, так и на кодовые группы информационного сигнала, сходные с синхрогруппами. Выселенные дешифратором 1 сигналы поступают через второй элемент ИЛИ 4 на вход узла управления 5, соответствующий запуску делителя 6. При регулярном поступлении импульсов тактовой частоты с входа 22 через узел управления 5 на вход делителя 6 на его выходе формируется последовательность импульсов опробования, длительностью в период тактовой частоты и следующих с частотой циклов. В установивщемся режиме отклик на синхрогруттау первого вида с выхода дешифратора 1 поступает на вход анализирующего узла 2 в тот момент, когда на другой его вход через открытый элемент И 9 узла коммутации 8 с делителя 6 приходит импульс опробования. В этом случае сигнал повторения с выхода анализирующего узла 2 через третий элемент ИЛИ 1 9 проходит на вход записи фиксации состояния синхронизма в рещающем узле 20 и на вход узла фазирования 21. Кроме того, сигнал повторения с выхода анализирующего узла 2, задержанный на элементе задержки 12 узла формирования 11, проходит элемент ИЛИ 14 и переключает триггер 16 в положение, разрешающее в следующем цикле прохождение импульса опробования с делителя 6 через элемент И 10 узла коммут-апии 8 на вход, анализирующего узла 7 и запрещающее через элемент И 9 на вход анализирующего узла 2. В следующем цикле в результате появления на выходе дешифратора 1 отклика на синхрогрзшпу второго ви.ца аналогично происходит переключение триггера 16 в исходное положеьгие сигналом повторения с выхода анализирующего узла 7 через элемент задерЖ1си 13 и элемент ИЛИ 15, т.е. происходит подготовка устройства к приему в следующем цикле синхрогруппы первого вида. В случае потери синхронизма устройством (отсутствие на выходе дешифратора 1 ожидаемого отклика) на выходе подготовленного к опробованию анализирующего узла 2 или 7 формируется сигнал ошибки, который через первый элемент ИЛИ 3 поступает на вход сброса решающего узла 20 и на вход узла управления 5, запрещающий поступление импульсов тактовой частоты на вход делителя 6, т.е. делитель останавливается в положении, соответствующем моменту опробования, а ааементы И 17 и 18 остаются открытыми.

В режкК е поиска первый :ке из откликов на любило синхрогруппу клг се имитацию импульсами икформационкотю сигнала, появившийся на выходе дешифратора 1, пес тупает на соответствующий анализирующий узел 2 или 7 и на запуск де-лителя 6.

Этот отклик проходит соответстзуюшие элементы И 17 либо 18 и элемент РШИ 14, либо 15 узла формирования 11 и про-изводит установку триггера 16 в положение, открывающее элемент И 9 10 узла коммутации 8, пропускающий сигнал с делителя 6 на тот анализирующий узел 2 и 7j на вход которого пришел отклик с дешифратора 1.

Образ тощийся сигнал повторения, соот-ветствующи ; дешифруемой синхрогруптю, через третий эпекгент ИЛИ 1 9 поступает на вход записи решающего узла 20,

Кроме того. .З.Пдержанный сигнал повт рения чере.з соотвегствуюший элемент ИЛИ 14 либо 15 в узле формирования 11 осуществляет переброс триггера 16 в состояние, в котором устройство готово к приему в следующем синхгхзгруп-. пы.

Пос.пе фиксации состояния синхронизма решающим оп:;, , 2 О с узла фазирования 2. L, хочоры: открыт в установиБшемся режнлШ; поступает вмпульс для подстройки приемного расг;шде.гогг: 11я.

Формул а 5ды которого подключены через анализирующий узел синхрогруппы первого вида к входу первого элемента ИЛИ, к входу анализи рующего узла синхрогруппы второго вида, а через второй элемент ИЛИ, узел управления -. к входу делителя тактовой частоты, а также последовательно соединенные решающий узел и узел фазирования приемного распределителя, отличающеес я тем, что, с целью уменьшения времени обнаружения синхрогруппы, введены третий элемент ИЛИ, узел коммутации, узел формирования сигналов управления, при этом выход делителя тактовой частоты подключен к входам узла коммутации, а через узел формирозаш1Я сигналов управления, узел коммуташш, анали:зирую11щй узел синхрогруппы первого вида, третий элемент ИЛИ - к соответствуьощим входам узла формирования С1ггналов управления, решающего узла и узла фазирования приемного распределителя, причем второй выход узла коммутации подключен через анализирующий узел синхрогруппы второго вида, соединенный с узлом формирования сигналов управления, и первый элемент ИЛИ к вторым входам узла управления и решающего узла.

Источники информации, принятые во внимание при экспертизе:

1.Гуревич В. Э. и др. Импульсно-кодовая модуляция в многоканальной телефонной связи. М., Связь, 1973, с.24О.

2.Патент ФРГ № 1142921, класс 21а 49, 1963 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство синхронизации по циклам | 1975 |

|

SU544160A1 |

| Устройство синхронизации по циклам | 1989 |

|

SU1672579A2 |

| Устройство синхронизации по циклам | 1990 |

|

SU1809543A1 |

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2005 |

|

RU2284665C1 |

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2007 |

|

RU2348117C1 |

| УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ ПО ЦИКЛАМ | 2003 |

|

RU2231228C1 |

| УСТРОЙСТВО для СИНХРОНИЗАЦИИ | 1971 |

|

SU305578A1 |

| УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ ПО ЦИКЛАМ | 2002 |

|

RU2239953C2 |

| УСТРОЙСТВО ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2021 |

|

RU2782473C1 |

| Приемное устройство циклового фазирования | 1983 |

|

SU1085006A1 |

Авторы

Даты

1976-09-25—Публикация

1975-06-09—Подача