1

Изобретение относится к цифровой вычислительной технике.

Известны вычислительные системы, содержащие устройства обработки, первые управляющие выходы которых соединены с соответствующими первыми входами блока анализа занятости устройств обработки, оперативное запоминающее устройство, входы и выходы которого через первый коммутатор соединены с первыми выходами и входами сверхоперативных запоминающих устройств, вторые входы и выходы которых соединены с первыми выходами и входами соответствующих устройств управления, соединенных вторыми входами и выходами с первыми выходами и входами соответствующих блоков хранения слова состояния программы.

Недостаточно высокая производительност таких систем обусловлена необходимостью использования операционной системы для распределения вычислительных ресурсов при организации мультипрограммной работы.

Цель изобретения - повыщение производительности вычислительной системы,

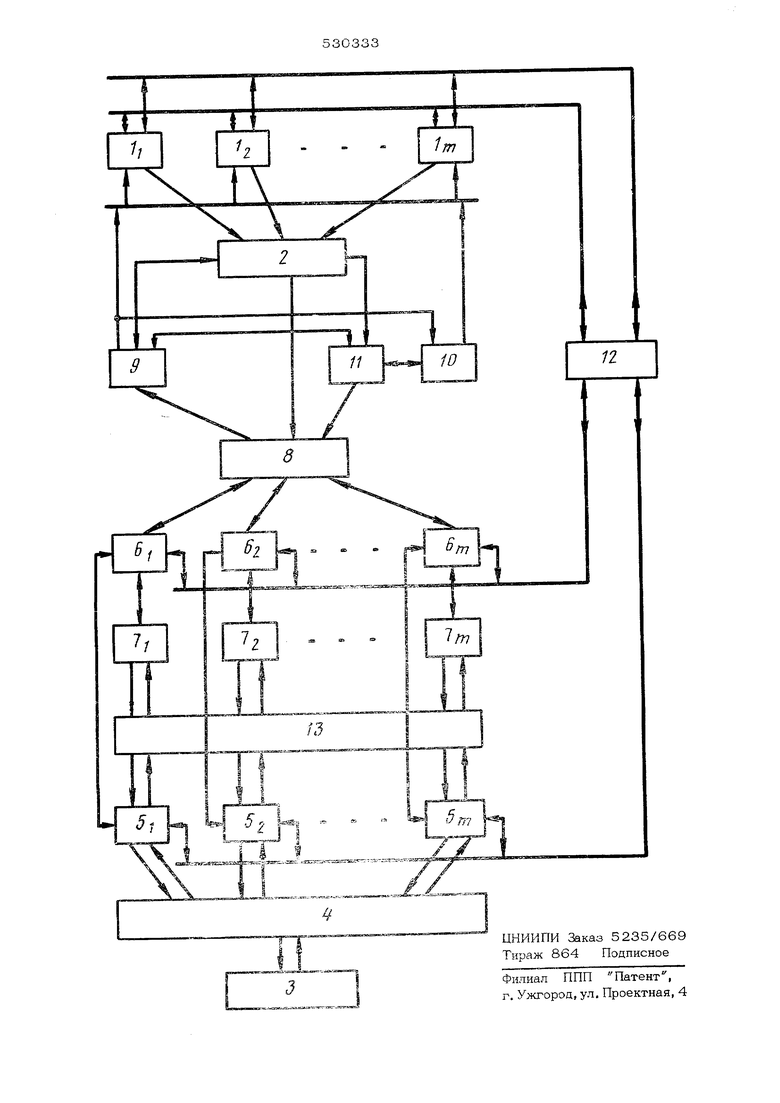

Это достигается тем, что предлагаемая вычислительная система содержит блок выбора приоритетных устройств управления, первые входы и выходы которого соединены с третьи.мп выходами и входами соответствующих устройств управления, а вторые входы подключены к первому выходу блока анализа занятости устройств обработки, блок классификации комаг.д, первые входы которого подключены к вторым выходам блока выбора приоритетных устройств управления, первые выходы соединены с первыми входами устройств обработки, а вторые входы и выходы соединены с вторыми выходами и входами блока анализа занятости устройств обработки, блок памяти невыполненных команд, первые выходы которого coeдшieны с первыми входами устройств обработки, а первые входы подключены к первым выходам блока классификации команд, блок анализа памяти невыполненных команд, первые входы и выходы которого соединены с вторыми выходами и входами блока памяти невыполненных команд, вторые входы и выходы соединены с третьими выходами и входами блока классификации команд, третий вход подключен к третьему выходу блока анализа занятости устройств обработки, а третий выход соединен с третьим входом б ка выбора приоритетного устройства управл«ния, Второй коммутатор, первые информационные и управляющие входы и выходы ко торого соединены с вторыми и третьими вы ходами и входами устройств обработки соответственно, а вторые информационные и управляющие входы и выходы соединены с третьими выходами и входами сверхоперативных запоминающих устройств и четвертыми выходами и входами устройств управ ления соответственно, и третий коммутатор включенный между вторыми входами и выходами блоков хранения слова состояния программы и четвертыми выходами и входами сверхоперативных запоминающих устройств. На чертеже представлена схема предлагаемой вычислительной системы. Вычислительная система содержит устройства обработки 1, - 1;„, первые управлязощие выходы которых соединены с соответствующими первыми входами блока 2 ан лиза занятости устройств обработки, опера тивное запоминающее устройство 3, входы и выходы которого через коммутатор 4 со динены с первыми выходами и входа 1и сверхоперативных запоминающих устройств 5 - 5( вторые входы и выходы которых соединены с первыми выходами и входами соответствующих устройств управления 6, 6, соедш1енных вторыми входами и выходами с первыми выходами и входами соответствующих блоков 7, - 7, хранения слова состояния программы, Кроме того, в состав системы входит блок 8 выбора приоритетных устройств управления, первые входы и выходы которого соедш-1елы с третьими выходами и входами саответству1ощ.их устройств управления 6 f 6, а вторые входы подключены к первому выходу блока 2 анализа занятости устройст обработки, блок классификации команд 9, первые входы которого подк.шэчель к вторым выходам блока выбора 8 приоритет}1Ы.х устройств управления, первые выходы соединены с первыми входами устройств обработки,,,, а вторые входы и выходы соединены с вторыми выходами п входами блока 2 анализа занятости устройств обработки; блок 10 памяги невыполненных команд, первые выходы которого соединены с первыми входами устройств обработки 1 , 1, а первые входы подключены к первым выходам блока классификации команд 9; блок 11 анали за памяти невыполне.)1лых команд, нервые входы и выходы которого соединены с вторыми выходами и входами блока 10 памяти невыполненных команд, вторые входы и выходы соединены с 1ретьими выходами и входами блока классификации команд 9, третий вход подключен к третьему выходу блока аршлиза 2 занятости устройств обработки, а третий выход соединен с третьим вxoдo. блока 8 выбора приоритетных ycTpoiiCTB управления; коммутатор 12, первые информационные и управляющие входы и выходы которого соединены с вторыми и третьими выходами и входами устройств обработки 1 - IfT) соответственно, а вторые информационные и управляющие входы и выходы соединены с третьими выходами и входами сверхоперативных запоминающих устройств Sj - 5m и четвертыми выходами и входами устройств управления 6 6несоответственно, и коммутатор 13, включенный между вторыми входами и выходами блоков 7-| - 7гп хранения слова состояния нрограммы и четвертыми выходами и входами сверхоперативных запоминающих устройств Вычислительная система работает следующим образом. Все нрограммы рещаемых задач и массивы обрабатываемых чисел разбить; на блоки и хранятся в оперативном запоминающем устройстве 3. По мере рещения задачи по запросу от устройств управления 6,6 у,очередные блоки программы и массивов чисел через коммутатор 4 передаются в соответствующие сверхоперативные запоминающие устройства 5 - 5, Устройства управления 6 - 617 непосредственно или через коммутатор 12 и соответствующий блок 7 - 7fy, хранения слова состояния программы выбирают очередную команду блока программы из соответствующего сверхоперативного запоминающего устройства 5-1 - 5|-р. Эта команда запоминается в соответствующем блоке хранения слова состояния программы, а устройство управления 6 , 6 I... нли 6, вызвавщее команду, производит ее обработку (модифицирует адреса операндов, определяет физические адреса операндов). После окончания обработки устройство управления 6р G, ,„. или передает сфор1 ;нрованные адреса операндов в соотгзетстврэщий блок 7 , 7, ... или 7|. хранения слова состояния программы и подает на блок 8 выбора приоритетных устройств управления запрос на выполнение подготовленной команды. Если блок выбора приор;- - тетных устройств управления свободен, то устройство управления, послави1ее запрос, передает на него код операции, номер команды и свой номер. Эта информация поступает на блок классификации команд 9, который по ходу команды определяет группу устройств обработки 1 - 1т которые физпчески могут выполнить эту команду. После этого блок классификации команд 9 за пускает блок 2 анализа занятости устройст обработки. Если хотя бы одно из устройств обработки 1 - 1, входящих в группу, определенную блоком классификации команд 9, свободно, блок 2 анализа занятости устройств обработки подключает выходь блока классификации команд 9 к этому естройству обработки 1 j . В это устройств передаются код операции, номер устрэГютва управления, пославшего запрос на выполнение команды. Если в группе устройств обра ботки, определенной блоком классификации команд 9, имеется несколько свободных устройств обработки, то подключение выходов блока классификации команд 9 к одному из них определяется правилом, рсализуемым в олоке анализа занятости устройств обработки. Выбранное устройство обработки 1 - 1, посылает на управляющие входы коммутатора 12 номер команды, номер обративщего ся устройства управления 6 - 6, и свой номер, С выхода коммутатора 12 номер команды и номер выбранного устройства об работки ( - 1(7) поступают в обративщееся устройство управления 6, - 6,, которое выдает в соответствующий блок 7, - 7т хранения слова состо5шия программы сигнал о передаче сформированных адресов операндов в соответствующее сверхоперативное запоминающее устройство 5 - 5, для считывания затребованных операндов. Операнды вместе с номером устройства обработки 1, - 1)-р поступают на коммутатор 12, который подключает свои информационные выходы к выбранному устройству обработк, 1( -Ijyj, последнее выполняет требуем то операцию и выдает резу.льтат через коммутатор 12 Б соответствующее сверхоператив ное запоминающее устройство 5.. - 5f, Если требуемое устройство обработки 12i .«. или 1|.у занято, то блок 2 занятости устройств обработки передает в блок 10 памяти невыполненных команд KOJ операции, номер команды и номер обративщегося устройства управления 6, 6л,... ил выхода блока классификации команды 9, из которог-о засылаемая информация пос тупает в соо1ветствуюшее устройство обработки 1,, 1, ... или Ifj после выполнения им предыдущей команды. Если требуемое устройство обработки 1, lo, занято и блок 10 памяти ноьыполненных команд заполнен, то блок 11 анализа nnN-iHTn невыполненных команд выдает через блок 8 выбора приоритетных устройств угфавления сигнал, который запрещает работу соответствующего устройства управления 6,, бо, ... или 6.,, до освобождения либо требуемого устройства обработки Ij, 1.,,,.. или Ij,-, либо места в блоке памяти невыполненных команд. и 3 о о р е т е 1 и я Вычис.пительная система, содержащая устройства обработк, первые управляющие выходы которьЕх соединены с соответствующими первыми входами блока анализа занятости устройств обработки, оперативное запоминающее устройство, входы и выходы которого через первый коммутатор соединены с первыми выходам и входами сверхот еративнь1Х запокшнающпх -стройств, втог}ые входы и выходы которь х соединены с по1}вьг--;и выходал;и и входах:) cooTBeTCTB Toщ 1х устройств управления, сосд 1ненных вторь И вхэда:иИ п ЕЬ1хода и с пepвымJ; выходами 1 входа ,к соответств%1ощих блоков хранения слова состояния программы, о т л и ч а ю щ а я с я тем. что, с целью повь ще}1ия ;роизвод ;тольности, она содержит блок выбора приоритетнь х устройств управления, nepBbfe входы ; выходы оторого соеД1 };е1;ы с третыг-.Л1 выходахи и входам соответствующих ycTpoiicTB управления, с; вторые входь подключепь к перво у выходу блока заиятост устройств обработки, блок классисрикпции команд, первы.е вхоаъ1 которого подкллч5чены к вторых выходам блока выбора приор11тетнь х устройств управления, первьте соедизтены с первь.ми входам ycTpoiicTE- эбр;1ботки, л вторые входы ВЫХОДЬ , с вторь ли1 выхода П1 и входами .:i ,-;пал за 3-анятост ; устройств обработки, блок г. свь;пол ен Гь х команд, первые выходы которого соединены с 1;ервь л,1 пход;;мн устройств эбработки, п 1ервь;е входы ; ЭД СЛ очены I-L первь м выходах: блока лассификац П команд, 6:ioK г..;гализа пах-ЯТ ; евь полненг Ь х команд, первь;е входь -. выходь которого соеди-нены с BTopb X u ;1Ь ходдх-;1 и входах- блока памяти невыполкеннь хкох анд, вторые входы и выходы соедине1 ы с третьими выходами и входах и блока класс ;ф1:кац -{и оханд, трети ; вход под -:л очен к третьему выходу блока а1-;ал1 за занятости устройств D6f:a6oT v, а трст выход соедине ; с тгеть1:1ч входох: блока выбора прл ,-;тет1 эго устройств; у11рпвлеи я, то- 7

рой коммутатор, первые информационные и управляющие входы и выходы которого соединены с вторыми и третьими выходами и входами устройств обработки соответственно, а вторые информационные и управляющие входы и выходы соединены с третьими выходами и входами сверхоперативных запоми8

нающих устройств и четБертыми выходами и входами устройств управления соответственно, и третий коммутатор, включенный между вторыми входами и выходами блоков хранения слова состо5шия программы и четвертыми выходами и входами сверхоперативных запоминающих устройств.

| название | год | авторы | номер документа |

|---|---|---|---|

| Вычислительная система | 1977 |

|

SU692400A1 |

| Управляющая векторная вычислительная система | 1982 |

|

SU1120340A1 |

| Устройство для обработки выражений языков программирования | 1974 |

|

SU519715A1 |

| ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО | 1990 |

|

RU2030785C1 |

| Процессор | 1977 |

|

SU691858A1 |

| Устройство для управления в многопроцессорной вычислительной системе | 1974 |

|

SU525092A1 |

| Устройство для контроля микропроцессорных блоков | 1988 |

|

SU1531099A1 |

| УСТРОЙСТВО КОНТРОЛЯ ПРОЧНОСТИ КРЫЛА ВОЗДУШНОГО СУДНА | 2011 |

|

RU2469289C1 |

| Процессор мультиобработки данных | 1975 |

|

SU590745A1 |

| Устройство сопряжения процессора с памятью | 1986 |

|

SU1322296A1 |

Авторы

Даты

1976-09-30—Публикация

1972-06-13—Подача