Изобретение относится к вычислительной технике и может использоваться при построении высокопроизводительных вычислительных систем для решения задач, алгоритмы которых имеют последовательно - параллельную структуру.

Известно вычислительное устройство [1], содержащее общее запоминающее устройство, блоки обработки информации. Производительность такого устройства существенно снижается, когда параллельные ветви алгоритмов представляют собой последовательность небольшого числа операций, после выполнения которых необходимо осуществить обмен данными между блоками обработки информации, что характерно, например, для алгоритмов вычисления полиномов, цепных дробей и других многоместных выражений.

В качестве прототипа выбрано вычислительное устройство [2], содержащее блоки ввода и вывода данных, блоки обработки информации, блоки буферной памяти данных и команд, запоминающие устройства управляющих слов и операндов, регистры адреса и данных. Недостатком указанного устройства является то, что выход из строя блока обработки информации приводит к неправильному результату вычислений, так как в устройстве не предусмотрены средства для выполнения повторных вычислений в случае неправильного выполнения команды.

Целью изобретения является повышение надежности за счет повторения вычислений в случае неправильного выполнения команды. Это достигается тем, что в вычислительное устройство, содержащее n блоков обработки информации, блок ввода данных, блок вывода данных, блок буферной памяти данных, блок буферной памяти команд, регистр данных, регистр адреса, блок памяти операндов, блок памяти управляющих слов, коммутатор, блок микропрограммного управления, причем информационный вход устройства соединен с информационным входом блока ввода данных, выход которого соединен с первым информационным входом коммутатора, выход которого соединен с информационным входом блока буферной памяти данных, первый информационный выход которого соединен с информационным входом регистра данных, второй информационный выход блока буферной памяти данных соединен с информационным входом регистра адреса, выход которого соединен с первым информационным входом блока памяти управляющих слов, первым информационным входом блока памяти операндов, первым информационным входом блока буферной памяти команд, первый выход регистра данных соединен с вторыми информационными входами блока памяти управляющих слов, блока памяти операндов и блока буферной памяти команд, третий информационный вход которого соединен с первым выходом блока памяти операндов, информационный выход блока памяти управляющих слов соединен с четвертым информационным входом блока буферной памяти команд, первый и второй выходы которого соединены с информационным входом блока вывода данных и с информационными входами блоков обработки информации с первого по n-й, информационные выходы которых соединены соответственно с информационными входами с второго по (n+1)-й коммутатора, первый выход блока микропрограммного управления соединен с управляющим входом блока ввода данных, выход признака данных которого соединен с первым входом режима блока микропрограммного управления, второй выход которого соединен с управляющим входом коммутатора, i-й выход первой группы блока микропрограммного управления (где i=1,...,n) соединен с первым входом кода операции i-го блока обработки информации, выход признака завершения операции которого соединен с i-м входом режима группы блока микропрограммного управления. i-й выход второй группы которого соединен с вторым входом кода операции i-го блока обработки информации, выход признака занятости блока буферной памяти данных соединен с вторым входом режима блока микропрограммного управления, третий выход которого соединен с управляющим входом блока буферной памяти, четвертый и пятый выходы блока микропрограммного управления соединены соответственно с входами записи/считывания регистра адреса и регистра данных, второй выход последнего из которых соединен с третьим входом режима блока микропрограммного управления, шестой и седьмой выходы которого соединены соответственно с входами записи/считывания блока памяти управляющих слов и блока памяти операндов, второй выход последнего из которых соединен с четвертым входом режима блока микропрограммного управления, восьмой выход которого соединен с управляющим входом блока буферной памяти команд, третий выход которого соединен с пятым входом режима блока микропрограммного управления, девятый выход которого соединен с управляющим входом блока вывода, выход признака готовности и информационный выход которого соединены соответственно с шестым входом режима блока микропрограммного управления и информационным выходом устройства, введены блок памяти операнда, шифратор, группа из n элементов ИЛИ, первый и второй элементы ИЛИ, причем i-й выход первой группы блока микропрограммного управления соединен с i-м входом первого элемента ИЛИ и первым входом i-го элемента ИЛИ группы, i-й выход второй группы блока микропрограммного управления соединен с i-м входом второго элемента ИЛИ и со вторым входом i-го элемента ИЛИ группы, выходы элементов ИЛИ группы соединены с входами шифратора, выход которого соединен с адресным входом блока памяти операнда, выход которого соединен с (n+2)-м информационным входом коммутатора, третий и четвертый выходы блока буферной памяти команд соединены соответственно с первым и вторым информационными входами блока памяти операнда, входы считывания и записи которого соединены соответственно с выходами первого и второго элементов ИЛИ, пятый выход блока буферной памяти команд соединен с седьмым входом режима блока микропрограммного управления, десятый выход которого подключен к входу режима блока памяти операндов, шестой выход блока буферной памяти команд объединен с вторым выходом блока буферной памяти команд по схеме монтажное ИЛИ и соединен с информационными входами блоков обработки информации с первого по n-й и блоком вывода данных.

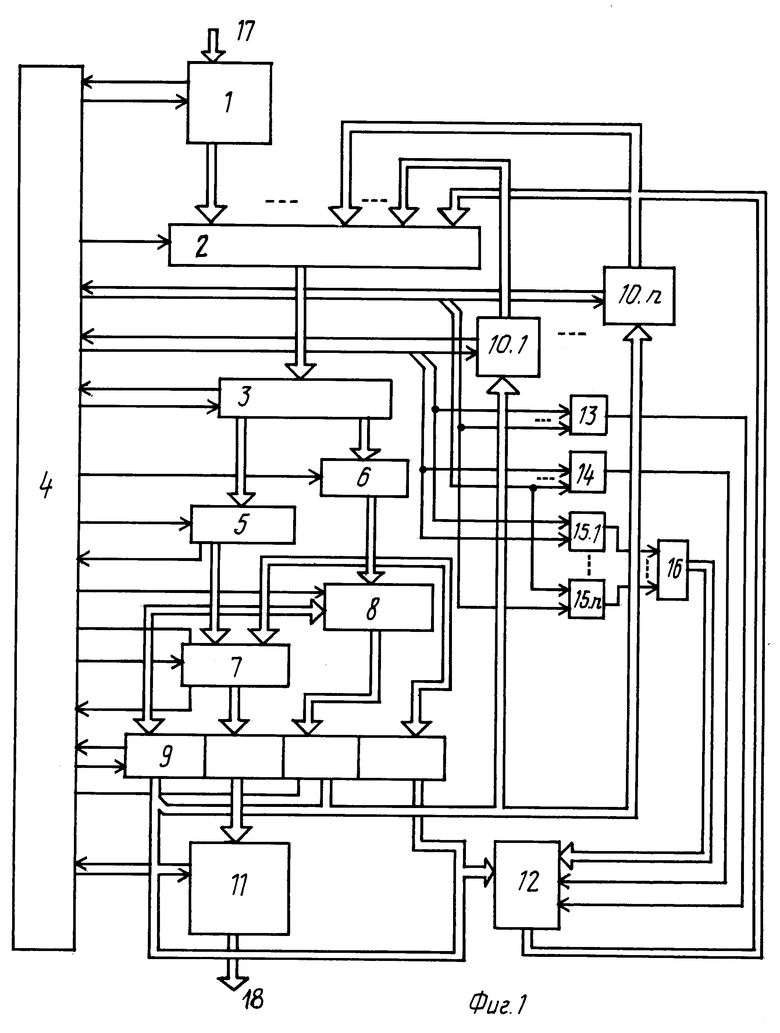

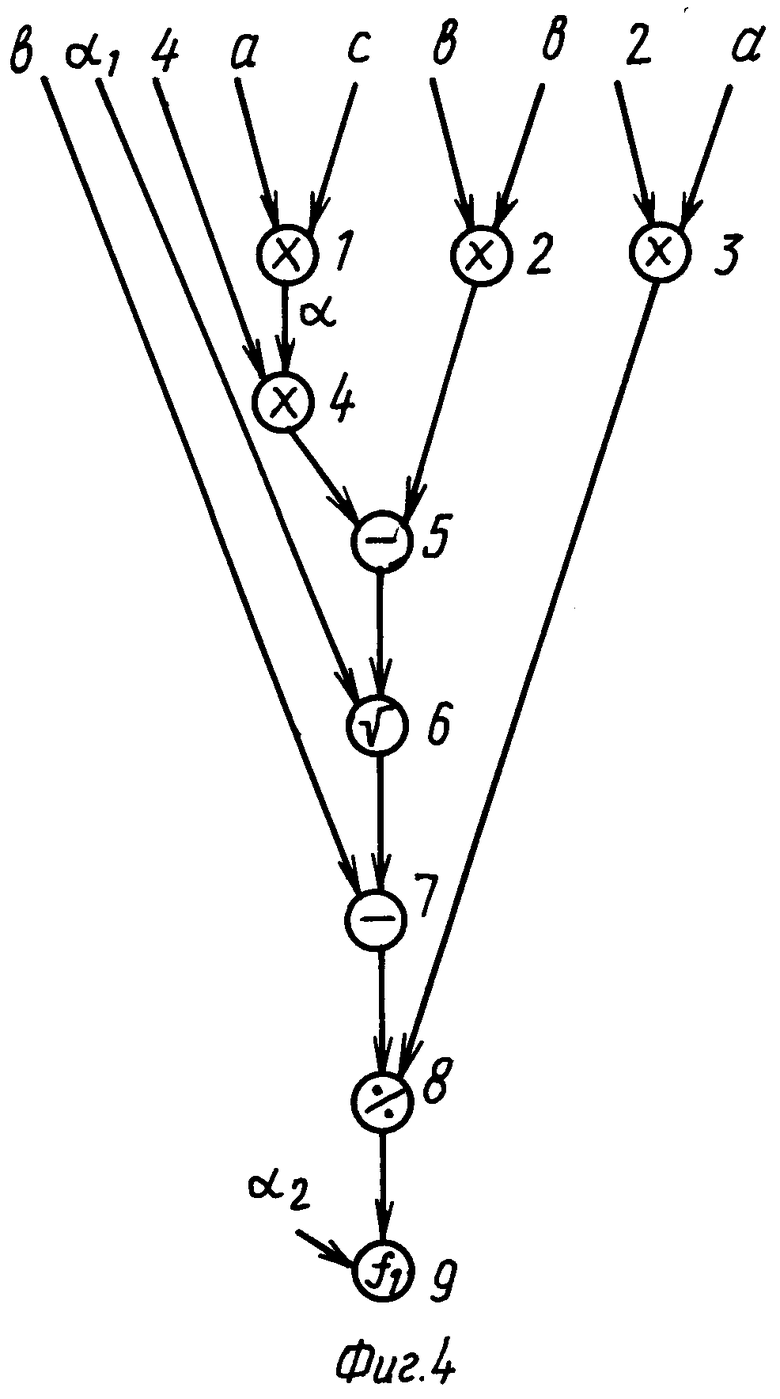

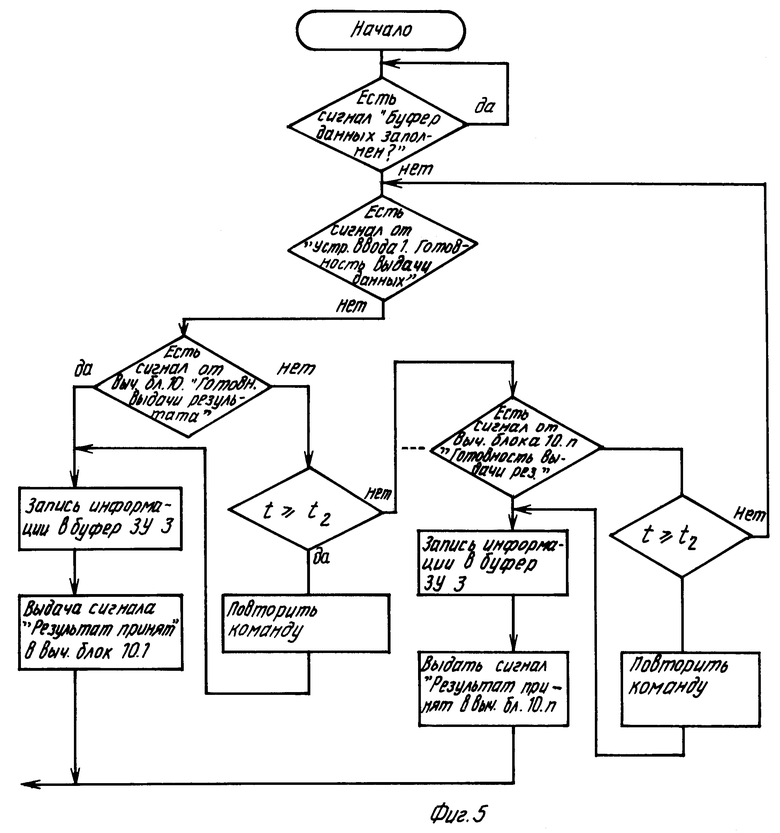

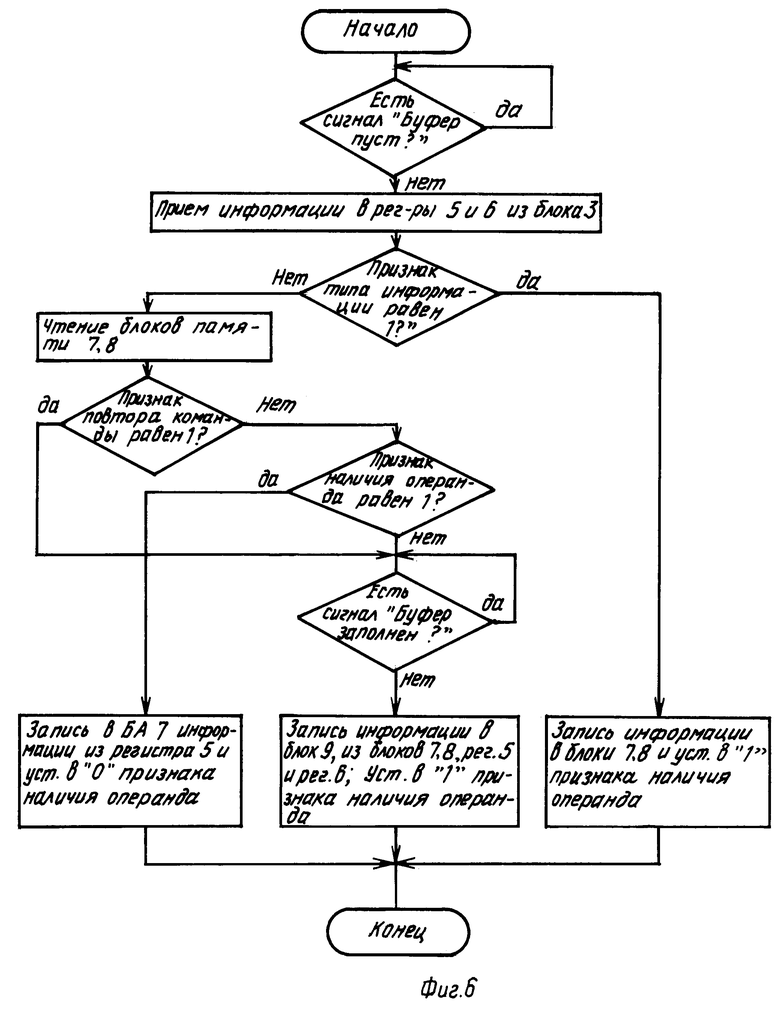

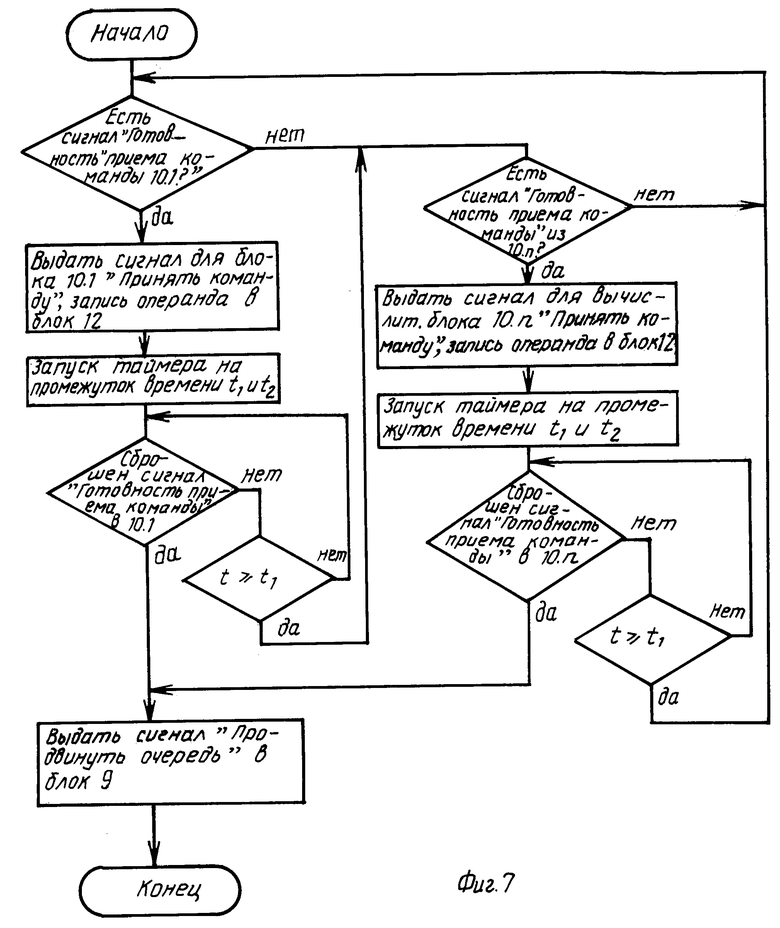

На фиг. 1 представлена структурная схема вычислительного устройства; на фиг. 2 - формат управляющего слова; на фиг. 3 - формат слова данных; на фиг. 4 - граф алгоритма вычисления функции f1; на фиг. 5 - алгоритм загрузки в блок буферной памяти данных управляющих слов, слов данных, результата выполнения команды, а также второго операнда и номера операции при повторном выполнении команды; на фиг. 6 - алгоритм формирования команды; на фиг. 7 - алгоритм распределения команд между блоками обработки информации.

Вычислительное устройство содержит блок 1 ввода данных, информационный выход которого подключен к первому информационному входу коммутатора 2, выход которого связан с информационным входом блока 3 буферной памяти данных. Управляющий вход и выход признака данных блока 1 ввода данных соединены с соответствующими входом и выходом блока 4 микропрограммного управления, выход которого подключен к управляющему входу коммутатора 2. Управляющие входы блока 3 буферной памяти данных, которые обеспечивают занесение информации и продвижение очереди, подключены к выходам блока 4 микропрограммного управления, соответствующие входы которого соединены с выходами сигналов блока 3 буферной памяти данных, характеризующих степень его заполнения ("Буфер занят" и "Буфер пуст"). К информационным входам регистра данных 5 и регистра адреса 6 подключены соответственно первый и второй информационный выходы блока 3 буферной памяти данных. Входы записи/считывания регистров 5 данных и 6 адреса подключены к выходам блока 4 микропрограммного управления, а выход одного разряда регистра данных 5 (признак типа информации) подключен к соответствующему входу блока 4 микропрограммного управления. Информационный выход регистра адреса 6 связан с адресными входами блока 7 памяти операндов и блока 8 памяти управляющих слов. Информационный выход регистра данных 5 подключен к информационным входам блока 7 памяти операндов, блока 8 памяти управляющих слов и первому информационному входу блока 9 буферной памяти команд. В блоке 9 буферной памяти команд формируется команда, которая условно разбита на четыре информационных слова (первый операнд, второй операнд, управляющее слово, адрес команды). В этом случае с входа регистра 5 на вход блока 9 поступает первый операнд. Второй, третий и четвертый информационные входы блока 9 буферной памяти команд соединены соответственно с информационными выходами блока 7 памяти операндов (второй операнд), блока 8 памяти управляющих слов (управляющее слово), регистра адреса 6 (адрес команды).

К входам записи/считывания блока 7 памяти операндов и блока 8 управляющих слов подключены соответствующие выходы блока 4 микропрограммного управления. Один выход блока 4 связан с входом режима блока 7 памяти операндов, который представляет собой вход одного информационного разряда (признак наличия операнда), а выходы двух разрядов блока 7 операндов (разряды признака наличия операнда и признака повторения команды) соединены с двумя входами блока 4. Выходы, указывающие на степень заполнения, а также управляющие входы записи и продвижения очереди блока 9 подключены к соответствующим входам и выходам блока 4.

Информационные выходы (первый, второй и третий) блока 9 буферной памяти команд подключены к информационным входам блоков обработки информации 10.1, ...,10.n и информационному входу блока 11 вывода данных, управляющий вход и выход признака готовности которого связаны с соответствующими выходом и входом блока 4.

Первый и четвертый информационные выходы блока 9 буферной памяти команд соединены с информационными входами блока 12, выход которого подключен к (n+2)-му информационному входу коммутатора 2. Группы управляющих входов и выходов блока 4 микропрограммного управления подключены к соответствующим выходам входам блоков обработки информации 10.1,...,10.n, информационные выходы которых соединены с информационными входами коммутатора 2. К управляющим входам чтения и записи блока 12 подключены выходы элементов ИЛИ 13 и 14. Входы элемента ИЛИ 13 соединены с одним из управляющих входов каждого блока обработки информации 10.1, . ..,10.n, по которому подается сигнал "Прием кода" от блока 4. Кроме того, эти же входы блоков обработки информации 10.1,...,10.n соединены с первыми входами элементов ИЛИ группы 15.1,. . . , 15. n соответственно. К входам элемента ИЛИ 14 подключены управляющие входы блоков обработки информации 10.1,...,10.n, по которым от блока 4 передается сигнал "Повтор команды". Эти же входы блоков обработки информации 10.1,...,10.n соединены с вторыми входами элементов ИЛИ группы 15.1,...,15. n соответственно. Выходы группы элементов ИЛИ 15.1,...,15.n подключены через шифратор 16 к адресным входам блока 12. Информационный вход блока 1 ввода данных связан с информационным входом устройства 17, информационный выход 18 которого соединен с информационным выходом блока 11 вывода данных.

В качестве блока 3 буферной памяти данных и блока 9 буферной памяти команд можно использовать любое запоминающее устройство, работающее по принципу "первым пришел - первым вышел" (FIFO). Каждый из блоков 10.1,...,10.n обработки информации содержит таймер, который формирует два сигнала, один из которых соответствует интервалу времени t1, а второй - большему интервалу времени t2. Таймер запускается блоком 4 микропрограммного управления и сбрасывается самим блоком 10.j.

Вычислительное устройство работает следующим образом.

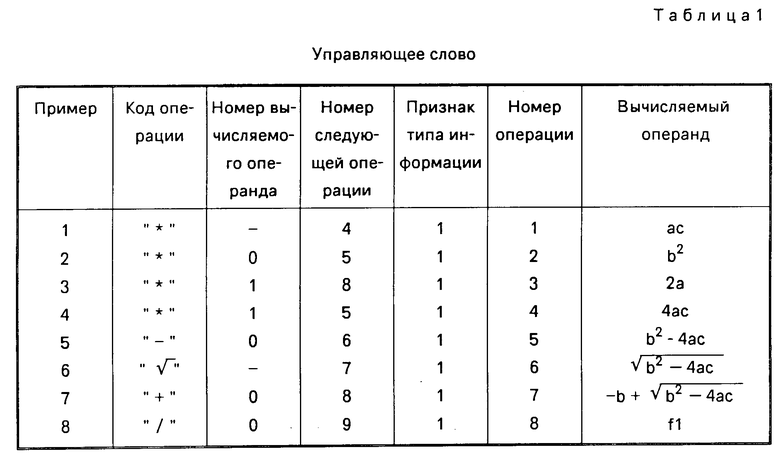

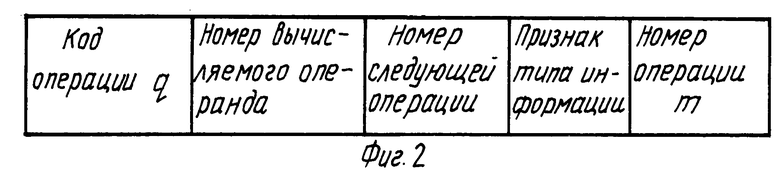

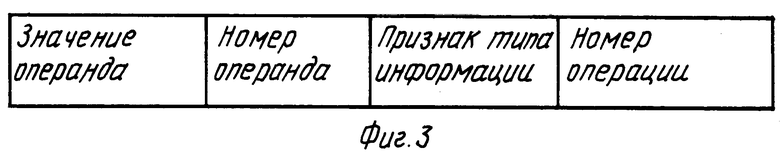

Исходная для вычислений информация вводится с информационного входа устройства 17 через блок 1 ввода данных и представляет собой последовательность управляющих слов и слов данных. Управляющее слово, формат которого представлен на фиг. 2, содержит q-разрядное поле кода операции, разряд номера вычисляемого операнда, s-разрядное поле номера следующей операции, разряд признака типа информации и поле номера операции, имеющее m разрядов. Разряд признака типа информации для всех управляющих слов имеет значение "1". Информация, записываемая в остальные поля управляющего слова, определяется заданным графом алгоритма вычислений, который строится независимо от числа n блоков обработки информации. В качестве примера (фиг. 4) представлен граф алгоритма вычислений выражения

f1 = (-b + /2a

/2a

Каждой вершине графа, которая соответствует определенной операции, присваивается номер, отличный от номеров других вершин. Управляющие слова для каждой вершины графа представлены в табл. 1. Вершина с номером 1 соответствует действию α= а ˙с. В поле кода операции управляющего слова для данной вершины записывается код операции умножения, в поле номера операции - "1" (номер вершины), в поле следующей операции - "4" (номер вершины, для которой результат операции является операндом) или можно записать приращение "3" (разность номеров вершин, с помощью которой получают номер следующей операции, просуммировав номер текущей операции с разностью). Разряд номера вычисляемого операнда имеет смысл для операций, которые не обладают свойством коммутативности (деление, вычитание и др.). В этом случае делимое и делитель, уменьшаемое и вычитаемое имеют разные номера (0 или 1). Для операции, соответствующей первой вершине, в разряде номера вычисляемого операнда, отмеченном прочерком, можно записать любую цифру, так как следующая (четвертая) операция умножения обладает свойством коммутативности. Каждой дуге графа соответствует слово данных (фиг. 3), включающее n - разрядное поле значения операнда в принятой для данной операции форме (с фиксированной или плавающей запятой и т.д.), m - разрядное поле номера операции (номера вершины на графе, для которой дуга является входной), разряд номера операнда и разряд типа информации, который для слов данных (в отличие от управляющих слов) всегда имеет нулевое значение. Слова данных для дуг графа (фиг. 4) представлены в табл. 2.

Для определенности предполагается, что для вычисления f1 используются операции умножения ("*"), сложения ("+"), вычитания ("-"), деления ("/") и извлечения корня (" "). Операнд α1 для операции извлечения корня необходим лишь для инициализации выполнения данной операции (см. ниже). В разряде номера этого операнда записывается "1", а в операнде, из которого извлекается корень, - "0". Вершине с номером 9 на графе соответствует операция передачи результата в блок 11 вывода данных. Слово данных, в котором записано значение результата, имеет нулевой признак операнда. Для инициализации или начала передачи результата в блок 11 вывода данных служит операнд α2, признак номера которого имеет значение "1". Граф для каждого алгоритма строится независимо от других. Номера вершин ни в одном графе не должны повторяться.

"). Операнд α1 для операции извлечения корня необходим лишь для инициализации выполнения данной операции (см. ниже). В разряде номера этого операнда записывается "1", а в операнде, из которого извлекается корень, - "0". Вершине с номером 9 на графе соответствует операция передачи результата в блок 11 вывода данных. Слово данных, в котором записано значение результата, имеет нулевой признак операнда. Для инициализации или начала передачи результата в блок 11 вывода данных служит операнд α2, признак номера которого имеет значение "1". Граф для каждого алгоритма строится независимо от других. Номера вершин ни в одном графе не должны повторяться.

Длина q поля кода операции (фиг. 2) определяется количеством команд и должна включать не менее log2N разрядов. Разрядность m должна обеспечивать возможность записи самого большого номера операции (вершины на графе), а разрядность S - либо максимального номера, либо максимальной по модулю разности номеров операций. Разрядность n поля значения операнда (фиг. 3) зависит от формы и точности представления операндов. Это поле может включать знаковые разряды, мантиссу и порядок.

В исходном состоянии блоки 7 буферной памяти данных и 9 буферной памяти команд пусты (в них вырабатываются сигналы "буфер пуст"). Цепи установки исходного состояния условно не показаны. При функционировании устройства можно выделить следующие процессы:

ввод в блок 3 буферной памяти данных информации из блока 1 ввода данных, из блоков обработки информации 10.1,...,10.n (в случае исправной работы блоков 10.1,...,10.n) и из блока 12 памяти операнда (в случае повторного выполнения команды);

формирование команды и засылка ее в блок 9 буферной памяти команд;

распределение команд между блоками 10.1,...,10.n обработки информации (для дальнейшей обработки) и блоком 11 вывода данных.

Рассмотрим работу устройства в случае, когда отказы блоков обработки информации отсутствуют. Первый из указанных процессов иллюстрируется алгоритмом (фиг. 5). Блок 4 анализирует сигнал "Буфер данных заполнен" блока 3 буферной памяти данных. При отсутствии указанного сигнала, когда в блок 3 буферной памяти данных можно записать информацию, блок 4 проверяет сигнал на выходе признака данных блока 1 ввода данных и сигналы на выходах признака завершения операции блоков обработки информации 10.1,...,10.n. Наличие первого из указанных сигналов свидетельствует о том, что блок 1 ввода данных принял данные с информационного входа 17 устройства. В этом случае по сигналам из блока 4 микропрограммного управления информация из блока 1 через коммутатор 2 записывается в блок 3. Аналогичным образом производится запись в блок 3 из блока 10.j в случае его готовности. В последнем случае в блок 10. j обработки информации передается сигнал "Результат принят" из блока 4 микропрограммного управления и блок 10.j снимает сигнал признака завершения операции. Если блок 3 не готов к записи (заполнен), то выполняется ожидание момента, когда запись будет возможна (снимается сигнал "Буфер данных заполнен").

Если блок 10.j обработки информации не выставляет сигнала признака завершения операции, то блок 4 микропрограммного управления проверяет условие t>t2, где t2 - промежуток времени, за который результат может быть получен обязательно, если блок 10.j не вышел из строя. Когда блок 10.j обработки информации работает правильно, условие t>t2 не выполняется и проверяется сигнал признака завершения операции в следующем блоке 10.j+1.

В процессе ввода исходной информации из блока 1 ввода данных сначала вводится управляющее слово, а затем слово данных для соответствующей операции. Процесс формования команды осуществляется следующим образом. Управляющее слово записывается в блок 8 управляющих слов по адресу, совпадающему с номером операции. Первое из поступающих слов данных для этой операции записывается по этому же адресу в блок 7 памяти операндов. Затем управляющее слово и один из операндов ожидают поступления из блока 3 данных недостающего операнда, после чего выполняется компоновка команды. Команда содержит управляющее слово, оба операнда, номер операции и записывается в блок 9 (в очередь для выполнения), причем номер операции записывается из регистра 6.

Алгоритм формирования команды приведен на фиг. 6. Блок 4 микропрограммного управления анализирует сигнал "Буфер пуст" блока 3 буферной памяти данных. При отсутствии указанного сигнала (в блоке 3 имеется хотя бы одно слово) слово с его выхода записывается в регистры адреса 6 и данных 5, причем в регистр 5 записывается поле номера операции (см. фиг. 2 и 3). Блок 4 проверяет в регистре данных 5 признак типа информации, который имеет единичное значение для управляющего слова и нулевое - для слова данных. Если признак типа информации равен "1", то в блок 8 записывается управляющее слово. Одновременно с этим в блок 7 записывается "1" в разряд признака наличия операнда (это означает, что для данного управляющего слова в блоке 7 нет ни одного операнда). В процессе записи адресом для блоков памяти операндов 7 и управляющих слов 8 является содержимое регистра 6. В блок 8 данные записываются из регистра 5, в блок 7 единичное значение на вход разряда признака наличия операнда подается из блока 4 микропрограммного управления.

В случае, если в регистре 5 признак типа информации равен "0" (слово является данными), осуществляется проверка признака повтора команды и признака наличия операнда в блоке 7 памяти операндов. Для этого осуществляются чтение блоков 7 и 8 и анализ указанных признаков. Если признак повтора команды равен "0" (команда формируется впервые), необходимо проанализировать и признак наличия операнда. При равенстве этого признака "1" (в блоке 7 памяти операндов нет операнда для данного управляющего слова) осуществляется запись в блок 7 слова из регистра 5. Одновременно с этим в признак наличия операнда записывается "0" (имеется один операнд для данной операции). При равенстве признака наличия операнда "0" и отсутствии сигнала "Буфер заполнен" готовая к выполнению команда (управляющее слово из блока 8 памяти управляющих слов, один операнд из блока 7, другой операнд из регистра данных 5 и номер операции из регистра 6) записывается в блок 9 буферной памяти команд. Разряд признака наличия операнда в блоке 7 устанавливается в "1".

Если в блоке 9 имеется хотя бы одна команда (нет сигнала "Буфер пуст"), то блок 4 анализирует поле типа команды на выходах блока 9 и обеспечивает передачу команды в блок 11 или в один из блоков обработки информации 10.j. Если команда имеет вычислительный характер (сложение, умножение и т.д.), передача ее в блок 10.j осуществляется в соответствии с алгоритмом, представленным на фиг. 7. Готовый к приему команды блок 10.j обработки информации выдает в блок 4 сигнал "Готовность приема команды". Блок 4 поочередно анализирует готовность каждого блока обработки информации 10.1,...,10.n, способного выполнить данную команду. Блок 4 передает готовому блоку 10.j управляющий сигнал "Принять команду". Команда из блока 9 буферной памяти команд передается в блок 10.j обработки информации. Одновременно с этим в блок 12 из блока 9 записываются второй операнд и номер операции. Адрес, по которому осуществляется запись, формируется с помощью шифратора 16 и совпадает с номером j блока 10.j обработки информации (на шифратор 16 поступает через один из элементов ИЛИ 15 сигнал "Принять команду", предназначенный для j-го блока обработки информации). Кроме того, сигнал "Принять команду" через элемент ИЛИ 13 поступает на вход записи блока 12 памяти операнда, что обеспечивает фиксацию информации в этом блоке. Далее блок 4 запускает таймер блока 10. j обработки информации на промежутки времени t1 и t2, а сам блок 10.j сбрасывает сигнал "Готовность приема команды" и начинает выполнение своей команды. После снятия сигнала "Готовность приема команды" блок 4 микропрограммного управления вырабатывает сигнал "Продвинуть очередь" для блока 9 буферной памяти команд. Описанный процесс формирования команды повторяется циклически.

В процессе обработки команды каждый блок 10.j обработки информации обменивается с блоком 4 микропрограммного управления двумя входными и двумя выходными управляющими сигналами. Одна пара сигналов (входной и выходной) используются для ввода команды, а другая - для выдачи результата после выполнения команды. Операнды, которые используются для инициализации выполнения операций и не имеют смыслового значения (например, α1 на графе на фиг. 4), в блоках 10.1,...,10.n необрабатываются.

При работе вычислительного устройства могут возникнуть сбои в работе одного или нескольких блоков обработки информации. Сбои могут возникнуть до того, как выставлен сигнал "Готовность приема команды " или после того, как он сброшен. В обоих случаях необходимо повторить команду, которая должна была выполняться или выполнялась в неисправном блоке обработки информации. Рассмотрим случай, когда блок 10. j обработки информации не сбрасывает сигнал "Готовность приема команды", т.е. он вышел из строя до начала выполнения команды. Как видно из алгоритма на фиг. 7, блок 4 микропрограммного управления анализирует, сброшен ли сигнал "Готовность приема команды" на промежутке времени t>t1. Время t1 выбирается таким образом, что за данный промежуток времени блок обработки информации при правильном функционировании обязательно примет команду и снимет сигнал "Готовность приема команды". Если по истечении времени t1 этого не произошло, то блок 4 микропрограммного управления повторяет процедуру передачи команды следующему (j+1)-му блоку обработки информации. Таким образом, если имеется хотя бы один работоспособный блок, то команда будет передана ему.

Рассмотрим второй случай, когда блок 10.j выходит из строя после приема команды, т.е. после снятия сигнала "Готовность приема команды". В этом случае также используется таймер, который запускается блоком 4 микропрограммного управления (фиг. 7). Промежуток времени t2 выбирается таким образом, чтобы правильно функционирующий блок успел выполнить любую команду. При считывании результата операции (фиг. 6) блок 4 микропрограммного управления поочередно проверяет сигнал "Готовность выдачи результата" в каждом блоке 10. j и при его отсутствии проверяет, не закончилось ли выделенное для операции время t2. Если сигнал "Готовность выдачи результата" формируется на протяжении отрезка времени t2, то результат считается правильным и записывается в блок 3 буферной памяти данных. Если по истечении времени t2 блок 10. j не выставил сигнал "Готовность выдачи результата", то осуществляется повторная запись в блок 3 буферной памяти данных второго операнда с номером операции данной команды из блока 12 памяти операнда, т.е. невыполненная команда будет повторно сформирована и передана в исправный блок обработки информации. Повторная запись второго операнда осуществляется с помощью сигнала "Повторить команду" для блока 10.j, который через элемент ИЛИ 14 поступает на вход считывания блока 12 и, кроме того, устанавливает нужный адрес, равный номеру j, поступая через элемент ИЛИ 15.j на соответствующий вход шифратора 16. При занесении второго операнда в блок 3 буферной памяти данных разряд признака типа информации устанавливается в нулевое состояние, а разряд признака повтора команды - в единичное аппаратным способом (к соответствующим входам подведены сигналы соответствующих уровней). Так как управляющее слово и первый операнд хранятся в блоках 8 и 7, то в соответствии с алгоритмом (фиг. 6) после проверки признака повтора команды независимо от признака наличия операнда невыполненная команда будет сформирована и записана в блок 9.

Таким образом, устройство остается работоспособным при отказах блоков обработки информации.

| название | год | авторы | номер документа |

|---|---|---|---|

| Вычислительная система | 1990 |

|

SU1709331A1 |

| Устройство обработки информации с переменной длиной команд | 1990 |

|

SU1817099A1 |

| ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 1991 |

|

RU2042193C1 |

| Устройство центрального управления процессора | 1983 |

|

SU1136177A1 |

| Арифметическое устройство с микропрограммным управлением | 1988 |

|

SU1541594A1 |

| Устройство для обработки нечеткой информации | 1985 |

|

SU1564603A1 |

| Арифметическое устройство с микропрограммным управлением | 1988 |

|

SU1559340A1 |

| Арифметическое устройство с микропрограммным управлением | 1988 |

|

SU1559341A1 |

| ПРОЦЕССОР ДЛЯ КОНТРОЛЯ ЦИФРОВЫХ СХЕМ | 1972 |

|

SU435527A1 |

| Микропрограммный процессор | 1978 |

|

SU741269A1 |

Изобретение относится к вычислительной технике и может быть использовано для построения высокопроизводительных вычислительных систем. В вычислительной системе предусмотрены средства для выполнения повторных вычислений в случае неправильного выполнения команды. Вычислительная система содержит устройства ввода данных, коммутатор, вычислительные блоки, блоки памяти операндов и управляющих слов, блоки буферной памяти данных и команд, блок микропрограммного управления, регистр данных, регистр адреса, блок вывода данных, элементы ИЛИ. 7 ил., 2 табл.

ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО, содержащее n блоков обработки информации, блок ввода данных, блок вывода данных, блок буферной памяти данных, блок буферной памяти команд, регистр данных, регистр адреса, блок памяти операндов, блок памяти управляющих слов, коммутатор, блок микропрограммного управления, причем информационный вход устройства соединен с информационным входом блока ввода данных, выход которого соединен с первым информационным входом коммутатора, выход которого соединен с информационным входом блока буферной памяти данных, первый информационный выход которого соединен с информационным входом регистра данных, второй информационной выход - с информационным входом регистра адреса, выход которого соединен с первыми информационными входами блока памяти управляющих слов, блока памяти операндов и блока буферной памяти команд, первый выход регистра данных соединен с вторыми информационными входами блока памяти управляющих слов, блока памяти операндов и блока буферной памяти команд, третий информационный вход которого соединен с первым выходом блока памяти операндов, информационный выход блока памяти управляющих слов соединен с четвертым информационным входом блока буферной памяти команд, первый и второй выходы которого соединены с информационным входом блока вывода данных и с информационными входами n блоков обработки информации, информационные выходы которых соединены соответственно с информационными входами с второго по (n + 1)-й коммутаторов, первый выход блока микропрограммного управления соединен с управляющим входом блока ввода данных, выход признака данных которого соединен с первым входом режима блока микропрограммного управления, второй выход которого соединен с управляющим входом коммутатора, i-й выход первой группы блока микропрограммного управления (где i = 1, ..., n) соединен с первым входом кода операции i-го блока обработки информации, выход признака завершения операции которого соединен с i-м входом режима группы блока микропрограммного управления, i-й выход второй группы которого соединен с вторым входом кода операции i-го блока обработки информации, выход признака занятости блока буферной памяти данных соединен с вторым входом режима блока микропрограммного управления, третий выход которого соединен с управляющим входом блока буферной памяти, четвертый и пятый выходы блока микропрограммного управления соединены соответственно со входами записи-считывания регистра адреса и регистра данных, второй выход последнего соединен с третьим входом режима блока микропрограммного управления, шестой и седьмой выходы которого соединены соответственно с входами записи-считывания блока памяти управляющих слов и блока памяти операндов, второй выход которого соединен с четвертым входом режима блока микропрограммного управления, восьмой выход которого соединен с управляющим входом блока буферной памяти команд, третий выход которого соединен с пятым входом режима блока микропрограммного управления, девятый выход которого соединен с управляющим входом блока вывода, выход признака готовности и информационный выход которого соединены соответственно с шестым входом режима блока микропрограммного управления и с информационным выходом устройства, отличающееся тем, что, с целью повышения надежности за счет повторения вычислений в случае неправильного выполнения команды, в устройство введены блок памяти операнда, шифратор, группа из n элементов ИЛИ, первый и второй элементы ИЛИ, причем i-й выход первой группы блока микропрограммного управления соединен с i-м входом первого элемента ИЛИ и первым входом i-го элемента ИЛИ группы, i-й выход второй группы блока микропрограммного управления соединен с i-м входом второго элемента ИЛИ и с вторым входом i-го элемента ИЛИ группы, выходы элементов ИЛИ группы соединены с входами шифратора, выход которого соединен с адресным входом блока памяти операнда, выход которого соединен с (n + 2)-м информационным входом коммутатора, третий и четвертый выходы блока буферной памяти команд соединены соответственно с первым и вторым информационными входами блока памяти операнда, входы считывания и записи которого соединены соответственно с выходами первого и второго элементов ИЛИ, пятый выход блока буферной памяти команд соединен с седьмым входом режима блока микропрограммного управления, десятый выход которого подключен к входу режима блока памяти операндов, шестой выход блока буферной памяти команд объединен с вторым выходом блока буферной памяти команд по схеме монтажное ИЛИ и соединен с информационными входами n блоков обработки информации и блоком вывода данных.

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Вычислительная система | 1990 |

|

SU1709331A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Пуговица для прикрепления ее к материи без пришивки | 1921 |

|

SU1992A1 |

Авторы

Даты

1995-03-10—Публикация

1990-09-21—Подача