(34) ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для отображения информации | 1986 |

|

SU1506478A1 |

| Ассоциативное запоминающее устройство | 1978 |

|

SU701349A1 |

| Динамическое оперативное запоминающее устройство | 1981 |

|

SU1003142A1 |

| Устройство для сопряжения ЭВМ с абонентами | 1987 |

|

SU1411760A1 |

| Устройство для сопряжения каналов ввода-вывода с абонентом | 1983 |

|

SU1160422A1 |

| Устройство для сопряжения процессора с устройствами ввода-вывода | 1983 |

|

SU1129602A1 |

| Устройство для управления памятью | 1987 |

|

SU1483491A1 |

| Устройство для тестового контроля логических узлов | 1991 |

|

SU1837297A1 |

| Устройство для обмена информацией между ЭВМ и периферийными устройствами | 1989 |

|

SU1777145A2 |

| Устройство для задания тестов | 1983 |

|

SU1141379A2 |

Изобретенке «ушосится к области вычислительной техники.

Наиболее близким тexIraчecки t решением , является запоминающее устройство, содер,жашее элементы памйтн, подключенные через : дешифратор к соответствз ющим выходам пер:вого и второго регистров адреса, входы ко торь1х подключены к кодовым шинам, шину разрешения дешифравии и шину запуска.

Недостатком запо ганающего устройства является невысокое быстродействие, что свя:заио с задержкой Т между мокшйталто пода- ;чи на первые и вторые адреснь5е шииы полупроводниковых элементов памяти соответственно старших разрядов кода адреса к сигнала вь борки. Задержка Г характерна для полупроводниковых элементов памяти и обусловлена большим временем расшифровки адреса внутри полупроводниковых элементов ; памяти.

Целью изобретения является повышение быстродействия устройства.

Поставленная пеяь достигается тем, что tycTpoftCTBO содержит третий и четвертый ре |гистры адреса, схему сравнения, двухканал&ньгй переключатель, элемент задержки и гер, причем входы третьего и четсертог регистров адреса соединены с одноименн. входами первого регистра , а выходы через схему сравнения подключены к уп авляюшему входу двухканального переключателя, ppyrvie входы которого один Henocpej ственно, а гфугой - через элемент задержки, соединены с шиной разрешения дешифрации, выход двухканального переключателя подоое;динен к yпpaвляющё iy входу дешифратора, I управяяюнше входы третьего и четвертого регистров адреса через триггер подключены JK шине записи.

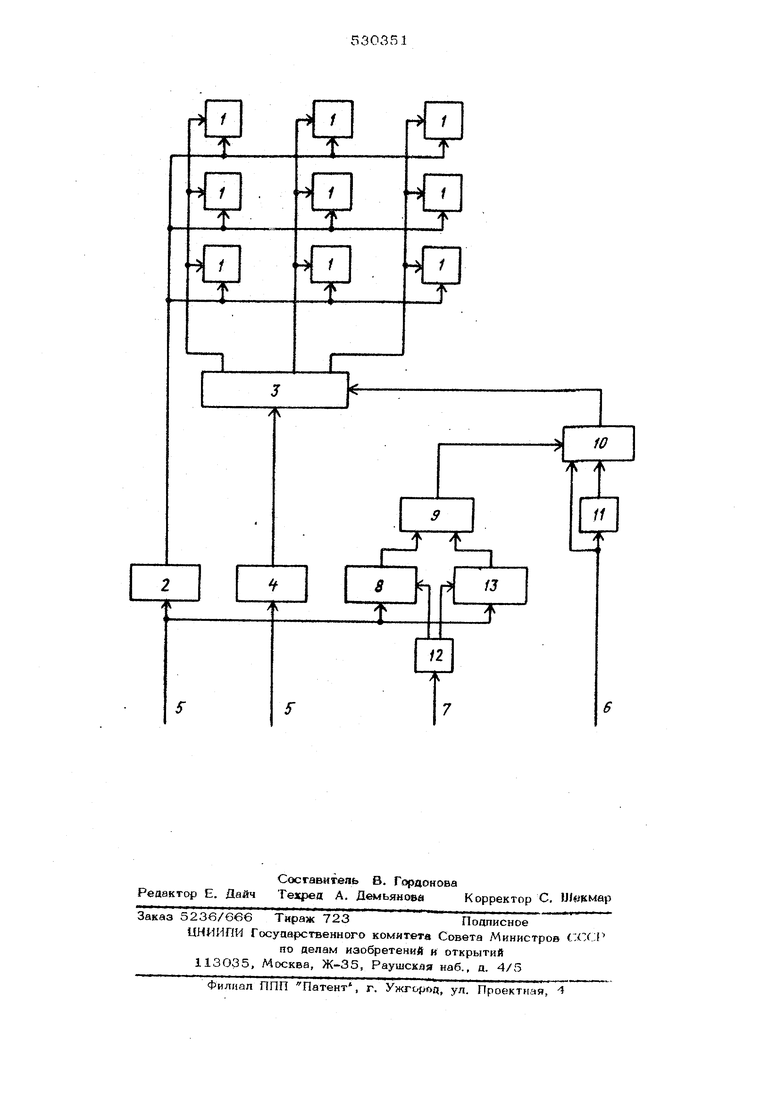

На чертеже приведена блок-схема устроЛотва.

Устройство содержит пoлyпpoвo raнкoвыe элементы 1 паьтяти, первый регистр 2 адIpeca, Дешифратор 3, второй регистр 4 , кодовые шины Б адреса, шину 6 рва1реше1шя дешифрапии, шину 7 запуска, третий регистр 8, схему 9 сравнения, двухканал гньгй .переключатель Ю, элемент 11 задержки, триггер 12, четвертый регистр 13, Устройство работает слевующим образом. По кодовым шинам 5 ащзеса поступает полный код асреса, причем & перьый ре гжлр 2 адреса заносятся старшие разряды кода адреса, а во второй регистгр 4 ащ)«;а росятся младшие разряды кода адреса. Одновременно старшие разряды кода ащ)еса поступают на одаоимешые входы регистров $ и 13, Импульс аайуска. поступающий по швне запуска 7 иа вход триггера 12, перебрасывает; его в погической состояние, противоположное TOKty, в котором тригг 12 находился до Щ)ихода импульса запуска, В аавйо«мооти от состояния триггера 12 . выбираотся один из регистров 8 или 13, в коТСфЬй в данный момент времени заносят ся старшие разряды кода адреса. При этом ООСТОяние одного из регистров 8 или 13 не иэменяется и на нем сохраняются старите разряда преды joymero кода адреса. Состояние регистров 8 и 13, т.е. старите разряды предыдущего и текушего кодов адреса, Сравнивается схемой сравнения 9. Резупьггат сравнения поступает на управляющий вход двуХканального переключателя 10, на другие два входа которого по шине в разрешения дешифранив поступает сигнал разрешения дешифрации. При этом на один из входов I двухканальяого переключателя Ю сигнал разрешения поступает непосредственно, а на вругой i- через впемент задержки i 1, fta котором он задерживается на время t . В зависимости от резуямгата сравнения сос тояния регистров 8 и 13, т.е. от несовпаде ния или совпадения старших разрядов кода адреса, через даухканальный перекшоча - тель 1О на управляющий вход деш фратора 3 поступает соответственно задержанный на элементе задержки 11 или незадержанны сигная рас ешения дешифрации. Соответстве НО иа эпемеиты памяти 1 с выходов дешифратора 3 будет поступать задержанный илт. неоадер}каннь.тй относительно кюмента псютуп ления старших разрядов кода адреса сигнал ||выборки элементов памяти 1. При весоападешге старших разрядов пре{(ыдушего и тек тцего кодов адреса на вто рыв адресные цлшы элементов памяти 1 по дается задержанный сигнал выборки, т.е., i также, как и в извес-шом устройстве. Пра совпадении же старших разрядов предыдуше- го и текущего кодов адреса на вторые адресные входы элементов памяти подаегся сигнал выборки на время Т раньше, . в известном устройстве, поскольку не трсбуе1 ся время на расшифровку адреса внут|ги згее ментоь памяти 1 (старшие раз5) кера 1адрес 1 хранятся иа первом perifeaYe «%€- са, 11, следом ателыто, адрес BSIJTPVS элемен- ов памяти 1 уже расшифрован в предыдущем, бращении), Поскольку при работе в составе ЭВМ и ряде других применений для запоминающео ус-хройства характерным является после оватепышя смена адресов, что соответствую т изменению старших разрядов кода адреса ерез 2 обращений к запоминающемуустро&тйу ( к-1зазрядность второю регистра aj реса), то в 2 обращениях старигае разряды преда.1дуадего н текущего кодов будут совпадать и, следовательно, сигнал выборки (будет поступать на вторые арресные шины no-f ;лупров9дниковых элементов памяти на вре|мя t: раньше, чем в известном устройстве. Только в одном обращении ( + 1)старЕше разряды предыдушего и текущего кодов а/феса буду- различаться и, следовательно, сигнал выборки будет поступать на вторые адресные шинЬт полупроводниковых элементов памяти незадержанным, т.е. также, как в известном усчройстве. Так как задержка С , например, для полуировоцниковьтх злементоа пам5гги МОП-типа может доститать величины, равных 2ОО-4ОО коек, при времени цикла обращения полупроводниковых элементов памяти ТОО -9ОО нсек, то изобретение позволяет сократить время цикла обращения запоминающего устройства, а также время выборки ш фop Шции примерно на ЗО-5О %, Таким образом, изобретение позволяет существенно повысить быстродействие запокоткаюшего устройства. Формула изобретения Запоминающее устройство, содержагпее элементы памяти, подключенные децп1фратор к соответствуютим выходам первого и второго регистров адреса, входы которых подключены к кодовым шинам, шину разрешения дешм|)рапии и шину запуска, о тличаюшееся тем, что, с целью повышения быстродействия устройства, оно содерла третий и четвертый регистры адреса, cxeKsy сравнения, двухканальный переключатель, элемент задержки к триггер, ггричем входы третьего и четвертого регистров адреса соединень с одноименными входами перього регистра адреса, а выходы через схему сравнешш подключены к управляющему входу двухканалыюго переключателя, {фугие входы которого опин непосредственво, а (фугой - через элемент задержки соединены с шиной разрешения дешифратга, выход двухканального переключателя подсоединен к управляк щек{у входу дешифратора, а управляющие входы третьего и четвертого регистров ajoqpeca через триггер подключены к шине записи.

Авторы

Даты

1976-09-30—Публикация

1975-02-24—Подача