Изобретение относится к вычислительной технике и может быть использовано в системах на основе микро- ВМ с общей тиной для управления оперативными и постоянными запоминающими устройствами.

Цель изобретения - повышение достоверности функционирования.

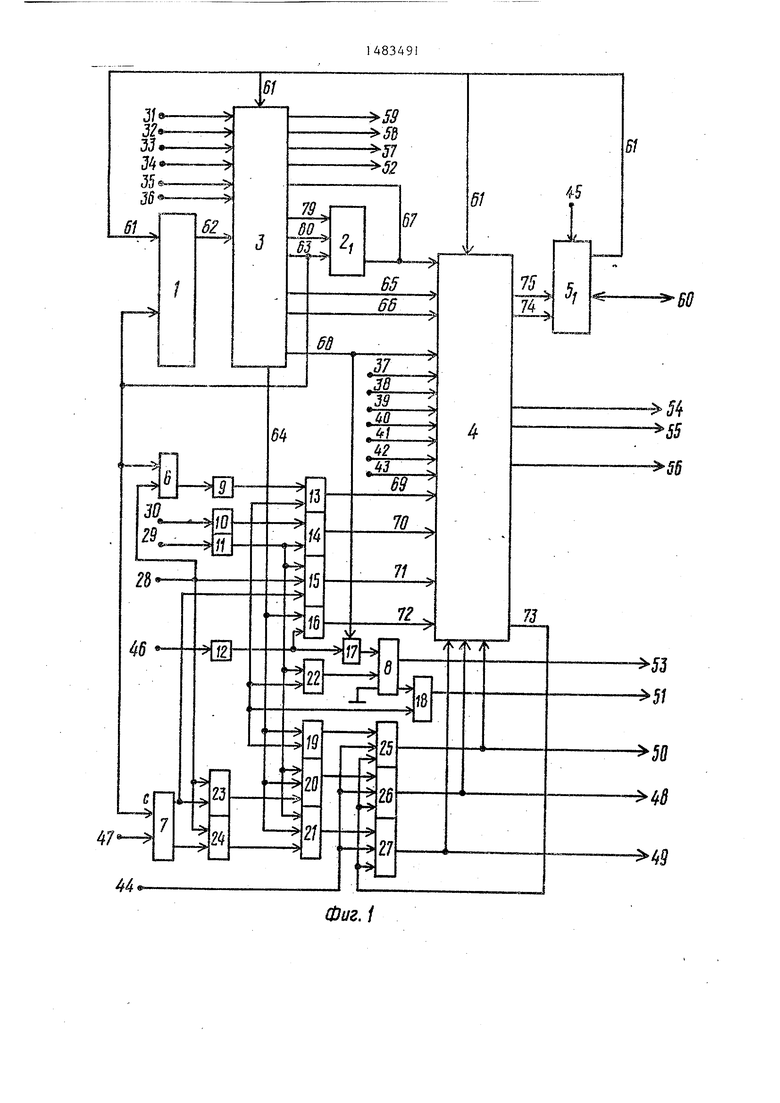

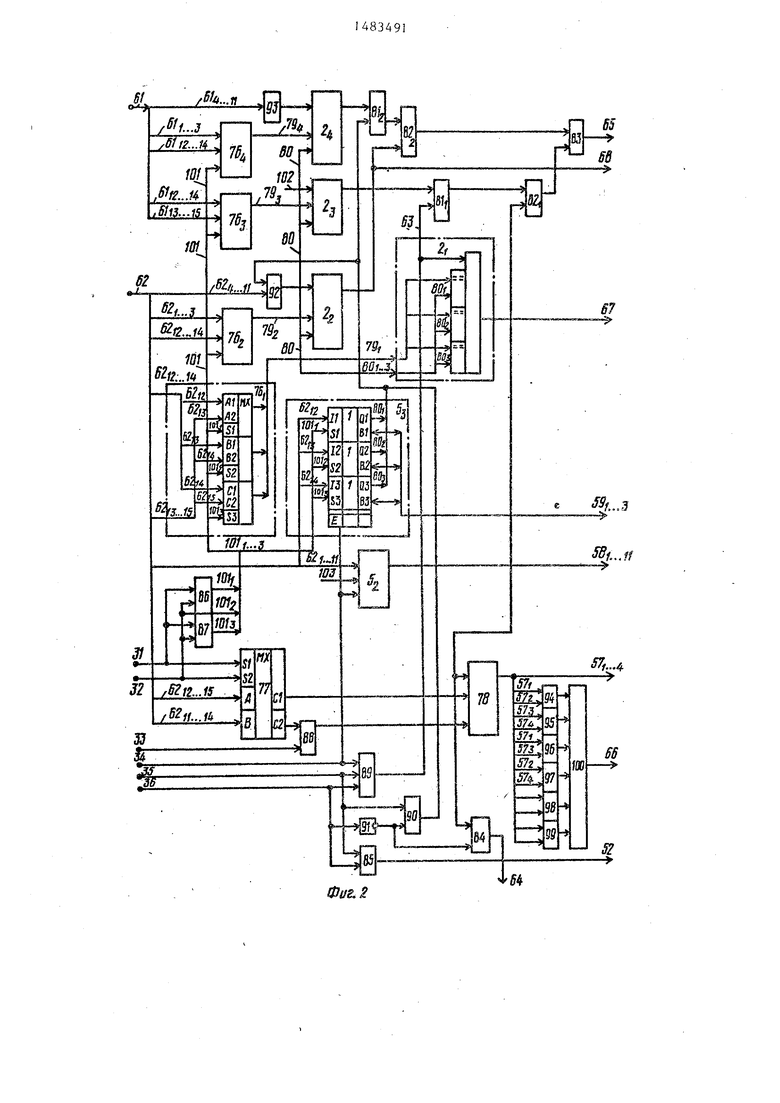

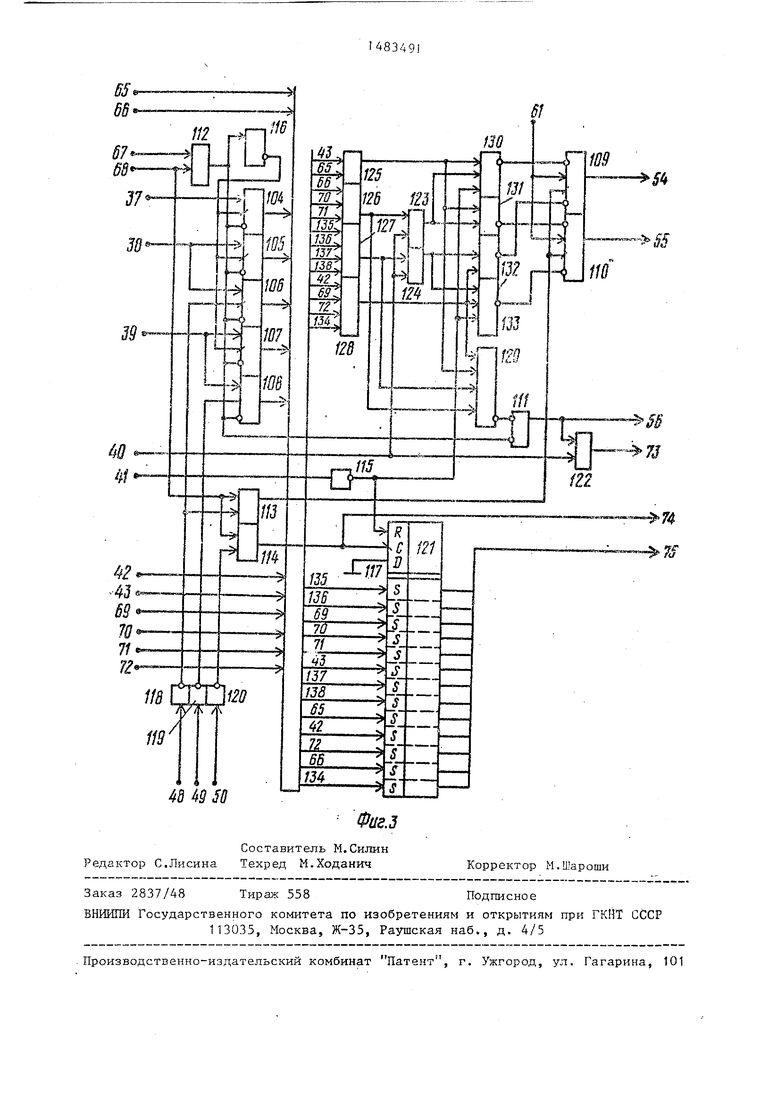

На Аиг.1 предстаьлена функциональная схема предлагаемого устройства;, на Фиг.2 - функциональная схема блока контроля тракта адреса; на фиг.З - функциональная схема блока формирования диагностических сигналов.

На Фигурах приняты следующие обозначения: регистр 1 адреса,- схемы 2« - 2 сравнения, блок 3 контроля адреса; блок 4 Лормирования диагностических сигналов; двунаправленные коммутаторы 5,, - 53 ; триггеры

6 элементы ГГ 9-12; элементы И 13-21; элементы щш 22-24; элементы И-НЕ 25-27; входы 28 признака записи байта, входы 29 признака режима записи, входы 30 признака режима чтения; входы 31-33 признаков режима дешифрации адреса; вход 34 блокрировки деииЛрации адреса, вход 35 синхронизации обмена, вход 36 выборки; вход 37 признака ошибочной работы памяти, вход 38 признака ошибки в младшем байте; вход 34 признака ошибки в старшем байте; вход 40 признака ошибки в цикле обмена; вход 41 начальной установки, вход 42 импульсного признака ошибки памяти; вход 43 признака аварии источника питания; вход 44 блокировки сигналов управления записью-чтением; вход 45 управления подключением пины

Ј

эо

Јъ X)

данных-адреса; вход 46 признака готовности памяти; вход 47 младшего разряда данных-адреса устройства; выходы разрешения младшего 4Я и старшего 49 байтов; выход 50 разрешения считывания; выход 51 разрешения выдачи данных устройства; первый выход 52 управления выборкой устройства; выход 53 синхронизации обмена устройства; выходы 54 и 55 признаков состояния; выход 56 признака ошибочной работы устройства; второй выход 57 управления выборкой устройства; адресный выход 58 устройства; вход-выход 59 кода области адресного пространства устройства; шина 60 данных-адреса устройства; гаины связи 61-75 между элементами устройства; мультиплексоры 76 - 76jf 77; дешифратор 78, выходы 79 - 79# .мультиплексоров; выход 80 двунаправленного коммут.атора; триггеры 81 и 817; элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 82, и 82г, элементы ИЛИ 83, 86; элемен- ты И 87 - 90; элемент НЕ 91; элементы И 92 - 99; элемент ИЛИ 100; входы 10 - мультиплексоров; входы 102 и 103 логических единиц и нуля; триг834914

на соответствующий коду адреса выход 57 выбора памяти и выход 64 блока 3. По приходу любого из сигналов

е на входы 35 и 36 устройства поступающий по пине 60 код адреса фиксируется в регистре 1 адреса одновременно с фиксацией уровней сигналов на входе 28 в триггере 6 н сигнала на вхо- ..

Ю де 47 в триггере 7. Далее устройство выполняет цикл чтения или цикл записи- в управляемую память, или чтение или запись в триггёрных схемах блока 4 в зависимости от наличия

15 сигналов на входах 29, 30, 35, 36 устройства. Цикл чтения начинается по приходу сигнала на вход 30 и пос- Tynaiorjero через элементы НЕ 10, И 19, И-НЕ 25 на выход 50 сигнала

20 разрешения чтения слова из управляемой памяти, при условии наличия сигнала разрешения на выходе 64 блока 3 и отсутствии сигнала блокировки на выходе 73 блока 4, Цикл записи на25 чинается по приходу на вход 29 сигнала, поступающего через элемент НЕ 11, элементы И 20 и 21 и элементы И-НЕ 26 и 27 на выходы 48 и 49 в соответствии с уровнем сигнала на выхо

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения ЭВМ с внешними устройствами | 1985 |

|

SU1288709A1 |

| Многоканальный программируемый преобразователь код-фаза | 1990 |

|

SU1742998A1 |

| Устройство для сопряжения ЭВМ с абонентом | 1987 |

|

SU1439609A1 |

| Многоканальная система сбора и регистрации измерительной информации | 1989 |

|

SU1783547A1 |

| ИМИТАТОР СИГНАЛОВ УПРАВЛЕНИЯ ПОЗИЦИОНИРОВАНИЕМ МАГНИТНЫХ ГОЛОВОК ОТНОСИТЕЛЬНО МАГНИТНЫХ ДИСКОВ | 1991 |

|

RU2017239C1 |

| Устройство для сбора данных о работе ЭВМ | 1982 |

|

SU1121679A1 |

| Устройство для отладки программно-аппаратных блоков | 1987 |

|

SU1497617A1 |

| Устройство для сопряжения ЭВМ с абонентом | 1990 |

|

SU1705832A1 |

| Устройство для отображения информации на экране телевизионного приемника | 1988 |

|

SU1583967A1 |

| Устройство для отладки микроЭВМ | 1987 |

|

SU1587514A1 |

Изобретение относится к вычислительной технике и может быть использовано в системах на основе микроЭВМ для управления оперативными и постоянными запоминающими устройствами. Целью изобретения является повышение достоверности функционирования. Устройство содержит регистр адреса, схему сравнения, блок контроля адреса, блок формирования диагностических сигналов, триггеры 7, элементы НЕ, элементы И, элементы ИЛИ 23, элементы И-НЕ 26, управляющие входы и выходы, шину данных - адреса. Поставленная цель достигается за счет расширения возможностей контроля и диагностики ошибок. 2 з.п. ф-лы, 3 ил., 2 табл.

геры 104-1 1 1 ; элемент ИЛИ И 2; элементы 30 де 28 и значения триггера 7, при усИ ИЗ, 114; элемент ПЕ 115, элемент 116 задержки; вход 137 логического нуля; элементы НЕ 118-120; группа триггеров 121; элементы И 122-124; элементы ИЛИ 125-128, элементы ИЛИ- НЕ 129-133, элементы связи 134-138 между элементами.

Устройство работает следующим образом.

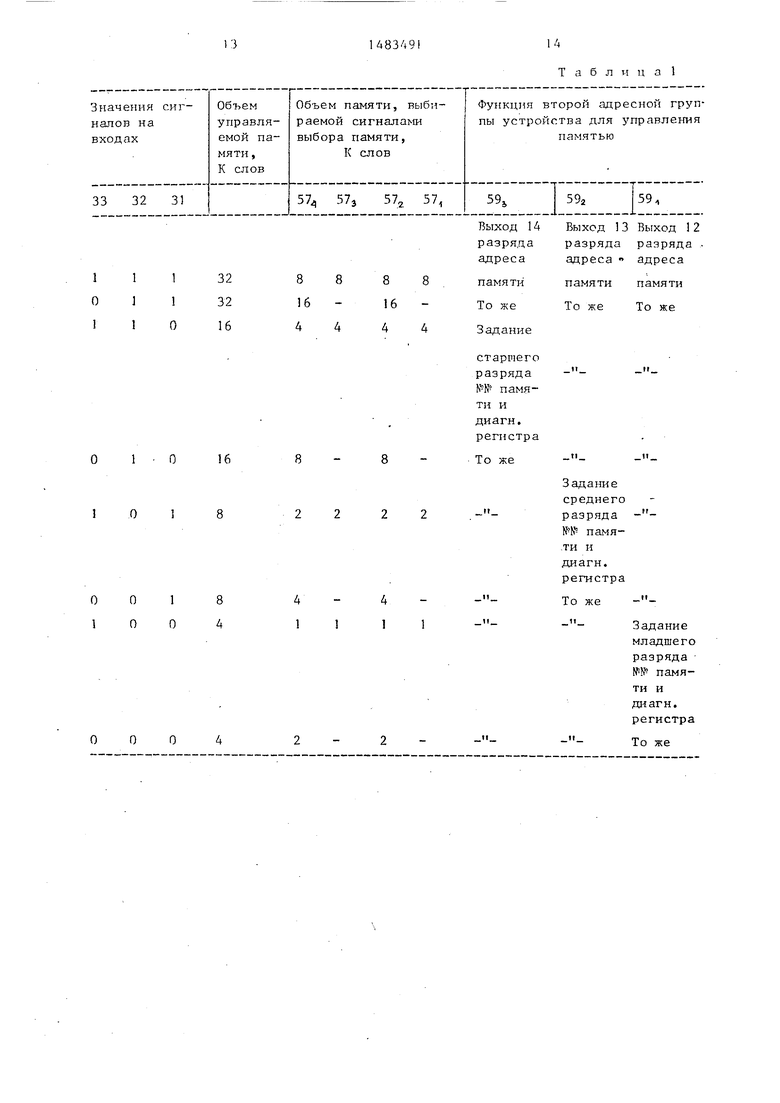

Устройство для управления памятью работает при отсутствии активных уровней сигналов блокировок на входах 34, 44 и 45. По входам 31-34 устройству задается один из режимов селекции адреса, приведенных в табл.1.

В соответствии с заданным устройству режимом селекции адреса по входам 59 устройству задается код номера управляемой памяти, т.е, задаются значения одного, двух или трех разрядов кода адреса, при совпадении с которыми (разряды кода адреса, поступающие по шине 60 через блок 5( , регистр 1 адреса и блок. 3) схема 2( сравнения выдает активный уровень сигнала на выходе 67, разрешающий выдачу активного уровня сигнала

35

40

45

50

55

ловии наличия сигнала разрешения на выходе 64 блока 3 и отсутствии сигнала блокировки на выходе 73 блока 4. В ответ на сигналы на выходах 48- 50 устройства управляемая память должна выдать сигнал на вход 46 устройства, по которому через элементы НЕ 12 и И 18 устанавливается триггер 8. При этом формируется активный уровень сигнала на выходе 53 устройства и разрешается -выдача элементом И 18 сигнала управления подключением к общей шине управляемой памяти на выходе 51 устройства в цикле чтения. Возврат триггера 8 в исходное состояние осуществляется через элемент ИЛИ 22 по синхровходу триггера 8 концом сигналов на входах 28 или 30.

Сигнал блокировки выдачи управляющих сигналов на выходе 73 блока 4 формируется в нем элементом И 22 при поступлении на вход 40 устройства активного уровня сигнала-, а также при обнаружении ошибок имеющимися в устройстве средствами контроля или поступлении на входы 37-39, 42 и 43 устройства сигналов - признаков ошибок. На элементах И 13-16 реализован контроль, выявляющий некорректные

5

0

5

0

5

ловии наличия сигнала разрешения на выходе 64 блока 3 и отсутствии сигнала блокировки на выходе 73 блока 4. В ответ на сигналы на выходах 48- 50 устройства управляемая память должна выдать сигнал на вход 46 устройства, по которому через элементы НЕ 12 и И 18 устанавливается триггер 8. При этом формируется активный уровень сигнала на выходе 53 устройства и разрешается -выдача элементом И 18 сигнала управления подключением к общей шине управляемой памяти на выходе 51 устройства в цикле чтения. Возврат триггера 8 в исходное состояние осуществляется через элемент ИЛИ 22 по синхровходу триггера 8 концом сигналов на входах 28 или 30.

Сигнал блокировки выдачи управляющих сигналов на выходе 73 блока 4 формируется в нем элементом И 22 при поступлении на вход 40 устройства активного уровня сигнала-, а также при обнаружении ошибок имеющимися в устройстве средствами контроля или поступлении на входы 37-39, 42 и 43 устройства сигналов - признаков ошибок. На элементах И 13-16 реализован контроль, выявляющий некорректные

514834916

комбинации сигналов на входах 28 - 30, значений триггеров

46 и 47 устройства, а также на выходе 64. Средства контроля блока 3 реализованы на дублирующих основной тракт селекции адреса мультиплексорах 76з,4 схемах -з,и сравнения; триггерах 8(г , элементах ИСКЛЮЧАВ- 1 ГЕЕ ИЛИ .

При не совпадении результатов селекции кода адреса в основном и дублирующем тракте блок 3 выдает сигнал на выход 65. На элементах И 94-99 и элементе ИЛИ 00 осуществляется контроль зависания сигналов на выходах 57 устройства, т.е. при появлении более одного активного уровня на выходах 57 формируется сигнал на выходе 66 блока 3. Значения сигналов на входах 37-39 устройства фиксируются в блоке 4 в момент их достоверного значения в триггерах 104, 105, -I 107 по сигналам на входах 67 или 68 блока 4, а в триггерах 106 и 108 - по сигналам на выходах 48 и 49 устройства соответственно. Сброс триггеров 104 - 108, а также триггера 111, на выходе которого формируется сигнал признака обнаружения ошибки на выходе 56 устройства, производится при отсутствии обращения к устройству по общей шине, т.е. при отсутствии сигналов на входах 67, 58 блока 4. Активные уровни сигналов на выходах 134-138 триггеров 104-108, а также остальных признаков ошибок, поступающих на входы 42, 43, 65, 66, блока 4, устанавливают соответ- ствукчдие разряды группы триггеров 121, через элементы ИЛИ 125-128 и элемент ИЛИ-НЕ 129 устанавливают триггер 111. Кроме того, при этом может изменяться состояние триггеров 109, 110 в соответствии с табл.2.

Выходы 75 группы триггеров 121 доступны через коммутатор 5 для прочтения по шине 60 устройства при специальных обращениях к нему в цикле чтения как к внешнему устройству по адресу, соответствующему заданному режиму селекции и номеру управляемой памяти, из области адресов (170000 + 170008) В. По завершению этого обращения происходит запись нулевых значений во все разряды группы триггеров 121. При обращении по этому адресу к устройству в цикле записи производится установка

20

25

чению уровней сигна блока 4. По активно ла на входе 41 устр дится начальная уст 109 и 110 и всех ра триггеров 121, i Формула из

1, Устройство дл мятью, содержащее р схему сравнения, тр 15 ре элемента НЕ, дев три элемента ИЛИ, т причем вход признак устройства подключе му входу первого тр входу первого элеме дам первого и второ выход первого тригг элемент НЕ подключе ду второг элг-уснта ка режима записи и чтения устройства п дам второго и трет НЕ, выход второго э чен к первому вхспу та И, ьторому входу И, первым входам тр го и пятого элемент третьего элемента Н второму входу второ вторым входам треть и третьего элемент дам шестого и седьм синхровход регистра к стробируюцему вх ния, синхровходам п триггеров, инверсный триггера подключен к первого элемента ИЛИ входу первого элемен ход и информационный триггера подключены второму входу второ и к входу младшего р адреса устройства, в второго элементов И соответственно к вто того и пятого элемен которых подключены с первым входам первог ментов И-НЕ, вторые подключены к входу б лов управления запис ройства, выход треть подключен к синхровх

30

35

40

45

50

55

значений триггеров

0

5

09 и НО по значению уровней сигналов на входе 61 д блока 4. По активному уровню сигнала на входе 41 устройства производится начальная установка триггеров 109 и 110 и всех разрядов группы триггеров 121, i Q Формула изобретения

1, Устройство для управления памятью, содержащее регистр адреса схему сравнения, три триггера, четы- 5 ре элемента НЕ, девять элементов II, три элемента ИЛИ, три элемента И-НЕ, причем вход признака записи байтя устройства подключен к чго- му входу первого триггера, первому входу первого элемента И, первым входам первого и второго элементов ПЛИ, выход первого триггера черря первый элемент НЕ подключен к первому входу второг элг-уснта И5 Bxoni прзюпа- ка режима записи и признака режима чтения устройства подключены к входам второго и третьего элементов НЕ, выход второго элемента НП пг,гклч- чен к первому вхспу --ретьего элемента И, ьторому входу псрьсго элемента И, первым входам третьего, четвертого и пятого элементов 1Г71Т, г- ход третьего элемента НЕ подклочен к второму входу второго этем21 тм Л, вторым входам третьего элемента И и третьего элемент 1ШИ, первьта входам шестого и седьмого элементов И, синхровход регистра адреса подключен к стробируюцему входу схемы сравнения, синхровходам первого и второго триггеров, инверсный выход второго триггера подключен к второму входу первого элемента ИЛИ и к третьему входу первого элемента И, прямой выход и информационный вход второго триггера подключены соответственно к второму входу второго элемента ИЛИ и к входу младшего разряда данных адреса устройства, выходы первого и второго элементов ИЛИ подключены соответственно к вторым входам четвертого и пятого элементов Н, выходы которых подключены соответственно к первым входам первого и второго элементов И-НЕ, вторые входы которых подключены к входу блокировки сигналов управления записью-чтением устройства, выход третьего элемента ИЛИ подключен к синхровходу третьего

0

5

0

5

0

5

триггера, информационный вход и вход установки в 1 которого подключены соответственно к входу логического нуля устройства и к выходу восьмого элемента II, о т л и ч а ю щ е е с я тем, что, с целью повышения достоверности функционирования, в него введены блок контроля адреса, блок формирования диагностических сигналов и двунаправленный коммутатор, причем входы блока контроля адреса с первого по восьмой подключены соответственно к входам признака режима чтения, первого, второго, третьего признаков режима дешифрации адреса, блокировки дешифрации адреса, синхронизации обмена,выборки устройства, выходу регистра адреса, выходу схемы сравнения, вход-выход блока контроля адреса подключен к входу-выходу кода области адресного пространства устройства, выход двунаправленного коммутатора подключен к информационному входу регистра адреса, девятому входу блока контроля адреса и к первому входу блока формирования диагностических сигналов, входы которого с второго по девятнадцатый подключены соответственно -к выходу схемы сравнения, первому, второму и третьему выходам бло ка контроля адреса, входам признака ошибочной работы памяти, признака ошибки в младшем байте, признака ошибки в старшем байте, признака ошибки в цикле обмена, начальной установки, импульсного признака ошибки памяти, признака аварии источника питания устройства, выходам второго, третьего первого и девятого элементов II, выходам второго, первого и третьего элементов И-НЕ, выходы с четвертого по девятый блока контроля адреса подключены соответственно к первому и второму информационным входам схемы сравнения, стробирующсму входу схемы сравнения, первому и второму выходам управления выборкой и к адресному выходу устройства, десятый выход блока контроля адреса подключен к первому входу девятого -элемента И, второму входу шестого элемента И, третьим входам четвертого и пятого элементов II, вход признака готовности памяти устройства через четвертый элемент НЕ подключен к второму входу девятого элемента И и к первому входу восьмого элемента И, второй вход которого подключен к третьему выхо0

5

0

5

0

5

0

5

0

5

ду блока контроля адреса, выход шестого элемента И подключен к первому входу третьего элемента И-НЕ, второй вход которого подключен к входу блокировки сигналов управления за- пнсыо- чтением устройства, выходы блока формирования диагностических сигналов подключены соответственно к входу направления передач и информационному входу двунаправленного коммутатора, первому и второму выходам состояния устройства, выходу признака ошибочной работы устройства и к третьим входам первого, второго и третьего элементов И-НЕ, выходы которых подключены соответственно к выходам разрешения записи младшего байта, старшего байта и разрешения считывания устройства, прямой и инверсный выходы третьего триггера подключены соответственно к второму входу седьмого элемента И и к выходу синхронизации обмена устройства, выход седьмого элемента И подключен к выходу разрешения выдачи данных устройства, вход управления подключением шины данных адреса устройства подключен к управляющему входу двунаправленного коммутатора, вход-выход которого подключен к шине данных адреса устройства,

91483491

к второму входу третьего элемента И, первогу входу четвертого элемента И, первому входу второго элемента ИЛИ, шестой вход блока подключен к третье- ему входу, через первый элемент НЕ к второму входу четвертого элемента И и первому входу третьего элемента ИЛИ, седьмой вход блока подключен

к первым и вторым информационным вхо- JQ элементов И с седьмого по двенадцадам мультиплексоров с первого по третий, информационным входам первого и второго двунаправленных коммутаторов, входам с первого по восьмой пятого элемента И, управляюгдий вход двунаправленного коммутатора подключен к входу логического нуля устройства, восьмой вход блока подключен к первому входу первого элемента

ИСКЛЮЧАЮЩЕЕ ИЛИ, второму входу треть- 2Q входу пятого элемечга И, выход кото25

30

35

его элемента ИЛИ, стробирующему входу дешифратора, вход-выход блока подключен к входу-выходу первого двунаправленного коммутатора, девятый вход блока подключен к входам с первого по восьмой шестого элемента И, первому и второму информационным входам четвертого и пятого мультиплексоров, выходы четвертого и пятого элементов И подключены к первом} и второму выходам блока, выход первой схемы сравнения подключен к первому входу второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и к третьему выходу блока, выход второго мультиплексора подключен к четвертому выходу блока, выход первого двунаправленного комму- татора подключен к пятому выходу блока, первым информационным входам первой, второй и третьей схем сравне- .-. ния, вторые входы которых подключены соответственно к выходам третьего, четвертого и пятого мультиплексоров, выход четвертого элемента И подключен к синхровходу первого триггера и к шестому выходу блока, выход второго элемента ИЛИ подключен к седьмому выходу блока, выход дешифратора подключен к восьмому выходу блока, вы-, ход второго двунаправленного мультиплексора подключен к девятому выходу блока, выход третьего элемента ИЛИ подключен к десятому выходу блока, первый разряд выхода дешифратора подключен к первым входам седьмого, восьмого и девятого элементов И, второй разряд выхода дешифратора подключен к второму входу седьмого элемента И, первым входам десятого и

50

55

poi o подключен к строопру:сщему входу первой схемы сравнения, стробирующие входы второй и третьей схем сравнения подключены соответственно к входу логической единицы устройства к к выходу шестого элемента И, выходы второй и третьей схем сравнения подключены соответственно к информационным входам первого и второго триггеров, выходы котори;: подключены соответственно к вторым входам первого и второго элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, выходы которых подключены соответственно к первому и второму входам четвертого элемента ИЛИ.

одиннадцатого элементов И, третий разряд выхода дешифратора подключен к первому входу двенадцатого элемента И, вторым входам восьмого и одиннадцатого элементов И, четвертый разряд выхода дешифратора подключен к вторым входам одиннадцатого, десятого и девятого элементов И, выходы

тый подключены соответственно к входам с первого по шестой пятого элемента ИЛИ,, первый выход первого мультиплексора подключен к первому входу дешифратора, второй выход первого мультиплексора подключен к второму входу депийратора, выход гет- вертого элемента И подключен к синх- ровходу второго трип гра и второму

25

30

5

.-.

0

5

poi o подключен к строопру:сщему входу первой схемы сравнения, стробирующие входы второй и третьей схем сравнения подключены соответственно к входу логической единицы устройства к к выходу шестого элемента И, выходы второй и третьей схем сравнения подключены соответственно к информационным входам первого и второго триггеров, выходы котори;: подключены соответственно к вторым входам первого и второго элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, выходы которых подключены соответственно к первому и второму входам четвертого элемента ИЛИ.

Q § 0 5 0 0

5

0

5

второму входу втопого элемента ИЛИ и к входу установки десятого триггера группы, тринадцатый вход блока подключен к третьему входу четвертого элемента ИЛИ и к входу установки в 1 одиннадцатого триггера группы, четырнадцатый вход блока подключен к второму входу третьего элемента ИЛИ и к входу установки в 1 двенадцатого триггера группы, пятнадцатый . вход блока подключен к третьему входу третьего элемента ИЛИ и к входу установки в 1 тринадцатого триггера группы, шестнадцатый вход блока подключен к четвертому входу четвертого элемента ИЛИ и к входу установки в 1 четырнадцатого триггера группы, семнадцатый вход блока через второй элемент НЕ подключен к синхро- входу седьмого триггера, восемнадцатый вход блока через третий элемент НЕ подключен к второму входу первого элемента И и к синхровходу пятого триггера, девятнадцатый вход блока через четвертый элемент НЕ подключен к второму входу второго элемента И, выход второго элемента ИЛИ подключен к второму входу первого элемента ИЛИ- НЕ и к первым входам третьего и четвертого элементов ИЛИ-НЕ, выход третьего элемента ИЛИ подключен к вторым входам третьего элемента И и четвертого элемента ИЛИ, выход которого подключен к второму установочному входу восьмого триггера, выход четвертого элемента ИЛИ подключен к первому входу пятого элемента ИЛИ- НЕ, второму входу второго элемента ИЛИ-НЕ и к третьему входу четвертого элемента ИЛИ-НЕ, выход пятого элемента ИЛИ подключен к второму входу четвертого элемента И и к четвертому входу четвертого элемента ИЛИ-ГЕ, выход третьего элемента И подключен к второму входу третьего элемента ИЛИ- ГЕ и к третьему входу первого элемента ИЛИ-НЕ, выходы третьего и пятого элементов ИЛИ-НЕ подключены соответственно к вторым установочным входам первого и второго триггеров, выход четвертого элемента И подключен к второму входу пятого элемента ИЛИ-НЕ и к третьему входу второго элемента ИЛИ-НЕ.

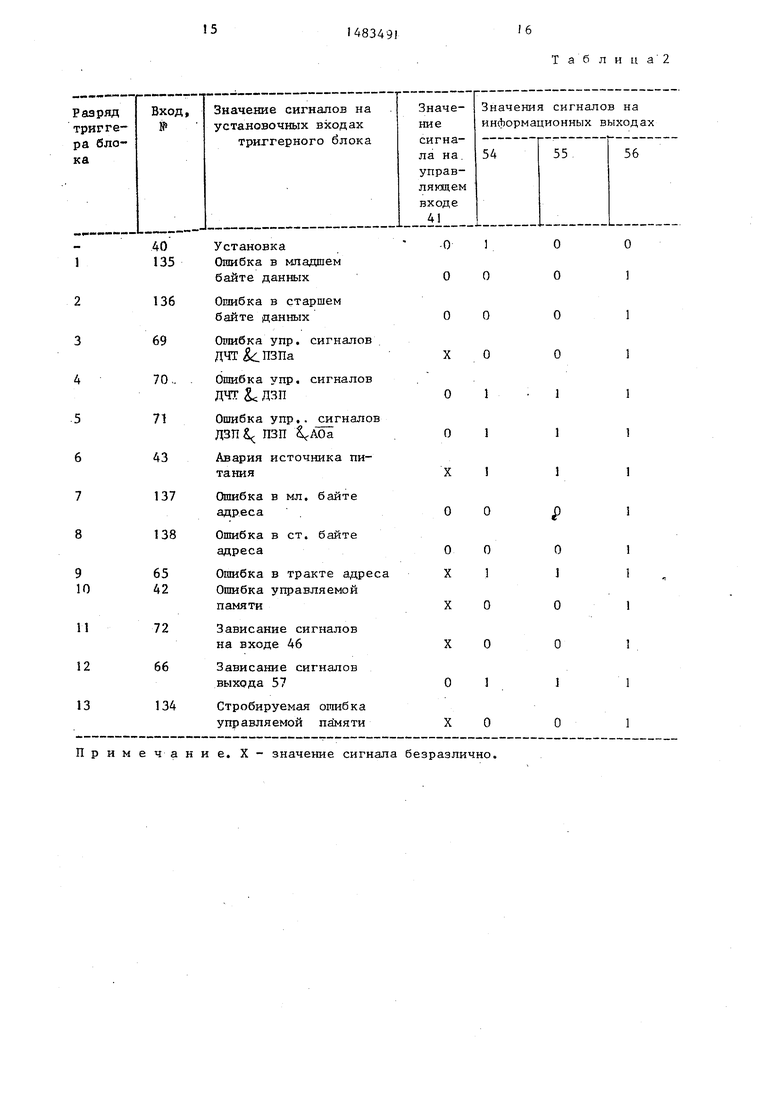

Т а б л и и а 1

Примечание. X - значение сигнала безразлично.

Т а б л и ц а 2

Редактор С.Лисина

Составитель М.Силин Техред М.Ходанич

Фиг.з

Корректор М.Шароши

| Устройство управления буферной памятью | 1985 |

|

SU1305771A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Устройство для управления памятью | 1984 |

|

SU1243030A1 |

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

Авторы

Даты

1989-05-30—Публикация

1987-07-30—Подача