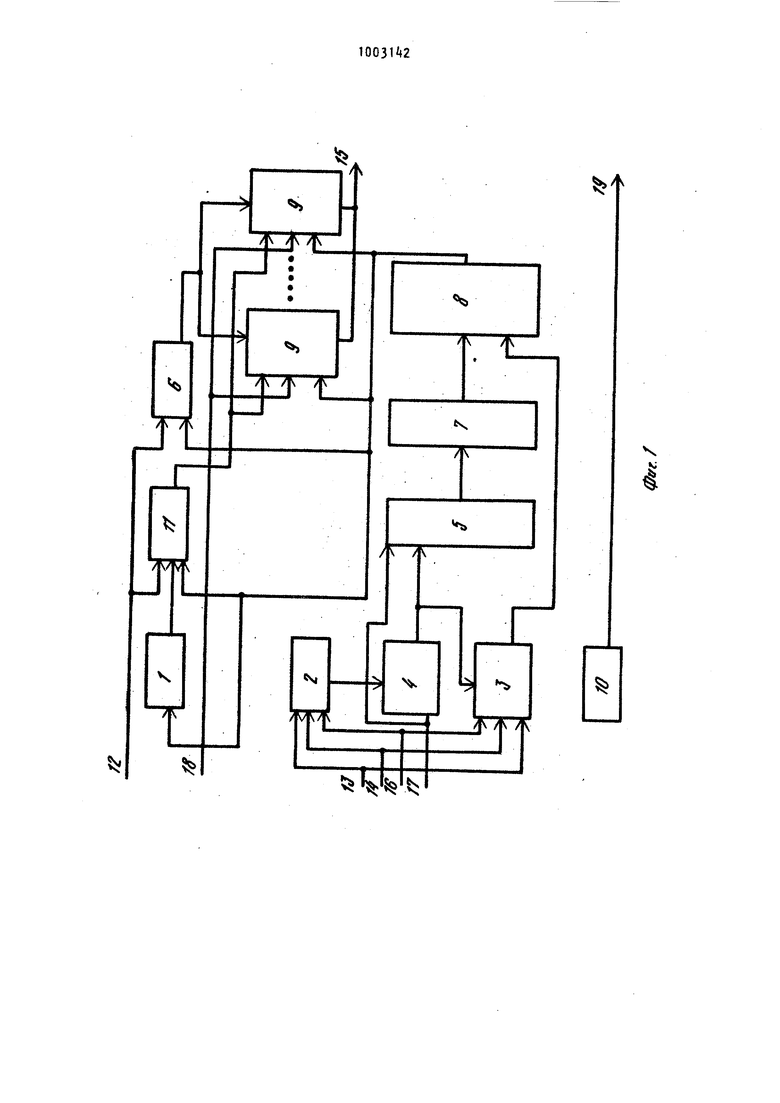

Изобретение относится к запоминающим устройствам и может быть применено в универсальных цифровых вычислительных машинах в качестве ос новной оперативной памяти. Известно устройство, содержащее полупроводниковые. памяти, счет чик адреса регенерации и обращения, дешифраторы, формирователи записи и считывания til. Недостатком этого устройства является невозможность использовать его в качестве основной оперативной памяти цифровых вычислительных машин Наиболее близким техническим решением к предлагаемому является дина мическое оперативное запоминающее устройство, содержащее счетчик адреса регенерации, выходы которого подключены к-первой группе входов мультиплексора, адресов обращений и регенерации, причем вторая группа вход мультиплексора соединена с шиной код адреса, а выходы мультиплексора соединены с адресными входами плат динамической памяти, состоящих из запоминающих динамических микросхем и логических микросхем обрамления, выходы считываемой информации плат прдключены к шине считываемой информации , дешифратор старших разрядов кода адреса, входы которого подключены к шине двух старших разрядов кода адресов, а выходы соединены со входами выбора запоминающих микросхем плат динамической памяти, схему ИЛИ, аходы которой подключены соответственно к входам обращения записи, чтения устройства, регистр режимов, состоящий из триггеров чтения, записи, регенерации, схему управляющих сигналов, состоящую из вентильных логических элементов, первая группа входов которой подключена к выходам регистра режимов, вторая группа входов соединена с выходами формирователей сигналов, а а выходы схемы управляющих сигналов соединены со входами управления плат динамической памяти, входы записываемой информации которых соединены с шиной записываемой информации и мультивибратор выработки команды регенерации и одновибраторы с подстрое ными резистором и конденсаторами, предназначенными для формирования временной диаграммы работы плат динамической памяти 21 . Недостатком этого устройства являются наличие одновибраторов с подстроенными R, С электрорадиоэлементами и то, что обращение на регенерацию формируется в самом устройстве и при многоблочной организации каждым блок ОЗУ будет переходить в режим регенерации в произвольные моменты вре мени независимо от других блоков, за счет чего снижаются надежность и быстродействие устройства. Цель изобретения - повышение надежности устройства. Поставленная цель достигается тем что в динамическое оперативное запоминающее устройство, содержащее блоки памяти, дешифратор адреса, счетчик блок местного управлен1 я, мультиплексор, одни из входов которого соединены со входами дешифратора адреса и являются адресными входами устройства, регистр режимов и элемент ИЛИ, первые и вторые входы крторых соответственно объединены и являются входом записи и входом чтения устройства причем выходы счетчика подключены к другим входам мультиплексора, выходы которого соединены с адресными входами блоков памяти, входы выборки которых подключены к выходам дешифратора адреса, управляющие входы которого входы счетчика , управляющие входы мультиплексора и блоков памяти подключены к выходам блока.местного управления, одни из входов которого соединены с выходами регистра режимов, информационные входы и выходы блоков памяти являются соответственно информациоными входами и выходами устройства, введены селектор, регистр сдвига, регистр управляющих сигналов и формирователь сигналов, причем первый вход селектора соединен с первым входом регистра сдвига и является входом синхронизации устройства, а второй вход и выход подключены соответственно к выходу элемента ИЛИ и к третьему аходу регистра режимов и второму входу регистра сдвига, выходы которого соединены со входами регистра управляющим сигналов, выходы которого подключены к другим входам блока местного управления, третий вход элемента ИЛИ и четвертый вход регистра режимов объединены и являются входом регенерации устройства, управляющим выходом которого является выход формирователя сигналов. На фиг.1 изображена-функциональная схема предложенного устройства; на фиг,2 - функциональная схема селекторов; на фиг,3 - формирователь импульсов. Устройство содержит (фиг,1) счетчик 1, элемент ИЛИ 2, регистр 3 режимов, селектор 4, предназначенный для .выделения тактового сигнала обращения, регистр 5 сдвига, дешифратор 6 адреса, регистр 7 управляющих сигналов, блок 8 местного управления, состоящий из элементов И, блоки 9 памяти, формирователь 10 сигналов, предназначенный для управления регенерацией, и мультиплексор 11, На фиг.1 обозначены адресный вход 12, вход 13 записи, вход 14 чтения, выходы 15 устройства, вход 16 регенерации, вход 17 синхронизации и информационные входы 18 устройства и выход 19 формирователя сигналов. Селектор (фиг,2 содержит первый 20 триггер с установочным входом 21, второй 22 триггер и элемент И 23 с выходом 2, Формирователь сигналов содержит (фиг,3) генератор 25 сигналов, сметчик 26 и элемент И 27. Каждый блок 9 памяти.имеет организацию 256 К X 72 разряда и содержит 72 платы динамической памяти, каждая из которых имеет организацаю 6А Кх4 разряда. Платы динамической памяти выполнены на запоминающих динамических микросхемах с организацией 16 Кх1 разряд. Устройство работает следующим образом. В режиме записи по входу 13 (фиг.1) поступает сигнал записи на первый вход элемента ИЛИ 2 и на вход регистра 3, при этом триггер записи в регистре 3 устанавливается в 1 на время цикла записи. Селектор выделяет тактовый сигнал, который поступает на регистр 5, формирующий сдвинутую 5100 последовательность синхронизирующих сигналов. Время сдвига этих сигналов задается периодом синхронизации высо кочастотного- сигнала, поступающего по входу 17. Регистр 7 формирует сигналы управ ления требуемой задержки и длительности . Блок 8 формирует временную диаграмму работы блоков 9 в режиме записи. По входу 12 поступает код адреса, причем младшие разряды кода адреса (четырнадцать разрядов )посту пают на мультиплексор 11 для выбора требуемой ячейки памяти. Для старших разряда кода адреса поступают на дешифратор 6 для выбора требуемых за поминающих микросхем. По входу 18 поступает код записываемой информации, В режиме чтения по входу 1 посту пает сигнал чтения на второй вход элемента ИЛИ 2 и на второй вход регистра 3, Триггер чтения в регистре 3 устанавливается в 1 на время цикла чтения. Работа устройства аналогична работе в режиме записи. Блок 8 формирует временную диаграмму работы блоков 9 памяти в режиме чтения По выходам 15 считывается информация из блоков 9В режиме регенерации по входу 16 поступает сигнал регенерации на третий вход элемента ИЛИ 2 и на вход регистра 3 в ответ на сигнал требования регенерации, поступающего с выхода 19 формирователя 10, Триггер регенерации в регистре 3 устанавливается в 1 на время цикла регенерации , Адрес регенерации формируется на счетчике 1 и поступает через мультиплексор 11 на блоки 9 памяти, Работа селектора и регистров 5 и 7 аналогична работе в режиме записи. Дешифратор 6 формирует сигналы выбора всех запоминающих микросхем блоком 9 памяти. Блок 8 формирует временную диаграмму работы устройства в режиме регенерации. Введение в устройство селектора 4 регистров 5 и 7 и формирователя 10 сигналов позволило исключить применение подстроечных резисторов и конденсаторов, за счет чего повышаются надежность и быстродействие устройст . ва, а также сокращается время его наладки, Технико-экономическое преимущесто предлагаемого устройства заключатся в его более высокой надежности о сравнению с прототипом, Формула изобретения Динамическое оперативное запоинающее устройство, содержащее блоки амяти, дешифратор адреса, счетчик, лок местного управления, мультиплексор, одни из входов которого соединены с входами дешифратора адреса и яв1ляются адресными входами устройства, регистр режимов и элемент ИЛИ, первые и вторые входы которых соответственно объединены и являются входом записи к входом чтения устройства, причем выходы счетчика подключены к другим входам мультиплексора, выходы которс)го соединены с адресными входами бАоков памяти , входы выборки которых подключены к выходам дешифратора адреса, управляющие входы которого, входы , управляющие входы мультиплексора и блоков памяти подключены к выходам блока местного управления, одни из входов которого соединеныс выходами регистра режимов, информационные входы -и выходы блоков памяти являются соответственно информационными входами и выходами устройства, отличающееся тем, что, с целью повышения надежности устройства, в него введены селектор, регистр сдвига, регистр управляющих сигналов и формирователь сигналов, причем первый вход селектора соединен с первым входом регистра сдвига и является входом синхронизации устройства, а второй вход и выход подключены соответственно к выходу элемента ИЛИ и к третьему входу регистра режимов и второму входу регистра сдвига, выходы которого соединены с входами регистра управляющих сигналов, выходы которого подключены к другим входам блока местного управления, третий вход элемента ИЛИ и четвертый вход регистра режимов объединены и являются входом регенерации устройства, управляющим выходом которого является выход формирователя сигналов. Источники информации, принятые во внимание при экспертизе 1, Авторское свидетельство СССР № 691925, кл, G 11 С П/З, 1977. 2, Патент США ГР 3790961, кл,- 3 0-173, опублик, 1975 (прототип)

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля памяти | 1983 |

|

SU1129656A1 |

| Устройство для отображения информации на экране электронно-лучевой трубки | 1985 |

|

SU1352477A1 |

| Запоминающее устройство | 1985 |

|

SU1249594A1 |

| Запоминающее устройство с самоконтролем | 1989 |

|

SU1718276A1 |

| Устройство для отображения информации | 1984 |

|

SU1354182A1 |

| Устройство для контроля динамических блоков памяти | 1985 |

|

SU1282221A1 |

| Устройство для управления сверхоперативной буферной памятью мультипроцессорной ЭВМ | 1981 |

|

SU980097A1 |

| УСТРОЙСТВО ДЛЯ ПОИСКА ПЕРЕМЕЖАЮЩИХСЯ НЕИСПРАВНОСТЕЙ В МИКРОПРОЦЕССОРНЫХ СИСТЕМАХ | 1992 |

|

RU2030784C1 |

| Многоканальное устройство для сопряжения ЭВМ | 1988 |

|

SU1695311A1 |

| Устройство для контроля времени работы оборудования | 1990 |

|

SU1815664A1 |

J1

J

ч

УГ

Si

ч

ч

/

/V /

J

jwrvv

т

Авторы

Даты

1983-03-07—Публикация

1981-10-13—Подача