1

Изобретение относится к технике передачи данных и может быть испопьзовано в аппаратуре, предназначенной для передачи данных с решающей обратной связью с непрерывной передачей информации.

Известно устройство, предназначенное для обнаружения ошибок, содержащее ограничитель данных, фиксатор входной информ&ции, регистр сдвига, элемент ИЛИ, ограничитель синхросигналов, детектор синхроимпульсов, блокирующий блок, генераторы им- пульсов, предварительный коррелятор, детекторы импульсов, импульсов выборки и счетчик С 11.

В этом устройстве с целью обнаружения ошибок местный код синхронизируется и сравнивается с псевдослучайным кодом, переданным по каналу связи.

Известно также устройство для приема дискретной информации, содержащее основной декодирующий блок, выход которого соединен с входом блокирующего регистра, и первый и второй блоки памяти, информационные входы и выходы которых соединены соответственно через блок для мажоритарного сложения с входом дополнительного декодирующего блока и входом выходного накопителя, другие входы которого подключены соответственно к информационным входам блоков памяти и выходу первого блока памяти 2.

Однако в этом известном устройстве при обнаружении ошибок стираются не только искажения, но и следующие за ней комбинации и при их повторном приеме комбинация, принятая с ошибкой, запрашивается вновь независимо от того, с ошибкой или без ошибки она была принята первый раз. Причем комбинация, принятая с ошибкой, запрашивается до тех пор, пока не будет принята правильно, что приводит к снижению скорости передачи информации.

Целью изобретения является увеличение скорости передачи информации.

Для этого в устройство введены управлющий блок, делитель на три, сравниватель признаков, промежуточный накопитель и блок для запоминания признаков, при этом входы управляющего блока соединены соо-гветственно с выходом регистра для блокиро

ки непосредственно, а также через делитель на три, и с выходом сравниватепя признаков, входы которого соединены с выходом Ьсновного декодирующего блока непосредст венно и через блок для запоминания признаков, а выходы управляющего блока подключены соответственно к входу регистра блокировки, другой вход которого соединен с выходом дополнительного декодирующего блока, и к входам делителя на три, выходного накопителя, сравнивателей и блоков для запоминания признаков и первого и второго блоков памяти, информационные входы которых через промежуточный накопитель соединены с входом основного декодирующего блока.

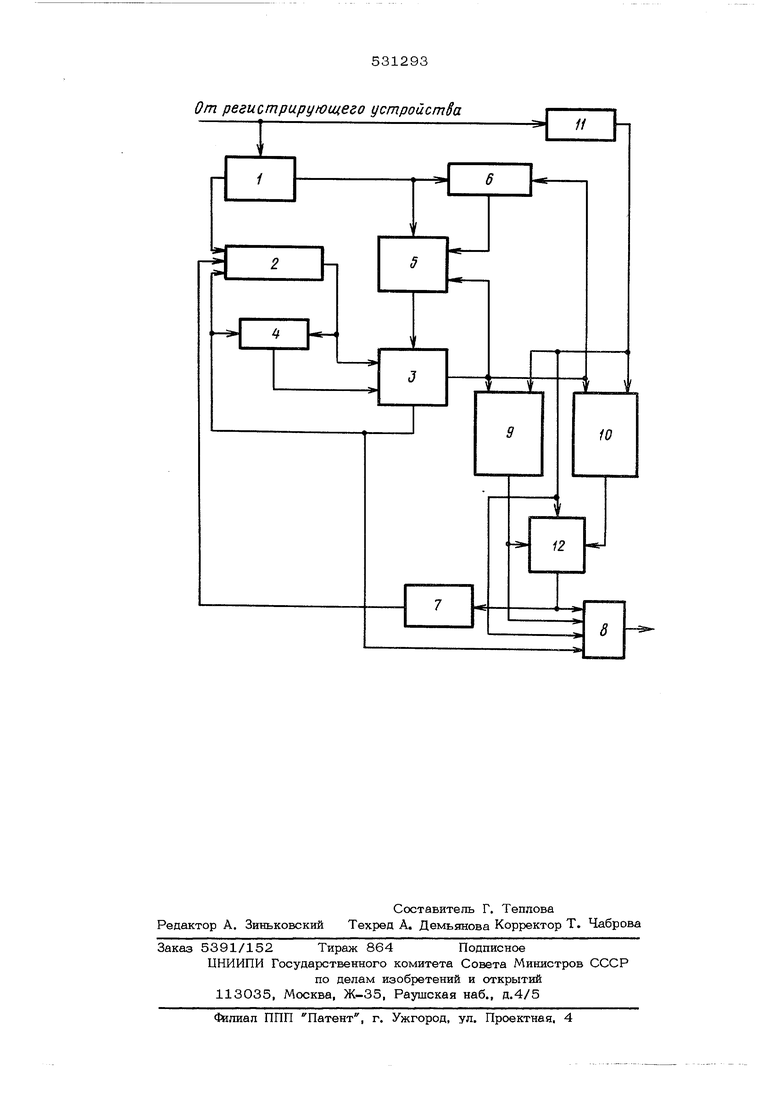

Это позволяет при повторении приема принятую с ощибкой комбинацию выдать из запоминающего устройства, если она при певой передаче была принята правильно. В результате чего можно избежать повторных переспросов тех комбинаций, которые уже были переданы по каналу связи без ощибок. На чертеже приведена структурная электрическая схема устройства.

Устройство для приема дискретной информации содержит основной декодирующий блок 1, выход которого соединен с одним из входов регистра 2, предназначенного для блокировки, выход которого соединен Z двумя входами управляющего блока 3 непосредственно, а также через делитель 4 на три, третий вход управляющего блока 3 соединен с выходом сравнивателя признаков 5, входы которого соединены с выходом основного декодирующего блока 1 и через блок для запоминания признаков 6, а выходы управляющего блока 3 подключены соответственно к входу регистра 2, другой вход которого соединен с выходом дополнительного декодирующего блока 7, и к входам делителя 4, выходного накопителя 8, сравнивателя признаков 5, блока для запоминания признаков 6 и первого 9 и второго 10 блоков памяти, информационные входы которых через промежуточный накопитель 11 соединены с входом основного декодирующего блока 1, а также через блок 12 для мажоритарного сложения - с входом дополнительного декодирующего блока 7 и входом выходного накопителя 8, выходы блоков памяти 9 и 10 соединены также через блок 12 с соответствующим входом, соединенным также с выходом блока памяти 9 непосредственно, выходного накопителя 8, выход которого является выходом устройства, подключенным к регистрирующему устройству (не показан).

Устройство работает следующим образом На входы промежуточного накопителя 1 и основного декодирующего блока 1 поэле-

ментно поступают П -элементные кодовые комбинации.

В случае отсутствия или необнаружения ощибок принятые комбинации с выхода промежуточного накопителя 11 поэлементно поступают на вход выходного накопителя 8, с выхода которого в случае необнаруже- ния ощибок в следующей кодовой комбинаш информационные эгэменты поступают на регистрирующее устройство.

При обнаружении в принятой комбинации ощибки сигналом с выхода основного декодирующего бпока 1 запускается регистр 2, а сигналом с выхода управляющего блока 3, осуществляется блокировка выхода выхоного накопителя 8. При этом элементы комбинации, предшествующей ощибочной, записанные в выходном накопителе 8, стирают ся сигналом с выхода управляющего блока 3, открываются информационный вход первого блока памяти 9 и вход блока 6 для запоминания признаков, элементы принятой с ощибкой и следующих за ней комбинаций записываются в блоке памяти 9, а их признаки - в блоке 6 для запоминания признаков, причем комбинациям, принятым без ощибки, присваивается признак О, а принятым с ощибкой - признак 1. При по&торном приеме запращиваемой комбинации регистр 2 сигналом с выхода блока 3 запускается вновь независимо от того, с ошикой или без ощибки будет принята эта комбинация,

В случае отсутствия ощибок в запращи- ваемой комбинации при повторении на выходе сравнивателя 5 после приема каждой комбинации образуются соответствующие сигналы, по которым при помощи управляющего блока 3 повторяемые комбинации записываются на вход выходного накопителя 8 непосредственно с выхода промежуточного накопителя 11 или с выхода первого блока памяти 9,

В случае приема комбинации с ощибкой при первом и повторном приемах ее запра- щивают вновь, В этом случае цикл блокировки начинается сначала.

В случае обнаружения ошибки в запращиваемой комбинации при повторении выход накопителя 8 блокируется вновь. При этом на выходе сравнивателя признаков 5 после приема каждой комбинации будет образован соответствующий сигнал, в соответствии с которым при помощи управляющего блока 3 элементы повторяемой комбинадии записываются во втором блоке памяти 10, стираются, записываются в первом блоке памяти 9 вместо записанных там при первом приеме элементов соответствукядей комбинации. В последнем случае в блок для запоминания признаков 6 записывает5ся признак О вместо записанного там признака i. При приеме запрашиваемой комбинации в третий раз независимо от наличия или отсутствия ошибок регистр 2 запускается третий раз подряд сигналом с выхода управляюшего блока 3, но блокировка выхода накопителя 8 не производится. При этом на выходе сравнивателя 5 образуются сигналы, в соответствии с которыми комбинация, принятая без ошибки хотя бы один раз из трех, выдается на вход накопителя 8 или непосредственно с выхода промежуточного накопителя 11 или с выхода первого блока памяти 9. В случае приема комбинации с ошибкой все три раза элементы этой комбинации с выходов промежуточного накопителя 11 и обоих блоков памяти 9 и 1О подаются на входы блока 12 для мажоритарного сложения, где путем поэлемен ного мажоритарного сложения их формируется новая комбинация, которая подается на вход дополнительного декодируюшего бло ка 7, и в случае отсутствия ошибок в ней она поступает на вход выходного накопител 8, в случае же обнаружения ошибки в ней комбинация запрашивается вновь, и весь цикл блокировки начинается сначала.

Формула изобретения Устройство для приема дискретной информации, содержащее основной декодируюший блок, выход которого соединен с входом регистра для блокировки, и первый и второй блоки памяти, информационные входы и выходы которых соединены соответственно

Источники информации, принятые во внимание при экспертизе;

1.Патент США № 3760354, кл. 340-146.1, опубл. 1973.

2.Авторское свидетельство СССР № 330561, 04 L 1/10, 29.01.70 (прототип). 3 через блок для мажоритарного сложения с входом дополнительного декодируюшего блока к входом выходного накопителя, другие входы которого подключены к информационным входам блоков памяти и выходу первого блока памяти соответственно, о т л и- чаюшееся тем, что, с целью увеличения скорости передачи информации, введены управляющий блок, делитель на три, сравниватель признаков, промежуточный накопи тель и блок для запоминания признаков, при этом входы управляюшего блока соединены соответственно с выходом регистра для блокировки непосредственно, а также через делитель на три, и с выходом сравнивателя признаков, входы которого соединены с выходом основного декодирующего блока непосредственно и через блок для запоминания признаков, а выходы управляющего блока подключены соответственно к входу регистра блокировки, другой вход которого соединен с выходом дополнительного декодирующего блока, и к входам делителя на три, выходного накопителя, сравнивателей и блоков для запоминания признаков и первого и второго блоков памяти, информационные входы которых через промежуточный накопитель соединены с входом основного декодирующего блока.

От регистрирующего устройства

И //

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для приема дискретной информации, закодированной корректирующим кодом | 1978 |

|

SU680189A1 |

| Устройство для приема дискретной информации | 1979 |

|

SU873435A1 |

| Устройство анализа кодовых комбинаций | 1976 |

|

SU649152A1 |

| Устройство для приема дискретной информации, закодированной корректирующим кодом | 1987 |

|

SU1462492A1 |

| Устройство для приема дискретной информации,закодированной корректирующим кодом | 1983 |

|

SU1099397A2 |

| Устройство для приема дискретной информации | 1980 |

|

SU907845A2 |

| Устройство для приема дискретной информации, закодированной корректирующим кодом | 1988 |

|

SU1596464A1 |

| Устройство для приема дискретной информации,закодированной корректирующим кодом | 1984 |

|

SU1172022A2 |

| "Устройство для исправления ошибок в системах передачи дискретной информации | 1977 |

|

SU663120A1 |

| Устройство приема многократно передаваемых комбинаций | 1979 |

|

SU866763A1 |

г5

Авторы

Даты

1976-10-05—Публикация

1974-11-10—Подача