(54) УСТРОЙСТВО ДЛЯ ПРИЕМА ДИСКРЕТНОЙ ИНФОРМАЦИИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для приема дискретной информации, закодированной корректирующим кодом | 1987 |

|

SU1462492A1 |

| Устройство анализа кодовых комбинаций | 1976 |

|

SU649152A1 |

| Устройство для приема дискретной информации,закодированной корректирующим кодом | 1983 |

|

SU1099397A2 |

| Устройство для приема дискретной информации, закодированной корректирующим кодом | 1988 |

|

SU1596464A1 |

| Устройство для приема дискретной информации | 1974 |

|

SU531293A1 |

| Устройство для приема дискретной информации, закодированной корректирующим кодом | 1978 |

|

SU680189A1 |

| Устройство для приема дискретной информации, закодированной корректирующим кодом | 1988 |

|

SU1601754A1 |

| АДАПТИВНЫЙ ДЕКОДЕР | 2008 |

|

RU2379833C1 |

| Адаптивное устройство для приема избыточной информации | 1981 |

|

SU1001145A1 |

| Устройство для приема дискретной информации,закодированной корректирующим кодом | 1984 |

|

SU1172022A2 |

I

Изобретение относится к технике передачи данных и может использоваться в аппаратуре передачи дискретной информации с решающей обратной связью.

Известно устройство для приема дискретной информации, содержащее блок управления, первый выход которого соединен с одними входами первого, второго и третьего блоков памяти и первым входом блока сравнения, ко второму входу которого подключен выход первого блока памяти, другой вход которого соединен с первым выходом основкого декодирующего блока и с входом блока сравнения, выход которого подключен к первому входу блока управления второй выход которого соединен с первым входом регистра, одним входом делителя и первым входом выходного блока памяти, вт(ой вход которого соединен с выходом решающего блока и входом дополнительного декодирующего блока, выход которого подключен ко второму входу регистра, выхоД которого соединен со вторым входом блока управления и с другим входом делителя, выход которого подключен к третьему блока управления, причем другие входы второго и третьего блоков памяти соединены

С выходом промежуточного блока памяти, вход которого соединен со входом основного декодирующего блока, второй выход которого подключен к третьему входу регистра 1 .

Однако в известном устройстве верность Приема мала.

Цель изобретения - повышение верности приема.

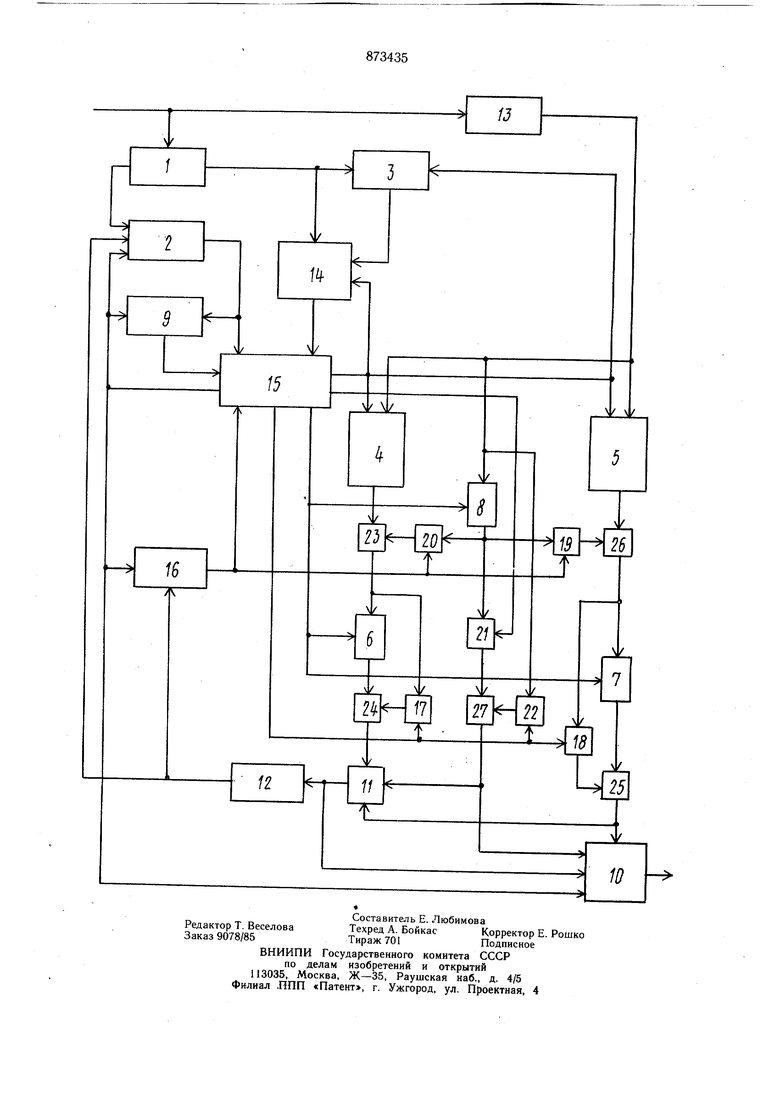

Цель достигается тем, что в устройство для приема дискретной информации введены четвертый, пятый и шестой блоки памяти, счетчик, шесть ключей и пять элементов ИЛИ, при этом выход первого элемента ИЛИ соединен с первым входом первого ключа и с первым входом четвертого блока памяти, выход которого подключен к первому входу второго элемента ИЛИ, выход которого соединен с первым входом решающего блока, второй вход которого соединен с третьим входом выходного блока памяти и выходом третьего элемента ИЛИ, к первому входу которого подключен выход пятого блока памяти, первый вход которого соединен с первым входом второго ключа и с выходом четвертого элемента ИЛИ, к первому входу которого подключен выход третьего ключа, первый вход которого соединен с первыми входами четвертого и пятого ключей и с выходом шестого блока памяти, первый вход которого соединен со вторыми входами четвертого и пятого блоков памяти и с третьим выходом блока управления, четвёртый выход которого подключен ко второму входу пятого ключа, выход которого соединен с первым входом пятого элемента ИЛИ, второй вход которого соединен с выходом шестого ключа, первый вход которого соединен со вторыми входами первого и второго ключей и с пятым выходом блока управления, четвертый вход которого соединен со вторыми входами третьего и четвертого ключей и выходом счетчика, первый и второй входы которого соединены соответственно с первым и вторым входами регистра, причем выход четвертого ключа подключен к первому входу первого элемента ИЛИ, второй вход которого соединен с выходом второго блока памяти, другой вход которого соединен со вторым входом шестого блока памяти и с вторым входом шестого ключа, выход третьего блока памяти подключен ко второму входу четвертого элемента ИЛИ, а вторые входы второго и третьего элементов ИЛИ соединены с выходами соответственно первого и второго ключей. На чертеже представлена структурная электрическая схема предложенного устройства. Устройство для прие.ма дискретной информации содержит основной декодирующий блок 1, регистр 2, первый-шестой блоки.З- 8 памяти соответственно, делитель 9, выходной блок ГО памяти, решающий блок 11, дополнительный декодирующий блок 12, промежуточный блок 13 памяти, блок 14 сравнения, блок 15 управления, счетчик 16, шесть ключей 17-22 и пять элементов ИЛИ 23-27. Устройство работает следуюш,им образом. На входы промежуточного блока 13 и ОСНОВНОГО декодирующего блока 1 поэлементно поступают П-элементные кодовые комбинации. В случае отсутствия или необнаружения ошибок принятые комбинации с выхода промежуточного блока 13 поэлементно поступают на вход выходного блока 10 через шестой ключ 22 и пятый элемент ИЛИ 27. С выхода выходного блока 10 в случае необнаружения ошибок в следующей кодовой комбинации информационные элементы поступают на регистрирующее устройство (на чертеже не показано). При обнаружении в принятой комбинации ошибки сигналом с выхода основного декодирующего блока 1 запускается регистр 2, а сигналом с выхода блока 15 осуществляется блокировка выхода выходного блока 10. При этом элементы комбинации, предшествующей ощибочной, записанные в выходном блоке 10, стираются сигналом с выхода блока 15, открываются информационный вход третьего блока 5 и вход первого блока 3, элементы принятой с ошибкой и следующих за ней комбинаций записываются в третьем блоке 5, а их признаки - в первом блоке 3, причем комбинациям, принятым без ошибки, присваивается признак «О, а принятым с ошибкой - признак «1. При повторном приеме запрашиваемой комбинации регистр 2 сигналом с выхода блока 15 запускается вновь независимо от того с ошибкой или без ошибки принимается эта комбинация. В случае отсутствия ошибок в запрашиваемой комбинации при повторении йа выходе блока 14 после приема каждой комбинации образуются соответствующие сигналы, по которым при помощи блока 15 повторяемые комбинации записываются на вход выходного блока 10 с выхода промежуточного блока 13 через шестой ключ 22 и пятый элемент ИЛИ 27 или с выхода третьего блока 5 через четвертый элемент ИЛИ 26, второй ключ 18 и третий элемент ИЛИ 25. В случае приема комбинации с ошибкой при первом и повторном приемах ее запрашивают вновь. В этом случае цикл блокировки начинается сначала. В случае обнаружения ошибки в запрашиваемой комбинации при повторении выход выходного блока 10 блокируется вновь. При этом на выходе блока 14 после приема каждой комбинации образуется соответствующий сигнал, в соответствии с которым при помощи блока 15 элементы повторяемой комбинации, записанные во втором блоке 4, стираются и записываются в третьем блоке 5 вместо записанных там при первом приеме элементов соответствующей комбинации. В последнем случае в первом блоке 3 записывается признак «О вместо записанного там признака «1. При приеме запрашиваемой комбинации в третий раз независимо от наличия или отсутствия ошибок регистр 2 запускается третий раз подряд сигналом с выхода блока 15, но блокировка выхода выходного блока 10 не производится. В случае приема комбинации с ошибкой все три раза элементы этой комбинации с выхода промежуточного блока 13 через шестой ключ 22 и пятый элемент ИЛИ 27, с выхода второго блока 4 через первый элемент ИЛИ 23, первый ключ 17, второй элемент ИЛИ 24, с выхода третьего блока 5 через четвертый элемент ИЛИ 26, ключ 18, третий элемент ИЛИ 25 поступают на соответствующие входы решающего блока 11 и одновременно записываются в четвертый, пятый и шестой блоки 6-8 соответственно. Если после поэлементного мажоритарного сложения новая сформированная комбинация, которая подается на вход дополнительного декодирующего блока 12, не содержит ошибок, то она поступает на вход выходного блока 10, при этом элементы комбинации стираются с блоков . Если после мажоритарного сложения новая комбинация содержит ошибки, то она запрашивается в четвертый раз. В случае обнаружения ошибки во вновь сформированной комбинации она запрашивается в пятый раз. Если во вновь сформированной комбинации после ее поэлементного мажоритарного сложения вновь обнаружена ошибка, то перезапись принятой комбинации осуществляется так же как и при приеме запрашиваемой комбинации в четвертый раз. В случае необнаружения ошибки в сформированной комбинации после мажоритар. ного сложения, ее информационные элементы через выходной блок 10 поступают к получателю, а элементы комбинации, записанные в четвертом, пятом и шестом блоках 6-8 стираются сигналом, поступающим с блока 8. Каждый раз при приеме запрашиваемой комбинации с ошибкой следующие за ней комбинации, которые не искажены, поступают в третий блок 5 памяти в соответствии с сигналами, поступающими с блока 14 через блок 8. Использование предложенного устройства уменьшает средний риск приема комбинации с ощибкой, вследствие чего уменьшается среднее число переспросов и вероятность задержки сообщения, а это позволяет увеличить скорость передачи информации. Формула изобретения Устройство для приема дискретной информации, содержащее блок управления, первый выход которого соединен с одними входами первого, второго и третьего блоков памяти и первым входом блока сравнения, ко второму входу которого подключен выход первого блока памяти, другой вход которого соединен с первым выходом основного декодирующего блока и с третьим входом блока сравнения, выход которого подключен к первому входу блока управления, второй выход которого соединен с первым входом, регистра, одним входом делителя и первым входом выходного блока памяти, второй вход которого соединен с выходом решающего блока и входом дополнительного декодирующего блока, выход которого подключен ко второму входу регистра, выход которого соединен со вторым входом блока управления и с другим входом делителя, выход которого подключен к третьему входу блока управления, причем другие входы второго и третьего блоков памяти соединены с выходом промежуточного блока памяти, вход которого соединен с входом, основного декодирующего блока, второй выход которого подключен к третьему входу регистра, отличающееся тем, что, с целью повышения верности приема, введены четвертый, пятый и шестой блоки памяти, счетчик, шесть ключей и пять элементов ИЛИ, при этом выход первого элемента ИЛИ соединен с первым входом первого ключа и с первым входом четвертого блока памяти, выход которого подключен к первому входу второго элемента ИЛИ, выход которого соединен с первым входом решающего блока, второй вход которого соединен с третьим входом выходного блока памяти и выходом третьего элемента ИЛИ к первому входу которого подключен выход пятого блока памяти, первый вход которого соединен с первым входом второго ключа и с выходом четвертого элемента ИЛИ, к первому входу которого подключен выход третьего ключа, первый вход которого соединен с первыми входами четвертого и пятого ключей и с выходом шестого блока памяти, первый вход которого соединен со вторыми входами четвертого и пятого блоков памяти и с третьим выходом блока управления, четвертый выход которого подключен ко второму входу пятого ключа, выход которого соединен с первым входом пятого элемента ИЛИ, второй вход которого соединен с выходом щестого ключа, первый вход которого соединен со вторыми входами первого и второго ключей и с пятым .выходом блока управления, четвертый вход котррого соединен со вторыми входами третьего и четвертого ключей и выходом счетчика, первый и второй входыкоторого соединены соответственно с первым и вторым входами регистра, причем выход четвертого ключа подключен к первому входу первого элемента ИЛИ, второй вход которого соединен с выходом второго блока памяти, другой вход которого соединен с вторым входом шестого блока памяти и с вторым входом Шестого ключа, выход третьего блока памяти подключен ко второму входу четвертого элемента ИЛИ, а вторые входы второго и третьего элементов ИЛИ соединены с выходами соответственно первого и второго ключей. Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР № 531293, кл. Н 04 L 1/10, 1974 (прототип).

Авторы

Даты

1981-10-15—Публикация

1979-10-09—Подача