Фиг.

vfrWWWe

Изобретение относится к автоматике и вычислительной технике и может быть использовано в преобразующих устройствах специализированных вычислительных машин, оперирующих в двоичной системе счисления и вьщающих результат обработки в десятичной системе.

Цель изобретения - повышение надежности работы преобразователя.

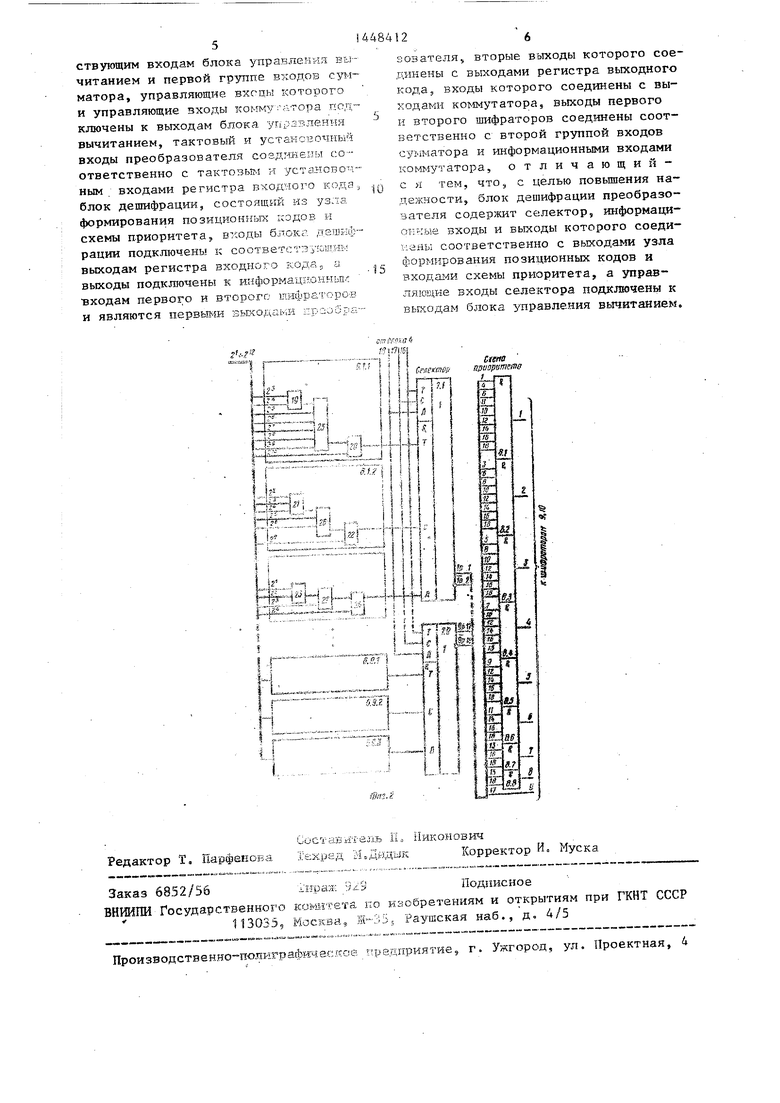

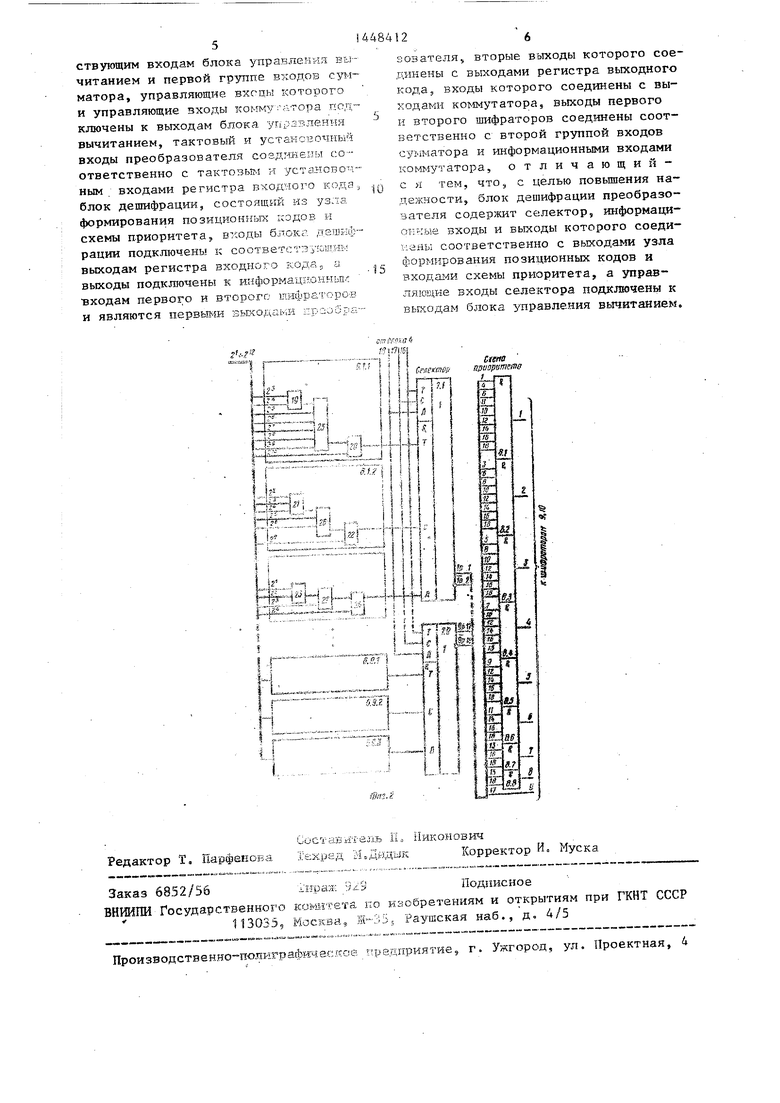

На фиг. i приведена блок-схема предлагаемого преобразователя; на фиг. 2 - функциональная схема блока дешифрации с примером исполнения npeобразователей 1-го разряда тетрад десятков, сотен и тысяч, селектора и схемы приоритета.

Преобразователь (фиг. 1) содержит регистры входного 1 и выходн.ого 2 кодов, сумматор 3, блок 4 управления вычитанием, блок 5 дешифрации, состоящий из узла 6 формирования позиционных кодов, селектора 7 и схемы 8 приоритета, первый и второй шифраторы 9 и 10 и коммутатор 11. На фиг. 1 обозначены информационные 12 и тактовые 13 входы, выходы 14 и 15 преобразователя для выдачи соответствен0

S

0 5

разряда) к младшему (1-му разряду) и вьвделяет только старший позиционный разряд любой тетрады, Шифратор 9 преобразует последовательный десятичный код с учетом сигналов признака тетрады в параллельный двоичный код для формирования двоичного кода числа любой тетрады. Коммутатор 11 предназначен для формирования двоичного кода любой тетрады.

Назначение, схемное решение блока 4 и принцип его работы, а также шифраторов 9 и 10 и коммутатора 11 аналогичны известным. Блок 4 управления вычитанием служит для анализа всех разрядных входов информационного .кода преобразователя, поступающих от регистра 1. Условие ф ормирования сигналов признаков тысяч, сотен и десятков на выходах 16-18 блока 4 управления вычитанием следующее:

Выход ,242 42 -1-2 -2 2 х «2«.(

+2)

Вькод ,t2 +2в+2 +2 -2(2Н2 -1Выход ,f Л2 +2 +2 +2 +2 )

Блок 5 дешифратора служит для

(24

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь двоичного кода в двоично-десятичный | 1985 |

|

SU1330762A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1978 |

|

SU864278A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1985 |

|

SU1283979A1 |

| Преобразователь двоично-десятичных чисел в двоичные | 1981 |

|

SU1003068A1 |

| Реверсивный преобразователь двоичного кода в двоично-десятичный | 1974 |

|

SU620975A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1985 |

|

SU1300640A1 |

| Преобразователь последовательного двоичного кода в параллельный двоично-десятичный код | 1982 |

|

SU1084780A1 |

| Преобразователь двоичного кода вдВОичНО-дЕСяТичНый КОд | 1979 |

|

SU849199A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1977 |

|

SU690474A1 |

| Преобразователь двоичного кода | 1984 |

|

SU1208607A1 |

Изобретение относится к вычислительной технике,-к устройствам преобразования кодов. Цель изобретения - повьшение надежности работы преобразователя за с-чет введения в блок 5 дешифрации селектора 7, управляемого сигналами признака тетрады. Это позволяет надежно формировать нужный позиционный код любой тетрады. В состав преобразователя входят регистр 1 входного кода для временного хранения входного числа, сумматор 3 для вычитания числа тетрады из преобразуемого числа, блок 4 управления вычи танием для формирования сигналов признака тетрады, шифратор 9 для формирования двоичного кода тетрады, ком- 1-{утатор 1 Н регистр выходного кода для записи и временного хранения двоично-десятичного кода преобразуемого числа. Принцип работы преобразователя основан на выделении из преобразуемого числа в блоке дешифрации позиционного кода, эквивалентного числу старшей тетрады, преобразовании этого кода в двоичн -лй код числа тетрады и вычитания этого кода в комбинационном сумматоре 3 из преобразуемого числа и занесении результатов вычитания во входной регистр 1 для дальнейшего преобразования. В шифраторе 10 пози- ционньш код тетрады преобразуется в дво -ганый код тетрады, который через коммутатор 11 поступает в выходной регистр 2 для временного хранения. Последующие циклы формирования послед: тощих тетрад осу1дествляются аналогично по ка:-кдому импульсу тактовой частоты. Преобразование продолжается до тех пор. пока результат вычитания станет меньше десяти, 2 ил. to

но двоично-дейятичного кода и единич-30 формирования единичного позиционного

ного позиционного кода тетрады, а также выходы 16-18 блока 4 управления вычитанием, эле|менты ИЛИ 19-24 и элементы И 25-27.

Регистр 1 предназначен для хране- 35 ния преобразуемого входного числа и результата вычитания сумматора. Регистр 2 предназначен для временного хранения выходного двоично-десят.ич- ного числа. Сумматор 3 предназначен 40 для получения разности между преобразуемым двоичным числом, поступающим от регистра 1, и двоичным числом тетрады, формируемым в шифраторе 9 числа тетрады. Блок 4 управления вычитанием з предназначен для формирования сигналов признака тетрады (тысяч, сотен, десятков). Блок 5 дешифрации предназначен для формирования позиционного десятичного кода тетрады с учетом д сигналов признака тетрады. Узел 6 формирования позиционных кодов осуществляет формирование возможных позиционных кодов тетрады тысяч, сотен и десятков. Селектор 7 разрешает про-ее выход тре гьего разряда

1 А ilT it I fl It n (Л г m О

хождение на его выход позиционных кодов, принадлежащих только одной тетраде. Схема В приоритета устанавливает приоритет от старшего (9-го

кода, разряды которого соответствии со следую выход девятого (старше Ц,С 2 - ( (242)J ; выход восьмого разряда

Ц if,T 2«-2 (2 +2 +2)+Д выход седьмого разряда

} i/,U T-2 2 2 + +2 +2)- -С-2П2 +2Ч2 ()) ; выход шестого разряда

if 4 У, +2 2 -2 : -С-2 Г2 2 ( Ч2 -+2 -2 - ) ;

выход пятого разряда .4.5 1, Ц1.(з Ч1Т-2 )+СГ2 н-2 2 +2)+Д-2 (2 +2 +2 выход четвертого разря

1|) /,/ji/jgr L/s ) +С-2 -

+2Mi;

l(, Ср, i/5,(7jV4i 5 jT 2 «2 (2 +2 - 2-) +С-2.t

) +Д(2 +2 -2 2 выход второго разряда

выход тре гьего разряда

кода, разряды которого формируются в соответствии со следующими условиями: выход девятого (старшего) разряда Ц,С 2 - () (242)J ; выход восьмого разряда

Ц if,T 2«-2 242-1-2) + (2 +2 +2)+Д 2. выход седьмого разряда

} i/,U T-2 2 2 +2--2 Ч2 - -2 / 2% +2 +2)- -С-2П2 +2Ч2 +2 2 -2) + ()) ; выход шестого разряда

if 4 У, +2 (2 + +2 2 -2 : -С-2 Г2 2 ( 2 Ч2 -+2 -2 - ) ;

выход тре гьего разряда

выход пятого разряда .4.5 1, Ц1.(з Ч1Т-2 242 - - )+СГ2 н-2 2 2 +2)+Д-2 (2 +2 +2 )} ; выход четвертого разряда

1|) /,/ji/jgr L/s -t-2 -2 ) +С-2 - )+Д-2 (2

+2Mi;

выход тре гьего разряда

1 А ilT it I fl It n (Л г m О

l(, Ср, i/5,(7jV4i 5 jT 2 2 2 «2 (2 +2 - 2-) +С-2.t +

) +Д(2 +2 -2 2 выход второго разряда

2 }

3IA48

Ц , г э 4 s 6 2 42 2 2« ,2 . 2() ) +fl-2f ()1;1

выход первого (младшего) разряда

/, Ч 1if4 3 4 5 Л7 ИтC2 « 29 2 .2 (2Ч2)+СГ2 +2« 2 5. ( +ДГ2П2. (2%2 )} ,

где Т, С, Д - приэяаки тетрады тысяч, сотен и десятков соответственно; ю

с 2 по 2 - разрядные входы информационного числа.

Первый шифратор 9 работает следующим образом.

На его управляющие входы с is первого по третий поступают сигналы от блока 4, а на информационные входы с первого по девятый поступают сигналы ifg- if с блока 5. При этом при появлении на информационных вхо- 20 дах шифратора 9 единицы, например, в первом разряде i/ и единицы в первом разряде fJ на управляющих входах на выходе шифратора 9 формируется двоичный код числа тетрады с наличием еди- ницы в разрядах 2 и 2 что соответствует числу 10. Если поступят сигна-г лы t/o и f , то выходной код числа тетрады будет принимать значение 1 в разрядах 2 , 2 и 2, что соответ- ствует числу 100. Если поступят сигналы cf „ и f, то сформируется число 1000, т.е. на выходе будут 1 в разрядах 2 и с 2 по 2.

Преобразователь двоичного кода в двоично-десятичный работает следующим образом.

В исходном состоянии в регистр 1 записано с входов 12 преобразуемое число, регистр 2 установлен в исход- ное нулевое состояние. Число, записанное в регистр 1, анализируется в блоке 4 управления вычитанием. Если анализируемое число содержит тысячи то появляется сигнал признака тысяч на выходе 16 блока 4; если число не содержит тысяч, а содержит сотни, то появляется сигнал признака сотен на выходе 17 блока 4, а если оно содержит только десятки, то по- является сигнал признака десяток на выходе 18 блока 4. Одновременно осуществляется анализ разрядов двоичного -кода в блоке 5 дешифрации (фиг. I, фиг. 2), в котором формиру- ется единичный позиционный код тетрады с учетом сигналов признака тетрад, поступающих от блока 4. Этот код поступает на выходы 15 преобразователя

12 ;4

и на входы шифраторов 9 и 10. В шифраторе 9 с учетом сигналов признака тетрады, поступающих на его управляющие входы от блока 4, формируется двоичный код числа тетрады. Этот код поступает на вторые входы сумматора 3, где вычитается из числа, поступающего на его первые входы от регистра 1 .

При поступлении импульса тактовой частоты с входа 13 на тактовый вход регист: 1 результат вычитания из сумматора 3 заносится в регистр 1 для дальнейшего преобразования. Операция вычитания повторяется с приходом каждого импульса тактовой частоты и осуществляется до тех пор, пока число в регистре 1 не станет меньше десяти Десятичный код тетрады с выхода блока 5 преобразуется в двоичный код тетрады в шифраторе 10. Этот код тетрады через коммутатор 11, управляемый сигналами признака тетрады, которые поступают от блока 4 управления вычитанием и синхронизируемый импульсами тактовой частоты, которые поступают со входа 13 преобразователя, поступает на соответствующие входы регистра 2 для временного хранения. По каждому импульсу тактовой частоты в регистр 2 заносится одна тетрада двоично-десятичного числа. Двоичный код тетрады единиц формируется в регистре 1. Так, , число 6789 преобразуется за 3 такта, причем в первом такте формируется двоичйый код 6 (0110) и сигнал признака тысячи , который коммутирует этот код на входы регистра 2 в тетраду тысяч. Во втором такте формируется двоичный код числа 7 (0111) и призна сотен, которьй коммутирует зтот код в тетраду сотен регистра 2. По третьему такту формируется двоичный код числа 8 (1000) и сигнал признака десяток. Этот код поступает в регистр 2 в тетраду десятков. Двоичный код единиц, равный 9 (1001), формируется в регистре 1 по третьему такту.

Формула изобретения

Преобразователь двоичного кода в двоично-десятичный, содержащий регис входного кода, информационные входы которого соединены с выходами сумматора, а выходы подключены к соответ5

ствующим входам блока управления вычитанием и первой группе входов сумматора, управляющие входы которого и управляющие входы коммугатора подключены к выходам блока уггрззления вычитанием, тактовый и устаисвочиыч входы преобразователя соедгжеиы соответственно с тактозы. и уст ал ОБ очным . входами регистра входного кода блок дешифрации, состоящий из ysJia формирования позицион1 ьш кодов и схемы приоритета, в:юды блокг дешифрации подключены к соответстз -юшиг выходам регистра входного кода, а выходы подключены к информационньп.; входам первого и второго шифраторов и являются первыми зьЕ одаки праэбра

0

5

зователя, вторые выходы которого соединены с выходами регистра выходного кода, входы которого соединены с выходами коммутатора, выходы первого и второго шифраторов соединены соответственно с второй группой входов cs wMaTopa и информационными входами коммутатора, отличающий- с я тем, что, с целью повьшения надежности, блок дешифрации преобразо- зателя содержит селектор, информаци- отп%ые входы и выходы которого соеди- иаяы соответственно с выходами узла формирования позиционных кодов и входа1- 5и схемы приоритета, а управляющие входы селектора подключены к выходам блока управления вычитанием.

| -Авторское свидетельство-СССР № 1198756, кл, Н 03 М 7/00,1985 | |||

| Преобразователь двоичного кода в двоично-десятичный | 1985 |

|

SU1330762A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1988-12-30—Публикация

1987-05-04—Подача