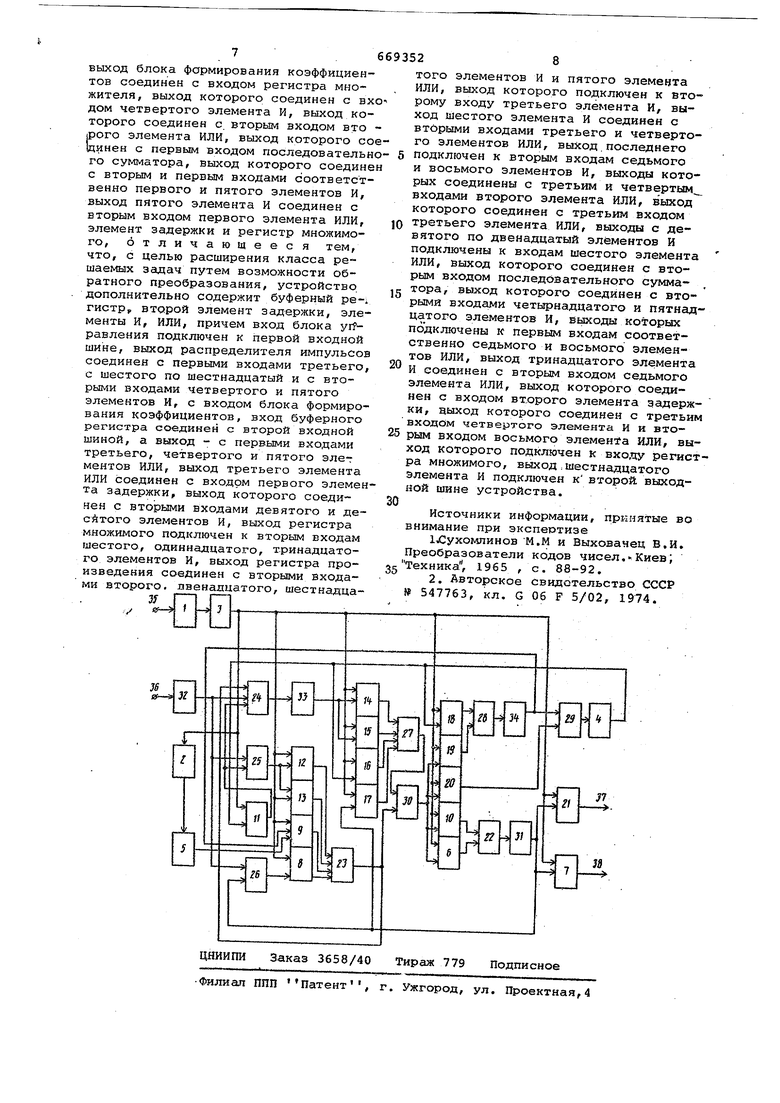

Изобретение относится к вычисли;тельной технике и может использоват ся в автоматизированньк системах уп равления, информационных системах. Известно устройство для преобразования двоично-десятичных чисел в двоичные и обратнр/ содержащее дина мический регистр, восемь триггеров, сумматор, пять элементов И и инвертор 1 . Недостатком устройства является отсутствие коррекции, необходимость которой появляется из-за возникновения ошибки при преобразовании десятичных дробных чисел методом умно жения на 1010. Существенным недостатком также является и наличие дин мического регистра на магнитном барабане или магнятострикционныХ линиях задержки. Наиболее близкое к. предлагаемому изобретению устройство для преобразования двоичного кода в двоично-де сятичный содержит блок управления, выход которого соединен с входом распределителя импульсов, выход которого подключен к первым входам пер вого и второго элементов И, выход второго элемента И соединен с первой выходной шиной устройства, выход пер вого элемента И соединен с первым входом первого элемента ИЛИ, выход которого соединен с входом регистра произведения, выход третьего элемента И соединен с входом второго элемента ИЛИ, выход блока формирования коэффициентов соединен с входом регистра множителя, выход которого соединен с входом четвертого элемента И, выход которого соединен с вторым входом второго элемента ИЛИ, выход которого соединен с первым входом последовательного сумматора, выход которого соединен с вторым и первым входами соответственно первого и пятого элементов И, выход пятого элемента И соединен с вторым входом первого элемента ИЛИ, элемент защержки и регистр множимого 2. Недостаток такого устройства невозможность обратного преобразования. Цель изобретения - расширение класса решаемых задач путем возможности обратного преобразования. Это достигается тем, что устройство дополнительно содержит буферный регистр, второй элемент задержки, элементы И, ИЛИ, причем вход блока управления подключен к первой входной шине, выход распределителя импульсов соединен с первыми входами третьего, с шестого по шестнадцатый и с вторыми входами четвертого и пят го элементов И, с. входом блока формирования коэффициентов, вход буфер|ного регистра соединен с второй вход ной шиной, а выход - с первыми входа ми третьего, четвертого и пятого эле ментов ИЛИ, выход третьего элемента ИЛИ соединен с входом первого элемента задержки, выход которого соединен с вторыми входами девятого и десятого элементов И, выход регистра множимого подключен к вторым входам шестого, одиннадцатого, тринадцатого элементов И, выход регистра Произведения соединен с вторьпуш входами второго, двенадцатого шестнадцатого элементов И и пятого элемента ИЛИ, выход которого подключен к вторс лу входу третьего элемента И, выход шестого элемента И соединен с вторыми входами третьего и четвертого элементов ИЛИ, выход последнего подключен к вторым входам седьмого и восьмого элементов И, выходы которых соединены с третьим и четвертым входами второго элемента ИЛИ, выход которого соединен с третьим входом третьего элемента ИЛИ, выходы с девятого по двенадцатый элементов И подключены к входам шестого элемента ИЛИ, выход которого соединен с вторым входом последовательного сумматора, выход которо го соединен с вторыми входами четырнадцатого и пятнадцатого элементов И, выходы которых подключены к первым входам соответственно седьмого и элементов ИЛИ, выход три надцатого элемента И соединен с вторым входом седьмого элемента ИЛИ выхОд которого соединен с входом вт рого элемента задержки, выход которого соединен с третьим входом четвертого элемента И и вторым входом восьмого элемента ИЛИ, выход которо го подключен к входу регистра множимого, выход шестнадцатого элемента И подключен к второй выходной шине устройства. На чертеже дана Функциональная схема 1редлагаемрго устройства для преобразования двоичного кода в дво но- дес ятичный , Устройство содержит блок 1 управ ления, блок 2 формирования коэффици тов, распределитель 3 импульсов, ре гистр 4 множимого, регистр 5 множителя, элементы И 6-21, элементы ИЛИ 22-29, последовательный сумматор 30 регистр 31 произведения, буферный регистр 32, первый и второй элементы 33 и 34 задержки, первую и втору входные шины 35 и 36, и вторую выходные шины 37 и 38 устройств Математическое обеспечение работ следующее. Информация представляетя в виде двоично-десятичных дробей в устройстве преобразуется методом оследовательной обработки цифр пребразуемого числа, который представяется алгоритмом (a a -iH °m-2H - zjl- « де N - преобразуемое число; m - число разрядов преобразуемого числа; а - основание системы счисления преобразуемого числа; а - коэффициент разряда преобразуемого числа. звестно, что данный способ преобраания пригоден для обработки цеых чисел, поэтому в данном случае еоб содимо вводить коррекцию, .которая водится к умножению полученного в езультате преобразования числа на оправочный коэффициент К К 2 Ю . реобразование двоичного кода в двочно-десятичный в режиме вывода инфорации осуществляется по алгоритму 1е-1, ttz-«o) -«е , . %и,,- OlOiO,; Y Ф(хг 5 I 1, 2,3 ... m де n - количество разрядов числа в двоичной системе счисления;t - показатель разряда; го - целое положительное число, определяющее количество разрядов десятичной системы счисления; У2 - исходный двоичный код числа; Ф1- двоичный остаток; Bg- получаемые тетради в двоично-десятичной системе счисления. Устройство работает следующим образом. Оно выполняет две функции - функцию преобразования двоично-десятичного кода в двоичный Хввод информации) и функцию преобразования двоичного кода в двоично-десятичный (вывод информации). В первом случае необходимо в соответствии с формулой 1) старшую 2-10 тетраду вводимого числа умножить на 1010, затем сложить полученный результат с очередной 2-10 тетрадой. Образовавшуюся сумму вновь умножить на 1010 и т.д. Всего нужно выполнить (т-1) чepeлsющиxcя операций умножения и сложения, Иа вход блока 1 управления поступает сигнс1Л ввода, по которому в распределителе 3 импульсов вырабатываются последовательно сигналы 1 - умножение, 2 - сложение, К - умножение на корректирующий коэффициент К, по которому подготавливается в блоке формирования коэффициентов нужный коэффи циент и вносится в регистр 5 множите ля. Входная информация, вносимая в буферный регистр 32 в виде тетрад 2-10 числа/поступает через элемен ты ИЛИ 24, задержки 33, И 15, ИГИ 2 на первый вход последовательного сум матора 30, а через элементы ИЛИ 25, И 12, ИЛИ 23 на второй вход последо вательного сумматора. Полученная сумма с выхода сумматора через элементы И 19, ИЛИ 28, элемент 34 задержки, ИЛИ 29 вн: сится в регистр 4 множимого. Затем вырабатывается сиг нал 2 (сложение), по этому сигналу содержимое регистра 4 множимого поступает через элементы И 16, ИЛИ 27 на первый вход сумматора 30, а очередная тетрада с буферного регистра 32 через элементы ИЛИ 25, И 13, ИЛИ 23 поступает на второй вход сумматор 30, полученная сумма через элементы И 20, ИЛИ 29 вновь записывается в регистр 4 множимого. Затем вновь вырабатывается сигнал 1 - умножение и содержимое регистра множимого поступает вновь на элементы И 11, ИЛИ 24 и ИЛИ 25 и т.д., т.е. содержимое регистра множимого умножается на 1010 Затем по сигналу Сложение умноженное на 1010 число сложится со следующей тетрадой. В-схеме произво дится (т-1) операция умножения и (т-1) операция сложения, где m порядок десятичного числа. В результате в регистре 4 множимого образова ся двоичный нескорректированный код вводимого числа. Для выполнения коррекции вырабатывается сигнал К, по которс 4у выполняется умножение множимого, хранимого в регистре 4 множимого, на множитель, поправочный коэффициент , содержащийся в регистре 5 множителя. Младший разряд множителя подготавливает элемент И 9, т.е. если его значение равно , то элемент И 9 будет пропускать множимое разряд за разрядом, которое следует с выхода регистра 4 через элементы И 18, ИЛИ 28, задержки 34, И 9, ИЛИ 23 на второй вход сумлатора. Полученное частичное произведение с выхода сумматора вносится через элемен ты И 10, ИЛИ 22 в регистр 31 произве дения. Во втором цикле образуется второе частичное произведение, которое склсщывается с первым частичным произведением, поступаквдим с выхода рег стра 31 произведения Через элементы И 17, ИЛИ 27 на первый вход сумматора 30. Всего I образуется П частичных: произведений, где П - число разрядов множителя i В результате этой операции в реги ре 31 произведения образуется скорректированное двоичное число, которо 526 поступает через элемент И 21 при наличии соответствующего потенциала на первую вчходную шину 37 устройства. При выводе информации из центрального процессора устройство работает в соответствии с алгоритмом (2), по которому преобразуемое двоичное число нужно умножить на 0,1010, отделить от полученного произведения четыре старших разряда, которые будут представлять первую двоично-десятичную тетраду. Затем полученный остаток вновь умно/ить на 0,1010 и опять отделить тетраду и т.д. Блок I управления по сигналу Печать, поступающему из центральной схемы управления, вырабатывает необходиПреобтэамне управляющие сигналы зование, которые осуществляют управление работой устройства. Информация в двоичном коде вносится в буферный регистр, освобождая таким образом центральный процессор для выполнения других операций. Из буферного регистра двоичный код через элементы ИЛИ 26, И 8, ИЛИ 23 поступает на второй вход сумматора, а через ИЛИ 24, элемент задержки 33, И 14, ИЛИ 27 на первый вход сумматора, полученная сумма через элементы И 6, ИЛИ 22 вносится в регистр 31 произведения, из которого через элемент И 7 очередная тетргща поступает на вторую выходную шину 38 устройства. Остаток вновь вносится через элементы ИЛИ 26, И 8, ИЛИ 23 и затем на второй вход сумматора 30, а-также е выхода элемента ИЛИ 23 через элементы ИЛИ 24, задержки 33, И 14, ИЛИ 27 на первый вход сумматора 30. Предлагаемое устройство позволяет совмещать функции устройства ввода и вывода, и так как основные принци- пы преобразования кодов (при вводе и вьшоде) совпадают в главной операции - умножении на 1010, реализация описанного алгоритма не ведет к сумми рованию оборудования, необходимого для их отдельной реализации, а лишь незначительно увеличивает оборудование схемы. Формула изобретения Устройство для преобрйзования двоичного кода в двоично-десятичный, содержащее блок управления, выход которого соединен с входом распределителя импульсов, выход которого подключен к первым входам первого и второго элементов И, выход второго элемента И соединен с первой выхрдной шиной устройства, выход первого элемента И соединен с первым входом первого элемента ИЛИ, выход которого соединен с входом регистра произведения, выход третьего элемента И соединен с входом второго элемента ИЛИ, выход блока формирования коэффициентов соединен с входом регистра множителя, выход которого соединен с вх дом четвертого элемента И, выход которого соединен с. вторым входом вто jporo элемента ИЛИ, выход которого со Ьинен с первым входом последовательн го сумматора, выход которого соедине с вторым и первым входами соответственно первого и пятого элементов И, выход пятого элемента И соединен с вторым входом первого элемента ИЛИ, элемент задержки и регистр множимого, отличающеес я тем, что, с целью расширения класса решаемых задач путем возможности обратного преобразования, устройство дополнительно содержит буферный pe-i гистр, второй элемент задержки, элементы И, ИЛИ, причем вход блока yrfравления подключен к первой входной шине, выход распределителя импульсов соединен с первыми входами третьего с шестого по шестнадцатый и с вторыми входами четвертого и пятого элементов И, с входом блока формирования коэффициентов, вход буферного регистра соединен с второй входной шиной, а выход - с первыми входами третьего, четвертого и пятого элег ментов ИЛИ, выход третьего элемента ИЛИ соединен с входом первого элемен та задержки, выход которого соединен с вторыми входами девятого и десАтого элементов И, выход регистра множимого подключен к вторым входам (лестого, одиннадцатого, тринадцатого элементов И, выход регистра произведения соединен с вторыми входами второго, лвенадцатого, шестнадцатого элементов И и пятого элемента ИЛИ, выход которого подключен к второму входу третьего элемента И/ выход шестого элемента И соединен с вторыми входами третьего и четвертого элементов ИЛИ, выход.последнего подключен к вторым входам седьмого и восьмого элементов И, выходы которых соединены с третьим и четвертым входами второго элемента ИЛИ, выход которого соединен с третьим входом третьего элемента ИЛИ, выходы с девятого по двенадцатый элементов И подключены к входам шестого элемента ИЛИ, выход которого соединен с вторым входом последовательного сумма- , тора, выход которого соединен с вторыми входами четырнадцатого и пятнадца того элементов И, вькоды которых п6дкл очены к первым входам соответственно седьмого и восьмого элементов ИЛИ, выход тринадцатого элемента И соединен с вторым входом седьмого элемента ИЛИ, выход которого соединен с входом второго элемента задержки, аыход которого соединен с третьим входом четвертого элемента И и вторым входом восьмого элемента ИЛИ, выход которого подключен к входу регистра множимого, выход,шестнадцатого элемента И подключен к второй выходной шине устройства. Источники информации, принятые во внимание при экспертизе и:;ухомлинов М.М и Выховачец В.И. Преобразователи кодов чисел.Киев; Техника, 1965 , с. 88-92. 2. Авторское свидетельство СССР № 547763, кл. G 06 F 5/02, 1974.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ И УСТРОЙСТВО УМНОЖЕНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ КОДОВ | 2008 |

|

RU2386998C1 |

| СПОСОБ И УСТРОЙСТВО УМНОЖЕНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ КОДОВ | 2009 |

|

RU2410745C1 |

| Устройство для преобразования двоичного кода в двоично-десятичный | 1974 |

|

SU547763A1 |

| Преобразователь двоичных чисел в двоично-десятичные числа | 1980 |

|

SU941990A1 |

| Преобразователь двоично-десятичногоКОдА B дВОичНый КОд | 1979 |

|

SU809151A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1981 |

|

SU1013942A1 |

| Множительное устройство | 1982 |

|

SU1116427A1 |

| Матричное устройство для умножения двоичных и десятичных чисел | 1983 |

|

SU1200282A1 |

| Преобразователь двоично-десятичной дроби в двоичную дробь | 1978 |

|

SU752323A1 |

| Устройство для умножения | 1987 |

|

SU1509875A1 |

Авторы

Даты

1979-06-25—Публикация

1976-09-29—Подача