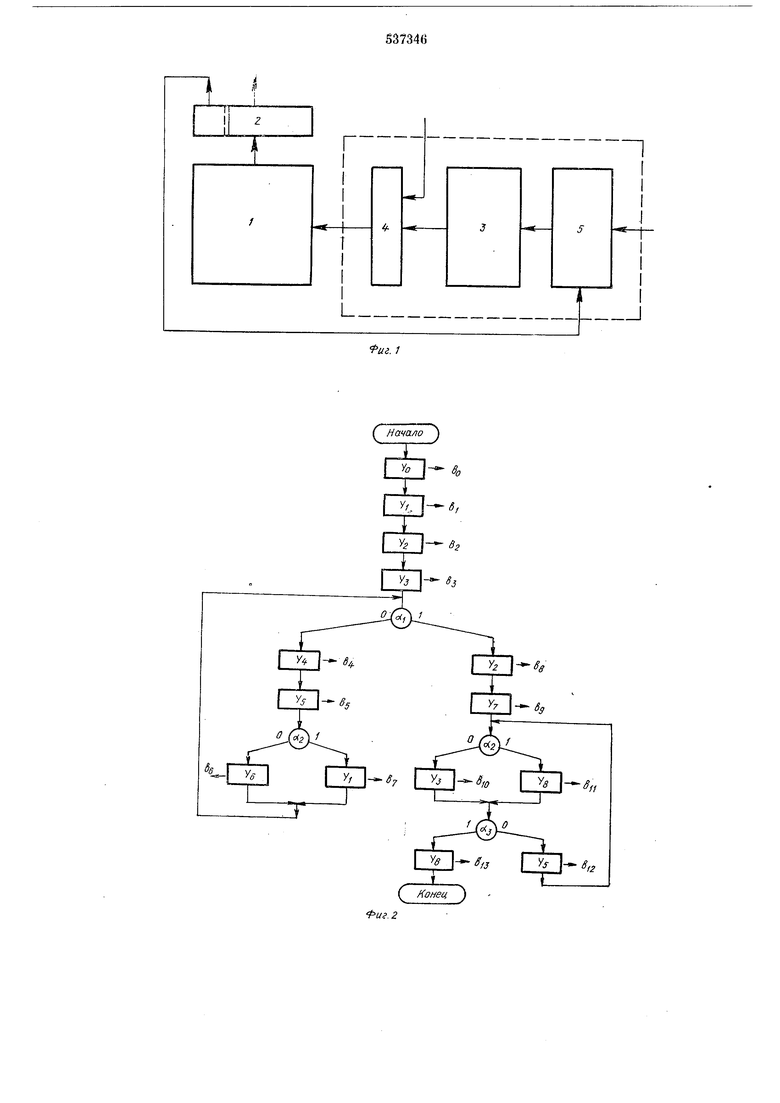

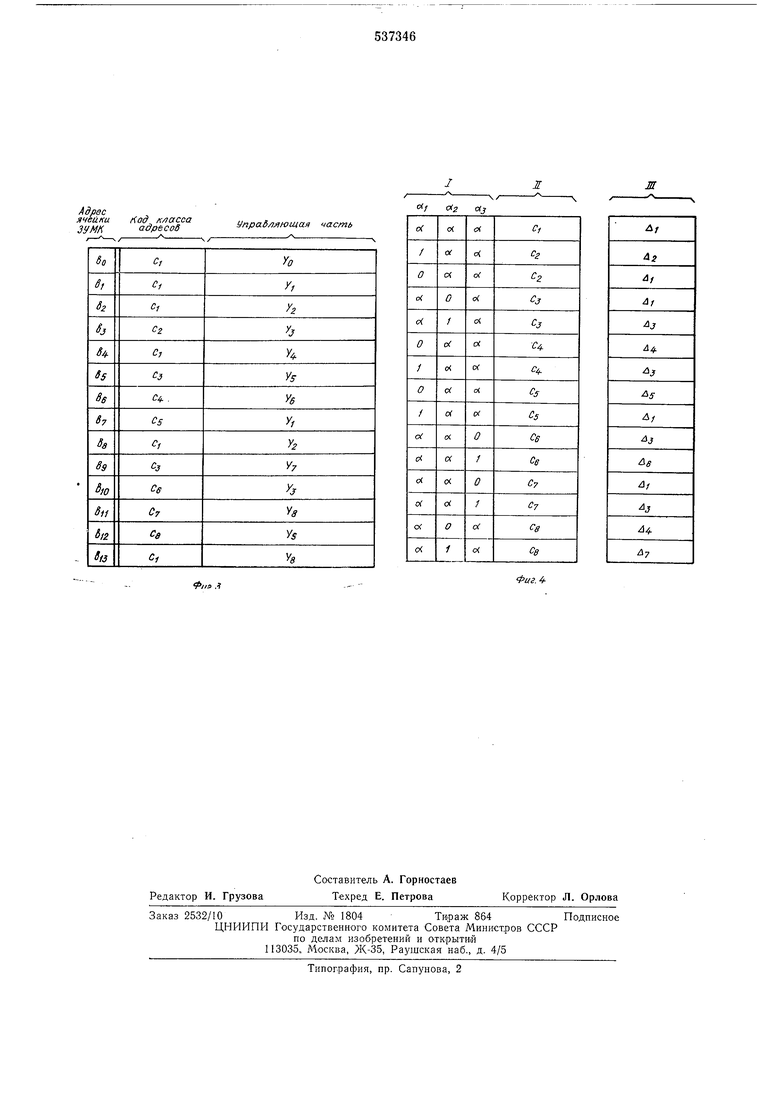

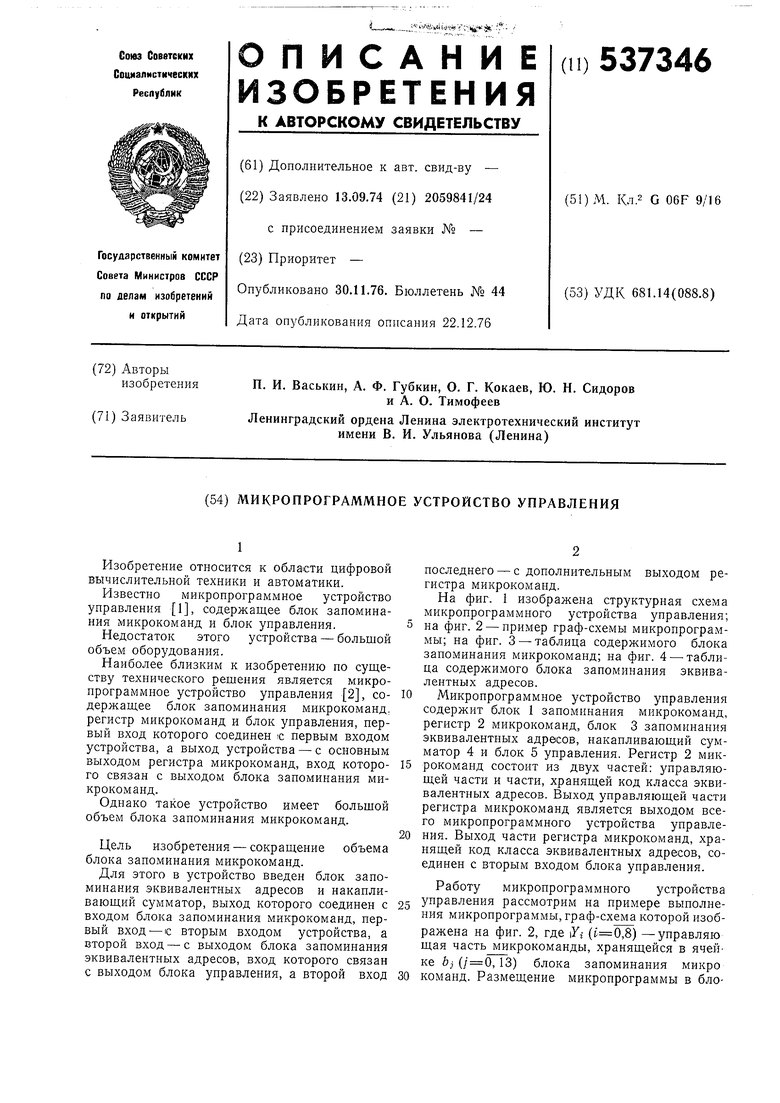

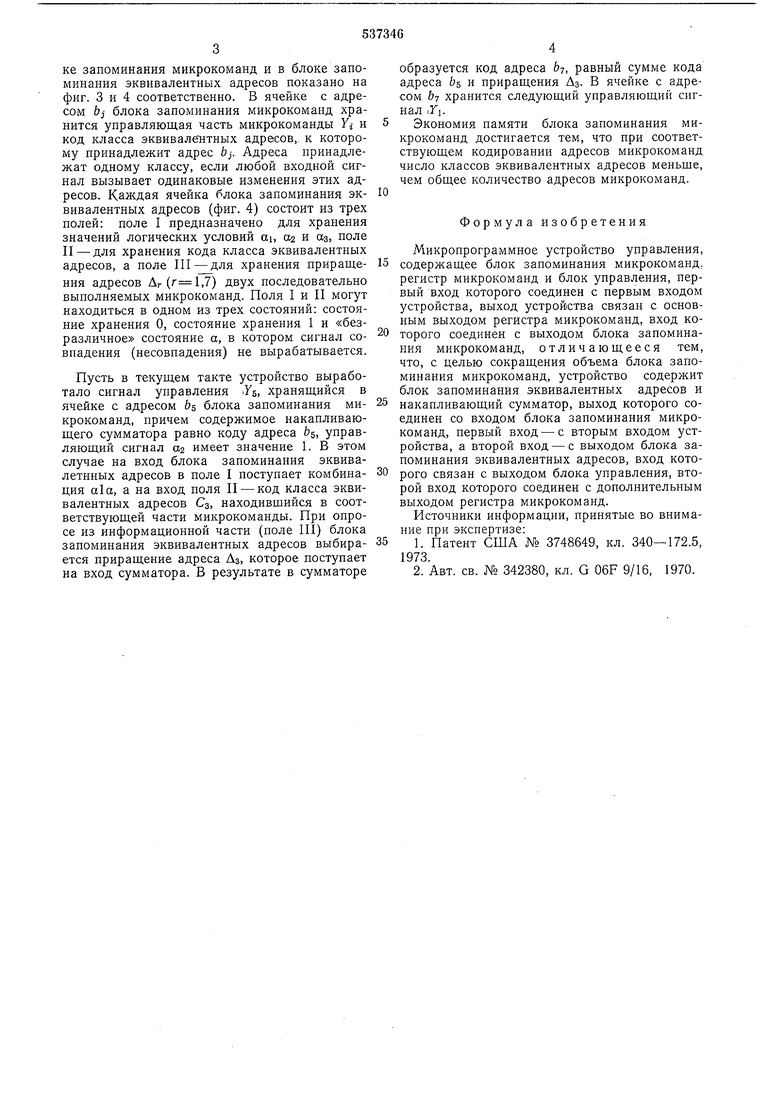

ке запоминания микрокоманд и в блоке запоминания эквивалентных адресов показано на фиг. 3 и 4 соответственно. В ячейке с адресом bj блока запоминания микрокоманд хранится управляющая часть микрокоманды Fj и код класса эквивалентных адресов, к которому принадлежит адрес bj. Адреса принадлежат одному классу, если любой входной сигнал вызывает одинаковые изменения этих адресов. Каждая ячейка блока запоминания эквивалентных адресов (фиг. 4) состоит из трех полей: поле I предназначено для хранения значений логических условий oi, 02 и аз, поле П-для хранения кода класса эквивалентных адресов, а поле III - для хранения прираш,еПИЯ адресов Аг(,7) двух последовательно выполняемых микрокоманд. Поля I и II могут находиться в одном из трех состояний: состояние хранения О, состояние хранения 1 и «безразличное состояние а, в котором сигнал совпадения (несовпадения) не вырабатывается.

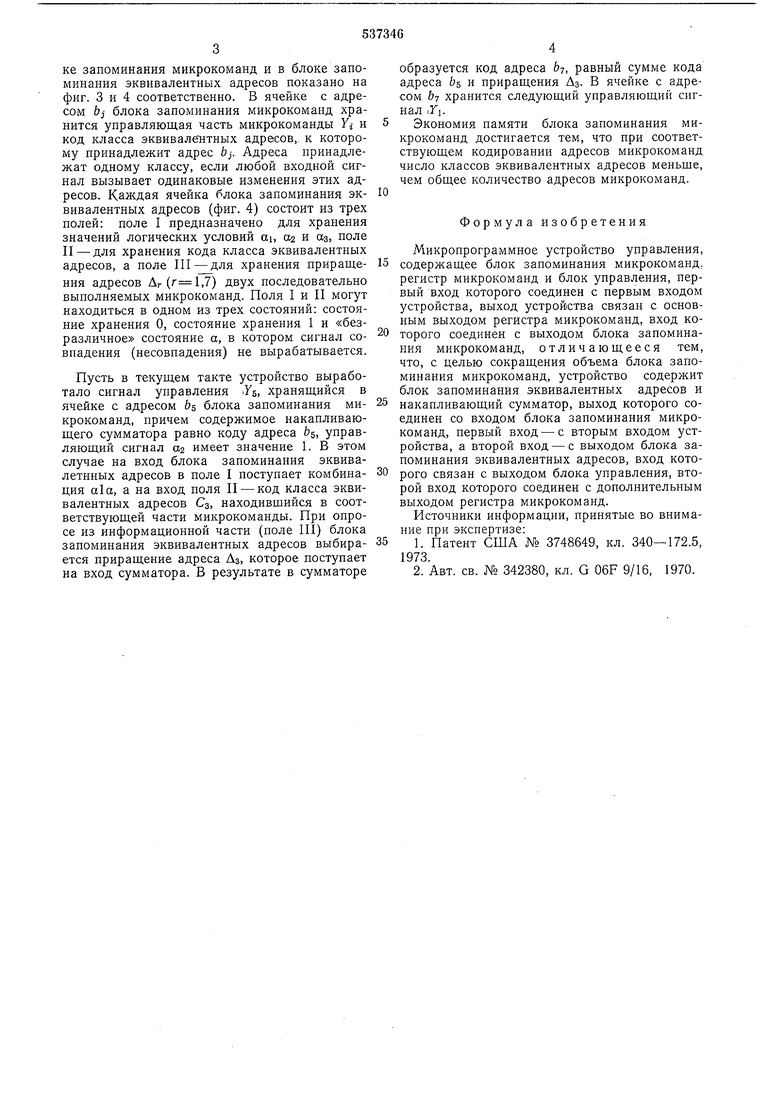

Пусть в текущем такте устройство выработало сигнал управления lYs, хранящийся в ячейке с адресом Ь блока запоминания микрокоманд, причем содержимое накапливающего сумматора равно коду адреса ЬБ, управляющий сигнал 02 имеет значение 1. В этом случае на вход блока запоминания эквивалетнных адресов в поле I поступает комбинация ala, а на вход поля П -код класса эквивалентных адресов Сз, находивщийся в соответствующей части микрокоманды. При опросе из информационной части (поле III) блока запоминания эквивалентных адресов выбирается приращение адреса Аз, которое поступает на вход сумматора. В результате в сумматоре

образуется код адреса Ьт, равный сумме кода адреса 65 и приращения АЗ. В ячейке с адресом 7 хранится следующий управляющий сигнал iyj.

Экономия памяти блока запоминания микрокоманд достигается тем, что при соответствующем кодировании адресов микрокоманд число классов эквивалентных адресов меньше, чем общее количество адресов микрокоманд.

Формула изобретения

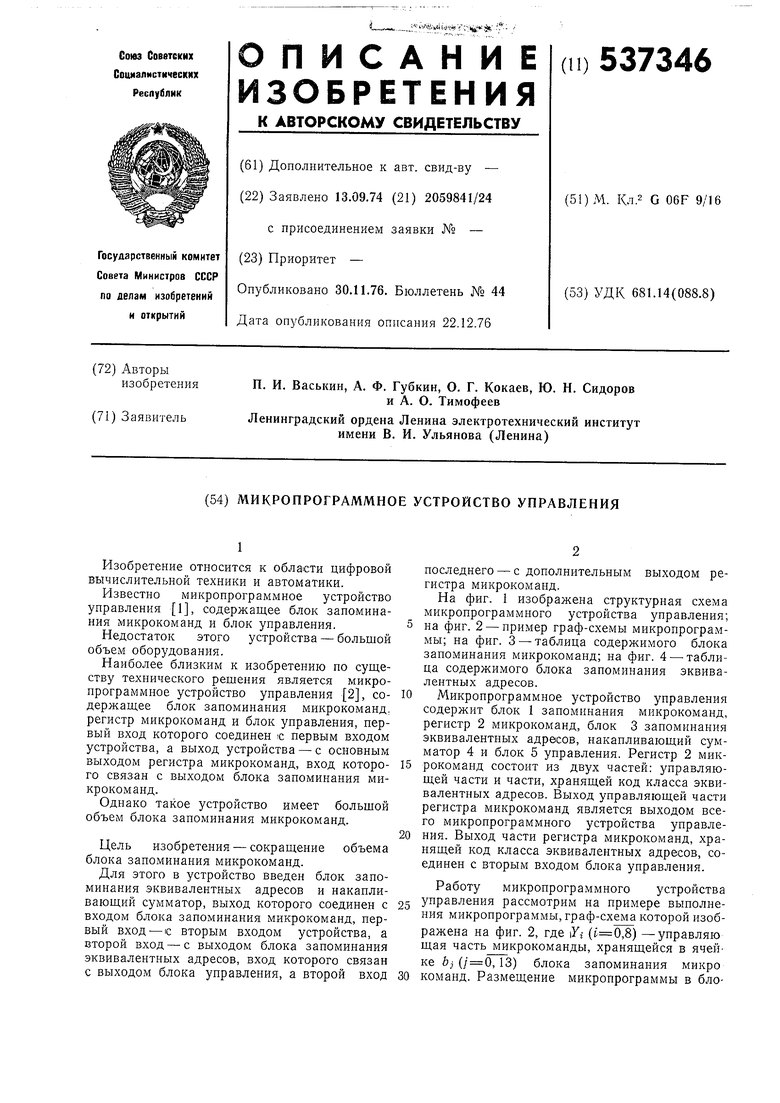

Микропрограммное устройство управления, содержащее блок запоминания микрокоманд, регистр микрокоманд и блок управления, первый вход которого соединен с первым входом устройства, выход устройства связан с основным выходом регистра микрокоманд, вход которого соединен с выходом блока запоминания микрокоманд, отличающееся тем, что, с целью сокращения объема блока запоминания микрокоманд, устройство содержит блок запоминания эквивалентных адресов и накапливающий сумматор, выход которого соединен со входом блока запоминания микрокоманд, первый вход - с вторым входом устройства, а второй вход - с выходом блока запоминания эквивалентных адресов, вход которого связан с выходом блока управления, второй вход которого соединен с дополнительным выходом регистра микрокоманд.

Источники информации, принятые во внимание при экспертизе:

1.Патент США № 3748649, кл. 340-172.5, 1973.

2.Авт. св. № 342380, кл. G 06F 9/16, 1970.

Г

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство микропрограммного управления | 1988 |

|

SU1536380A1 |

| Микропрограммное устройство управления | 1981 |

|

SU964640A1 |

| Микропрограммное устройство управления | 1981 |

|

SU951307A1 |

| Устройство микропрограммного управления | 1985 |

|

SU1287154A1 |

| Микропрограммное устройство управления | 1977 |

|

SU732871A1 |

| Программируемый формирователь многочастотного сигнала | 1989 |

|

SU1739472A1 |

| Цифровая электронная вычислительная машина последовательного действия | 1976 |

|

SU658564A2 |

| Процессор с совмещением операций | 1982 |

|

SU1138805A1 |

| Устройство для вычисления матрицы функций | 1987 |

|

SU1425706A1 |

| Устройство микропрограммного управления | 1985 |

|

SU1287156A1 |

L.

.J

//avo/T j -4,

Ш--5/

онец j

класса

Упра6/1яющая часть адресов

Фпа .

1

Фиг.4

Авторы

Даты

1976-11-30—Публикация

1974-09-13—Подача