1-1

Изобретение относится к вычислительной технике и может быть использовано для выборки многоиндексных данных, в частности для формирования адресов при выполнениибыстрого пре- образования Фурье и при реализадии цифровы х фильтров,

Целью изобретения является упрощение устройства при обработке индексированных данных за счет совме- щения оборудования для счета состояний и формирования и запоминания адресов возврата.

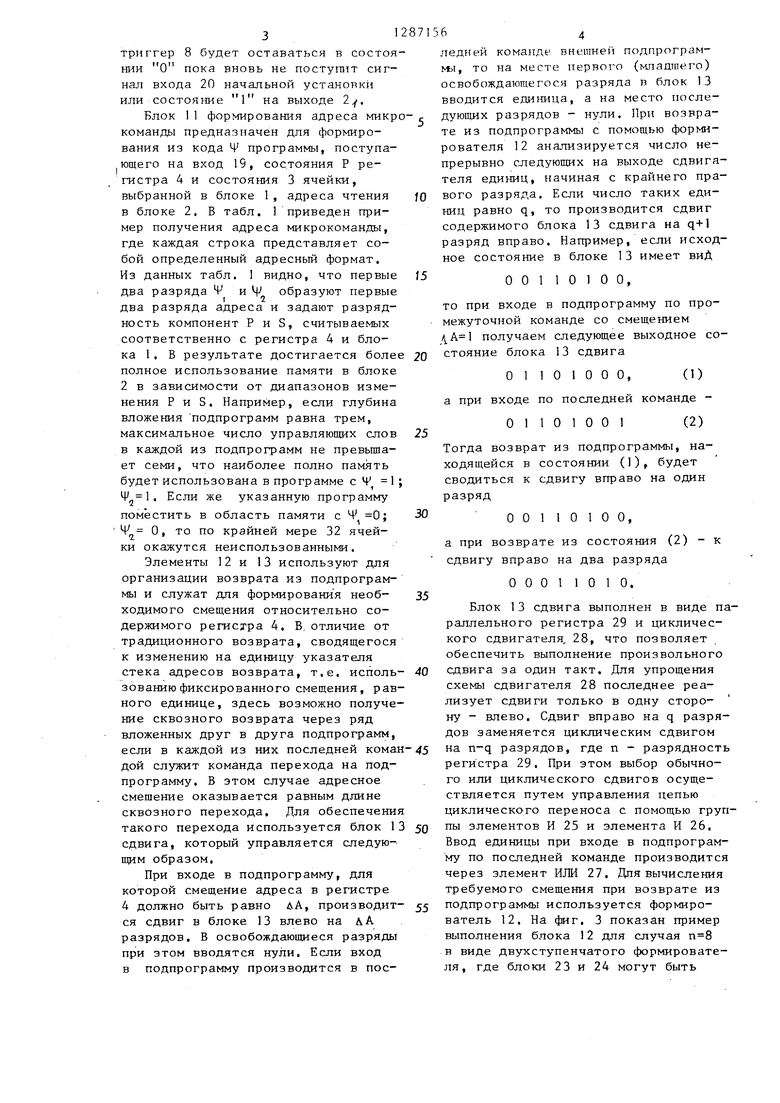

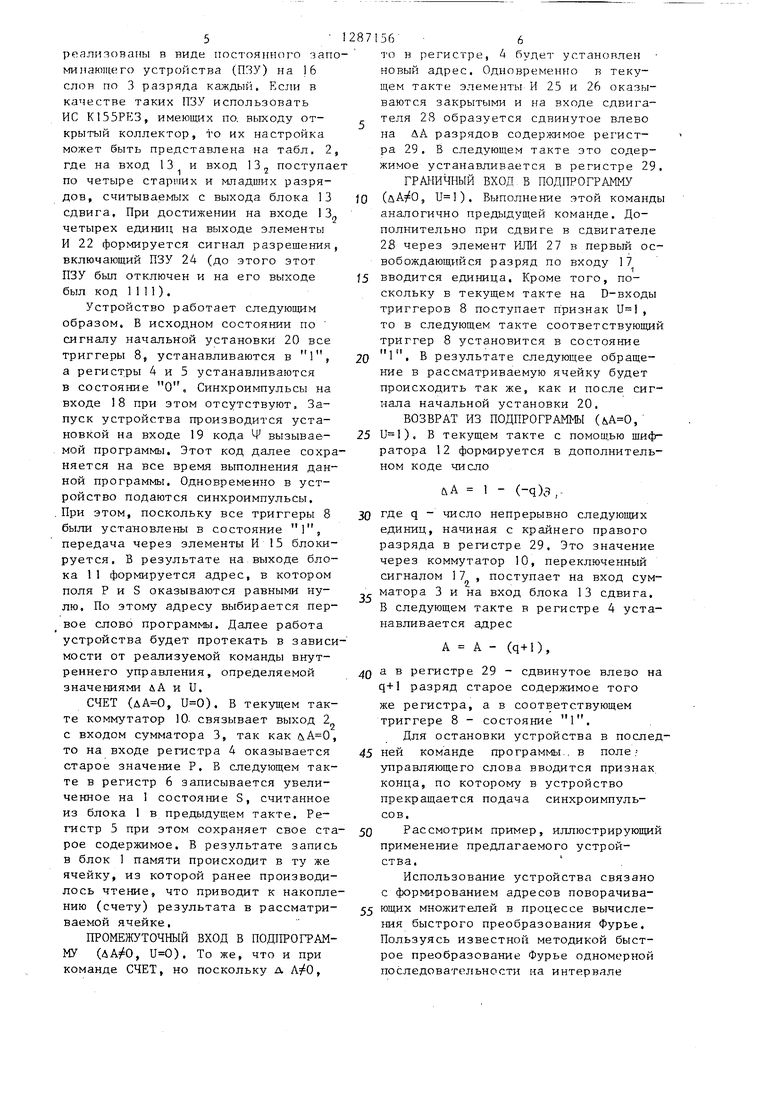

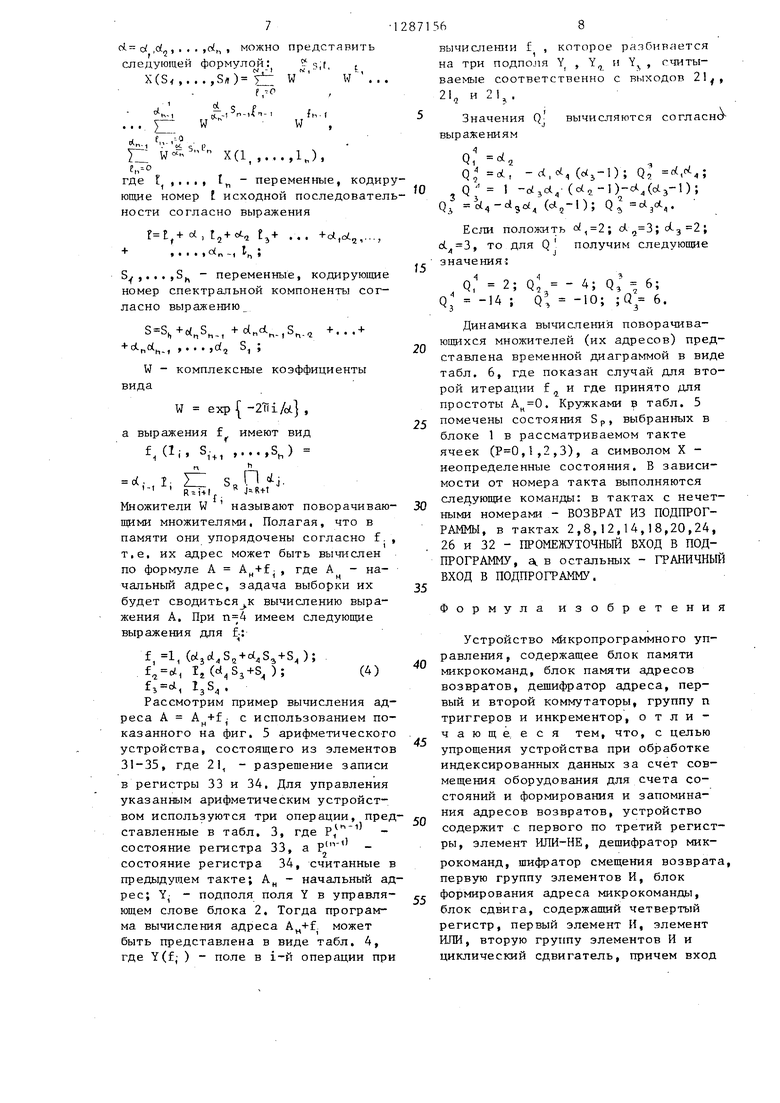

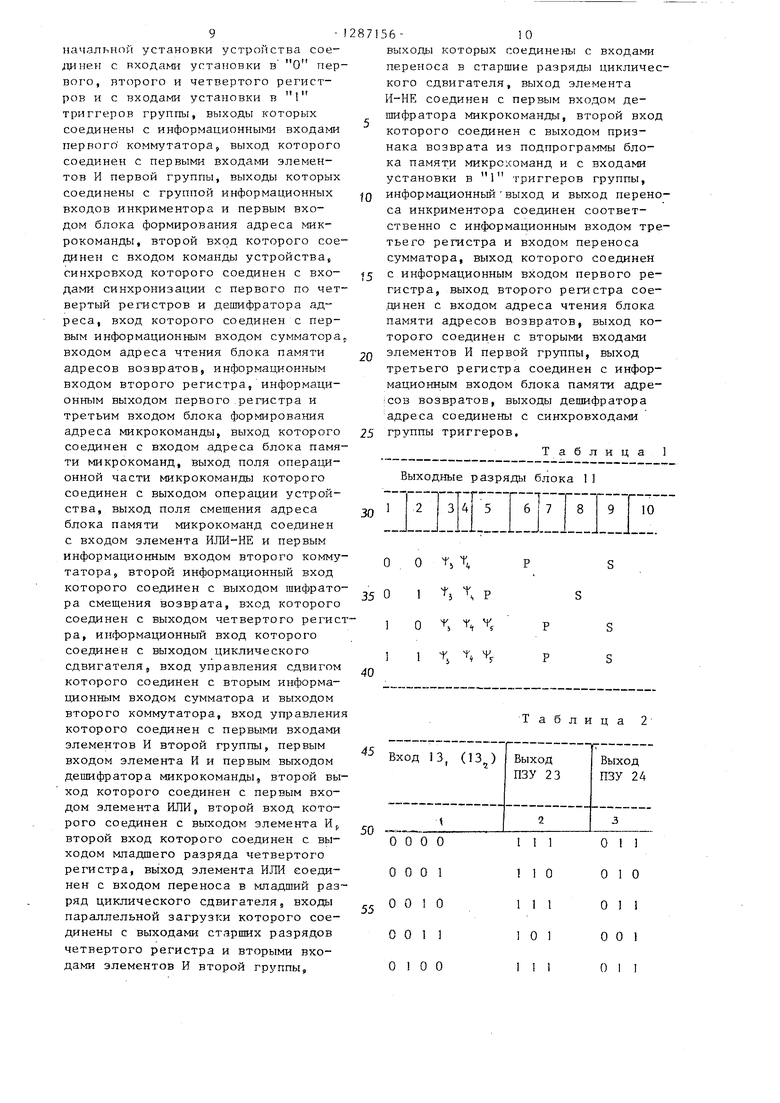

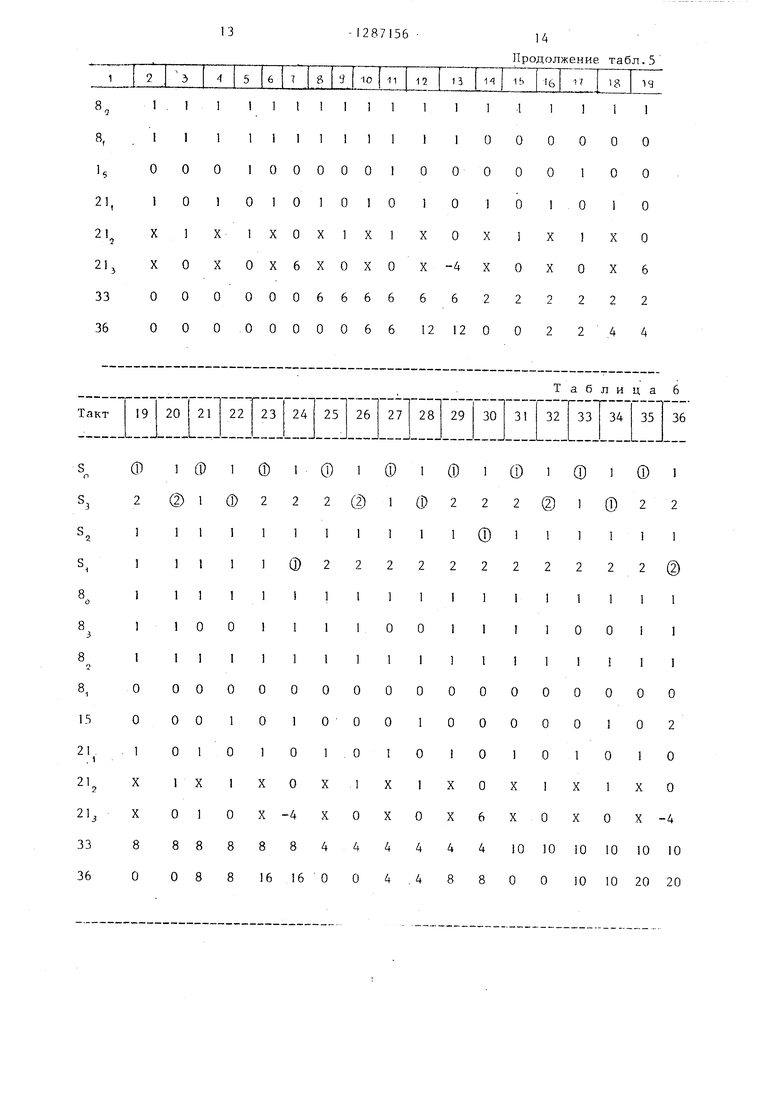

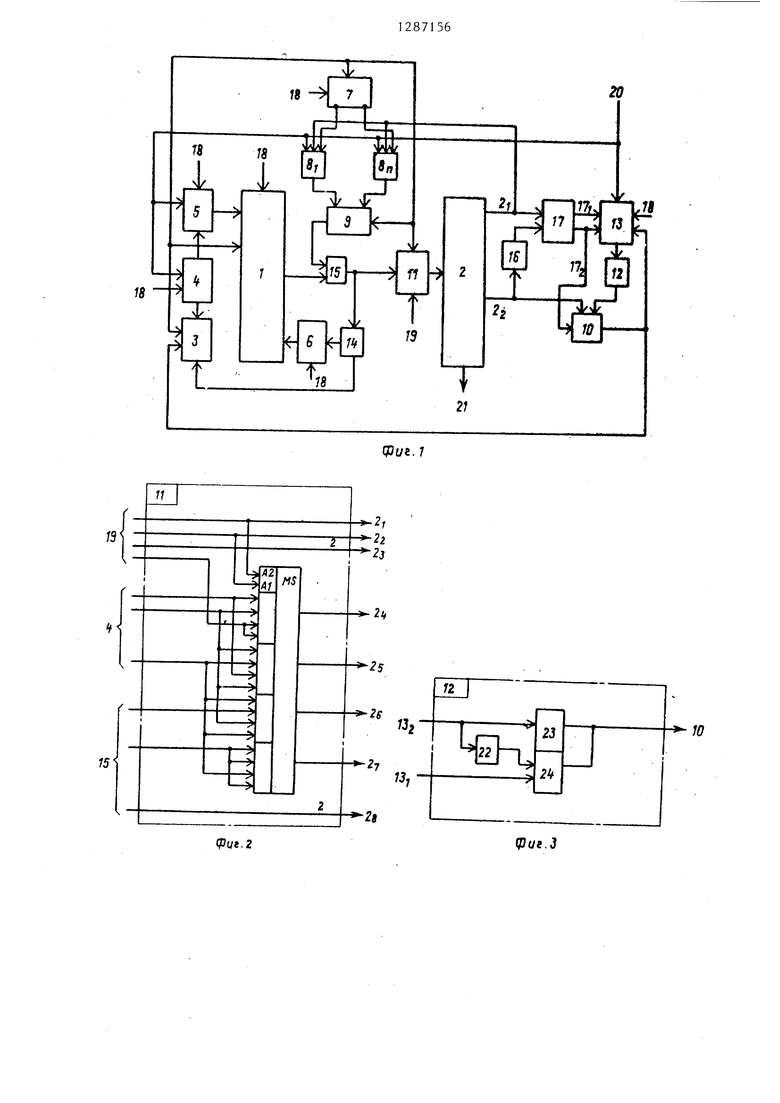

На фиг, 1 показана схема предлагаемого устройства; на фиг, 2 - схе- ма блока исполнительного адреса; на фиг, 3 - схема шифратора смещения возврата, на фиг, 4 - схема блока сдвига; на фиг, 5 - пример.использования устройства,

Устройство (фиг, 1) содержит блок 1 памяти адресов.возвратов, блок 2 памяти микрокоманд, сумматор 3, регистры 4-6, деишфратор 7 адре- са, группу триггеров 8, коммутаторы 9 и 10, блок 11 формирования адреса микрокоманд шифратор 12 смещетдая возврата, блок 13 сдвига, инкремен- тор 14, группу элементов И IS, эле- мент ИЛИ-НЕ 16, дешифратор 17 микрокоманд, синхровход 18 устройства, вход 19 команд устройства вход 20 начальной установки устройства, вы- ход 21 устройства.

Шифратор 12 смещения возврата (фиг, 3) состоит из элемента 22 и блоков 23 и 24 памяти старших и младших разрядов смещения.

Блок 13 сдвига (фиг, 4) содержит группу элементов И 25, элемент И 26 элемент ИЛИ 27, циклический сдвига- тель 28, регистр 29,

На фиг. 5 изображено предлагаемое устройство 305 сумматоры 31 и 32, регистры 33 и 34, коммутатор 35 выход 36 адреса микрокоманды, вход 37 начального адреса.

Все регистры, входящие в состав устройства синхронного типа, изменя- ют свое состояние по положительному фронту синхроимпульса.

Блок 1 памяти адресов возвратов представляет собой двухадресное оперативное запоминающее устройство (ОЗУ), позволяющее осуществлять параллельное чтение и запись по произвольным адресам. Примером такого ОЗУ может служить ИС КР1802ИРЬ

562

Блок 1 используется в качестве стека, в каждой ячейке которого с помощью регистра 6 и инкрементора 14 организуются счетчики. Состояние 9, выбранное при чтении ячейки, совместно с состоянием Р регистра 4 используется далее для адресации блока 2 памяти ьжкрокоманд,

Управляюише слона на выходе блока памяти 2 имеют формат:

ЛА

и

где uA - смещение содержимого регистра 4 при входе в под- . программу; и - однобитовый управляющими

признак; Y - выходное слово.

Сумматор 3 вместе с регистром 4 образуют указатель стека.

Регистры 4 и 6 используются для задержки на такт адреса записи и состояния S, сформированного инкре- ментором 14,

Элементы 7-9 используются для определения начального момента накопления в ячейках, выбираемых из блока 1, Триггер 8, соответствующий ячейке, в которой при следующем обращении должно быть начато новое накопление, устанавливается в состояние 1, Установка триггера 8 в это состояние производится либо по общему сигналу 20 начальной установки, либо по команде, поступающей с выхода 2 блока 2 памяти, В первом случае происходит общая установка всех триггеров, а во втором - только выбранного сигналом с дешифратора 7, Одновременно с выборкой i-ro триггера 8 происходит подключение его по выходу через коммутатор 9 к управляющим входам элементов 15,, Если обращение к определенной ячейке блока 1 происходит в начальный момент накопления, то соответствующий триггер 8 оказывается в состоянии 1 и остается в нем до окончания такта, В результате на управляю шцх входах элементов 15 действует запрет и на входе инкрементора 14 будет находиться нулевой код. После окончания такта выборки указанно ячейки в случае наличия на выходе 2 состояния О соответствующий триггер 8 по заднему фронту выходного сигнала дешифратора 7 переходит в состояние 0 Далее при каждом последующем обращении к той же ячейке

триггер 8 будет оставаться в состоянии О пока вновь не поступит сигнал входа 20 начальной установка или состояние 1 на выходе 2.

Блок 11 фор гарования адреса микр команды предназначен для формирования из кода ф программы, поступающего на вход 19, состояния Р регистра 4 и состояния 3 ячейки, выбранной в блоке 1, адреса чтения в блоке 2, В табл. 1 приведен пример получения адреса микрокоманды, где каждая строка представляет собой определенный адресный формат. Из данных табл. 1 видно, что первые два разряда V и ф образуют первые два разряда адреса и задают разрядность компонент Р и S, считываемых соответственно с регистра 4 и блока 1 , В результате достигается более полное использование памяти в блоке 2 в зависимости от диапазонов изменения Р и S, Например, если глубина вложения подпрограмм равна трем, максимальное число управляющих слов в каждой из подпрограмм не превьщ1а- ет семи, что наиболее полно память будет использована в программе с Ч 1 ; Ф,1. Если же указанную программу поместить в область памяти с Ч 0; О, то по крайней мере 32 ячейки окажутся неиспользованными.

Элементы 12 и 13 используют для организации возврата из подпрограммы и служат для формировани я необ- ходимого смещения относительно содержимого регистра 4, В, отличие от традиционного возврата, сводящегося к изменению на единицу указателя стека адресов возврата, т.е. исполь- зованию фиксированного смещения, равного единице, здесь возможно получение сквозного возврата через ряд вложенных друг в друга подпрограмм, если в каждой из них последней коман дои служит команда перехода на подпрограмму. В этом случае адресное смешение оказывается равным длине сквозного перехода. Для обеспечения такого перехода используется блок 13 сдвига, который управляется следую-- щим образом,

При входе в подпрограмму, для которой смещение адреса в регистре 4 должно быть равно uA, производит- ся сдвиг в блоке 13 влево на &А разрядов, В освобождающиеся разряды при этом вводятся нули. Если вход в подпрограмму производится в последней команде внешней подпрограм- ьы, то на месте первого (шaдшeгo) освобождающегося разряда в блок 13 вводится единица, а на место последующих разрядов - нули. При возврате из подпрограммы с помощью формирователя 12 анализируется число непрерывно следующих на выходе сдвига- теля единиц, начиная с крайнего правого разряда. Если число таких единиц равно q, то производится сдвиг содержимого блока 13 сдвига на q+1 разряд вправо. Например, если исходное состояние в блоке 13 имеет виД

001 10100,

то при входе в подпрограмму по промежуточной команде со смещением получаем следующее выходное состояние блока 13 сдвига

01101000,(1)

а при входе по последней команде - 01101001(2)

Тогда возврат из подпрограммы, находящейся в состоянии (1), будет сводиться к сдвигу вправо на один разряд

001 10100,

а при возврате из состояния (2) - к сдвигу вправо на два разряда

00011010,

Блок 13 сдвига выполнен в виде праллельного регистра 29 и циклического сдвигателя, 28, что позволяет обеспечить выполнение произвольного сдвига за один такт. Для упрощения схемы сдвигателя 28 последнее реализует сдвиги только в одну сторону - влево. Сдвиг вправо на q разрядов заменяется циклическим сдвигом на n-q разрядов, где п - разрядност регистра 29. При этом выбор обычного или циклического сдвигов осуществляется путем управления цепью циклического переноса с помощью группы элементов И 25 и элемента И 26. Ввод единицы при входе в подпрограмму по последней команде производится через элемент ИЛИ 27, Для вычисления требуемого смещения при возврате из подпрограммы используется формирователь 12. На фиг. 3 показан пример выполнения блока 12 для случая в виде двухступенчатого формирователя, где блоки 23 и 24 могут быть

5

реализованы в виде постоянного запоминающего устройства (ПЗУ) на 16 слон по 3 разряда каждый. Если в качестве таких ПЗУ использовать ИС К155Р 3, имеющих по. выходу от- крытый коллектор, то их настройка может быть представлена на табл, 2, где на вход 13 и вход 13 поступае по четыре старших и младших разрядов, считываемых с выхода блока 13 сдвига. При достижении на входе 132 четырех единиц на выходе элементы И 22 формируется сигнал разрешения, включающий ПЗУ 24 (до этого этот ПЗУ бьш отключен и на его выходе был код 1111).

Устройство работает следующим образом, В исходном состоянии по сигналу начальной установки 20 все триггеры 8, устанавливаются в 1, а регистры 4 и 5 устанавливаются в состояние О, Синхроимпульсы на входе 18 при этом отсутствуют. Запуск устройства производится установкой на входе 19 кода вызывав- мой программы. Этот код далее сохраняется на все время выполнения данной программы. Одновременно в устройство подаются синхроимпульсы. При этом, поскольку все триггеры 8 были установлены в состояние 1, передача через элементы И 15 блокируется, В результате на.выходе блока 11 формируется адрес, в котором поля Р и S оказываются равными нулю. По этому адресу выбирается первое слово программы. Далее работа устройства будет протекать в зависимости от реализуемой команды внутреннего управления, определяемой значениями дА и U,

СЧЕТ (, ), В текущем такте коммутатор 10. связывает выход 2 с входом сумматора 3, так как то на входе регистра 4 оказывается старое значение Р, В следующем такте в регистр 6 записывается увеличенное на 1 состояние S, считанное из блока 1 в предыдущем такте. Регистр 5 при этом сохраняет свое ста рое содержимое, В результате запись в блок 1 памяти происходит в ту же ячейку, из которой ранее производилось чтение, что приводит к накоплению (счету) результата в рассматри- ваемой ячейке,

ПРОМЕЖУТОЧНЫЙ ВХОД В ПОДПРОГРАММУ (, ). То же, что и при команде СЧЕТ, но поскольку л ,

0 5 0 Q

5 0 55

5

566

то в регистре, 4 будет установлен новый адрес. Одновременно в текущем такте элементы И 25 и 26 оказываются закрытыми и на входе сдвига- теля 28 образуется сдвинутое влево на ДА разрядов содержимое регистра 29 , В следующем такте это содержимое устанавливается в регистре 29,

ГРА1-1ИЧНЫЙ ВХОД В ПОДПРОГРАММУ (, и). Выполнение этой команды аналогично предыдущей команде. Дополнительно при сдвиге в сдвигателе 28 через элемент ШШ 27 в первый освобождающийся разряд по входу 17 вводится единица. Кроме того, поскольку в текущем такте на D-входы триггеров 8 поступает признак , то в следующем такте соответствующий триггер 8 установится в состояние 1, В результате следующее обращение в рассматриваемую ячейку будет происходить так же, как и после сиг-нала начальной установки 20,

ВОЗВРАТ ИЗ ПОДПРОГРАММЫ (, и), В текущем такте с помош.ью шифратора 12 формируется в дополнительном коде число

ЛА 1 - (-q)a,где q - число непрерывно следующих единиц, начиная с крайнего правого разряда в регистре 29, Это значение через коммутатор 10, переключенный сигналом 17 , поступает на вход сумматора 3 и на вход блока 13 сдвига, В следующем такте в регистре 4 устанавливается адрес

А А - (q+1),

а в регистре 29 - сдвинутое влево на q+1 разряд старое содержимое того же регистра, а в соответствующем триггере 8 - состояние 1,

Для остановки устройства в последней команде программы,, в поле. управляющего слова вводится признак конца, по которому в устройство прекращается подача синхроимпульсов.

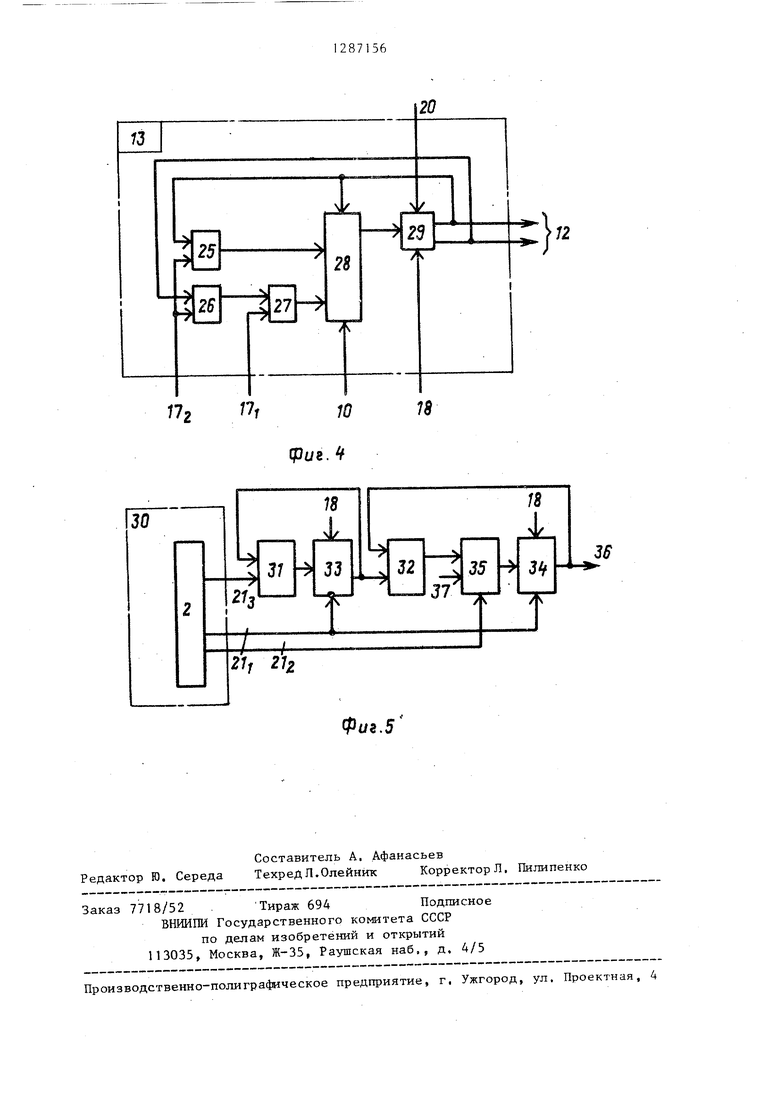

Рассмотрим пример, иллюстрирующий применение предлагаемого устройства.

Использование устройства связано с формированием адресов поворачивающих множителей в процессе вычисления быстрого преобразования Фурье, Пользуясь известной методикой быстрое преобразование Фурье одномерной последовательности на интервале

о(,о(,,, . . . ,о(„ , можно представить

J.,

дующей формулой: X(S,,..,8л)

1,0

9L S f

С(.-1 r - -t 1-

W

W

W

W

fb-f

. 0

1 . i 5, L HI W«- fh-x(i.

,1J,

где t , , . . , l - переменные, кодиру- юпще номер t исходной последовательности согласно выражения

,+ ot, ... +ol,ot,j,...,

+ ,... ,o(n -1 1„;

S,...,S - переменные, кодирующие номер спектральной компоненты согласно выражению..

,+c,S,,, +Ы.Л,.,5,.,

+ о1.„о1.

+ . . ,+ h-i jo s S, ;

W - комплексные коэффициенты вида

f.(l

W ехр{ ,

имеют вид Sj ) выражения f имеют вид

1 + 1

,-,.

S П «LJ

R-b. « i i

Множители W называют поворачивающими множителями. Полагая, что в памяти они упорядочены согласно f., т.е. их адрес может быть вычислен по формуле А ., где А - начальный адрес, задача выборки их будет сводиться к вычислению выражения А. При имеем следующие выражения для f-:

f, 1, (Mjci,S,-bd, , 1, ();(4)

fj, 1,5,.

Рассмотрим пример вычисления адреса А А +f: с использованием поИ

казанного на фиг. 5 арифметического устройства, состоящего из элементов 31-35, где 21, - разрешение записи в регистры 33 и 34. Для управления указанным арифметическим устройством используются три операции, представленные в табл. 3, где Р) - состояние регистра 33, а состояние регистра 34, считанные в предыдущем такте; А - начальный адрес; Y - подполя поля Y в управля- ющем слове блока 2. Тогда программа вычисления адреса А„+ может быть представлена в виде табл. 4, где Y(f; ) - поле в i-й операции при

5

0

5

0

5

вычиспении f , которое разбивается на три подполя У , Y и Y, , считываемые соответственно с выходов 21, 21, и 21,.

Значения Q вычисляются согласна- выражениям

Q

Q, di, -d,ci, (); Q o(,f,; Q; 1 -d,(-)-c,(); Q, ,-0(30, (cA,-l); Q .

Если положить о ,2; d,. , TO для Q получим следуюгцие значения:

Q; 2; Q - 4; Q, 6; Qj -14 ; Q -10; ;a 6.

Динамика вычисления поворачивающихся множителей (их адресов) представлена временной диаграммой в виде табл. 6, где показан случай для второй итерации f , и где принято для простоты , Кружками в табл. 5 помечены состояния Sp, выбранных в блоке 1 в рассматриваемом такте ячеек (,1,2,3), а символом X - неопределенные состояния. В зависимости от номера такта выполняются следующие команды: в тактах с нечетными номерами - ВОЗВРАТ ИЗ ПОДПРОГРАММЫ, в тактах 2,8,12,14,18,20,24, 26 и 32 - ПРОМЕЖУТОЧНЫЙ ВХОД В ПОДПРОГРАММУ, а в остальных - ГРАНИЧНЫЙ ВХОД В ПОДПРОГРАММУ.

0

г

5

0

Формула изобретения

Устройство микропрограммного управления, содержащее блок памяти микрокоманд, блок памяти адресов возвратов, дешифратор адреса, первый и второй коммутаторы, группу п триггеров и инкрементор, отличающееся тем, что, с целью упрощения устройства при обработке индексированных данных за счет совмещения оборудования для счета состояний и формирования и запоминания адресов возвратов, устройство содержит с первого по третий регистры, элемент ИЛИ-НЕ, дешифратор микрокоманд, шифратор смещения возврата, первую группу элементов И, блок формирования адреса микрокоманды, блок сдвига, содержащий четвертый регистр, первый элемент И, элемент ИЛИ, вторую группу элементов И и циклический сдвигатель, причем вход

начальной установки устройства сое- данет-1 с входами установки в О первого, второго и четвертого регистров и с входами установки в

Г

триггеров группы, выходы которых соединены с информационными входами первого коммутатора, выход которого соединен с первыми входами элементов И первой группы, выходы которых соединены с группой информационных входов инкриментора и первым входом блока формирования адреса микрокоманды, второй вход которого соединен с входом команды устройства, синхровход которого соединен с входами синхронизации с первого по четвертый регистров и деизифратора адреса, вход которого соединен с первым информационным входом сумматорЯр входом адреса чтения блока памяти адресов возвратов, информационным входом второго регистра, информационным выходом первого .регистра и третьим входом блока формирования адреса микрокоманды, выход которого соединен с входом адреса блока памяти микрокоманд, выход поля операционной части микрокоманды которого соединен с выходом операции устройства, выход поля смещения адреса блока памяти микрокоманд соединен с входом элемента ИЛИ-НЕ и первым информационным входом второго коммутатора, второй информационный вход которого соединен с выходом шифратора смещения возврата, вход которого соединен с выходом четвертого регистра, информационный вход которого соединен с выходом циклического сдвигателя, вход управления сдвигом которого соединен с вторым информационным входом сумматора и выходом второго коммутатора, вход управления которого соединен с первыми входами элементов И второй группы, первым входом элемента И и первым выходом дешифратора микрокоманды, второй выход которого соединен с первым входом элемента ИЛИ, второй вход которого соединен с выходам элемента Ир второй вход которого соединен с выходом младшего разряда четвертого регистра, выход элемента ИЛИ соединен с входом переноса в младший разряд циклического сдвигателя, входы параллельной загрузки которого соединены с выходами старших разрядов четвертого регистра и вторыми входами элементов И второй группы.

1287156-10

выходы которых соединены с входами переноса в старшие разряды циклического сдвигателя, выход элемента И-НЕ соединен с первым входом дешифратора микрокоманды, второй вход которого соединен с выходом признака возврата из подпрограммы блока памят;и микрокоманд и с входами установки в 1 триггеров группы,

IQ информационныйвыход и выход переноса инкриментора соединен соответственно с информационным входом третьего регистра и входом переноса сумматора, выход которого соединен

5 с информационным входом первого регистра, выход второго регистра сое- цинен с входом адреса чтения блока памяти адресов возвратов, выход которого соединен с вторыми входами

2Q элементов И первой группы, выход третьего регистра соединен с информационным входом блока памяти адре- icoB возвратов, выходы дешифратора адреса соединены с синхровходами

25 группы триггеров.

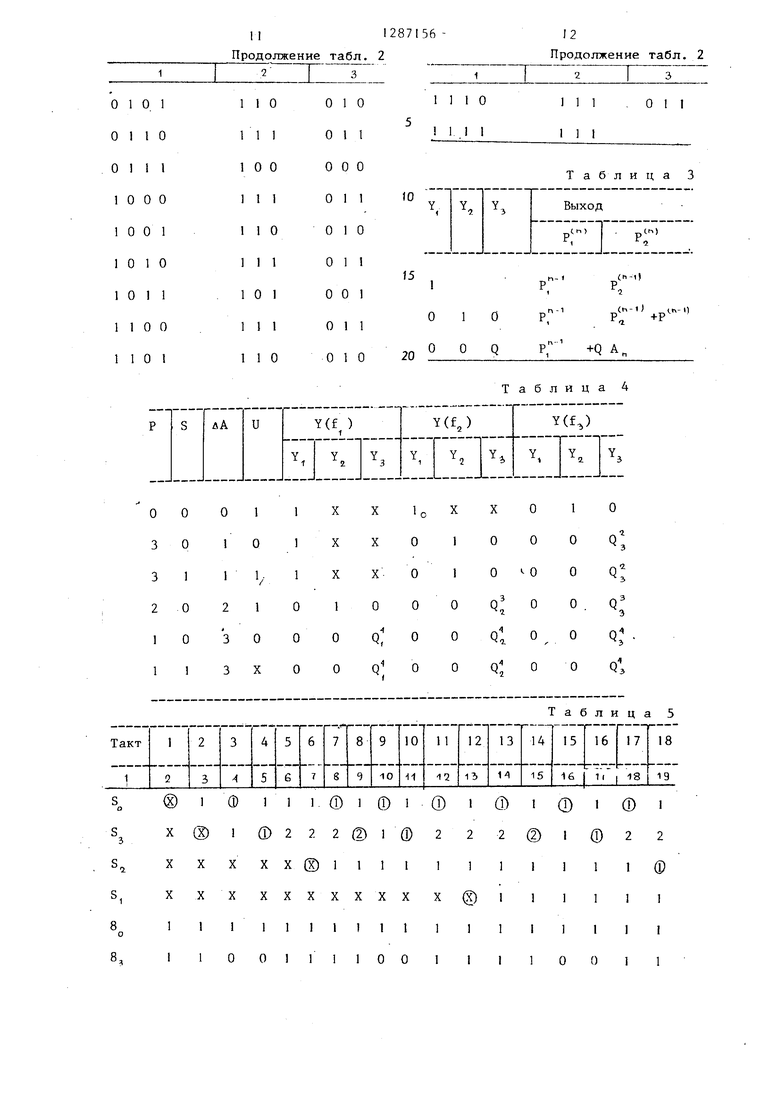

Таблица 1

Выходные разряды блока 1

30

35

S S

40

Таблица 2

45

50

55

S S

Таблица 2

1

II1287156 Продолжение табл. 2

3

1 1 1 1 0 1

11О

111

1оо

111

11о

111

1о1

111

11о

о1о

о11

000

о11

о1о

о11

оо1

о11

о1о

о

о

1

о

о

1

О 1 Г О

21

3О 3 X

1 1 1 О О

о

X X X

1

о о

® 1 Ф 11 1 0)1ф1®

X ® 1 Ф 2 2 2 ф ф 2 2 2®1ф2

ХХХХХ®1111 1 1 11111

ХХХХХХХХХХХФ11111

1 I 11111111 1 1 1I111

1

О 0111100 I 1

1

12 Продолжение табл. 2

2 Г 3

110

111

1 1 1 1 I

о I 1

(О

1

о 1 о о

о

Q

П-1

(n-i)

pC- J р-0

+Q А,

Таблица 4

о о о о о

X

1 1

о о о

X о

о о о - о

Q о г

г.

Q: о

Q , о

1

о о о о о

Q:

Таблица 5

1

2

Ф

1

I

1

о о

5

21, 2,

21з 33

36

1I

1I

ОО

1О

X1

Xо

оо

оо

1 1 1 1 1 1 1 1 1111111 О

1

X

1 1

1 1000000

1000001 о 00 о о 1 о о

0101010 1 о 1X0X1X1 X о

о 1

1 X о

X 0X6X0X0 Х-4 X о X о X

о 0006666

00000066 12 12 о о

S

п

S,

15 21

21, 21,

33 36

Ф

2

1

1

1

1

1

О

О

1

X

X

®

1 1 1

10)

®1

11

11

11

1о о

11 I

оо

оо

о1

1X

о1

88

О8

® 1 0 1

1 1 (D 2

1 1

Ф

1

2 1 1

® 1

1

1

Ф

1

0) 1 © I Ф 1 ® 1

2 2 2 @ 1 Ф 2 2 1 (Г) 1 1 1 1 I 1

1111

1 1

0О

11

1 1

1111

1111

1 1

0О

1

X О X

1 О 1

X 1 X О

X

X -4 X о X о X

1 1

1

© 1

1 1 I 1

000000000000000

0100010000010

2

1 о X о

X о X о X -4 10 10 10 10 10 10

16 16 о о 4,4 В 8 О О 10 10 20 20

Продолжение табл.5

1 1

1 1000000

о 1

1 X о

Таблица 6

1

1

2 1 1

® 1

1

1

Ф

1

0) 1 © I Ф 1 ® 1

2 2 2 @ 1 Ф 2 2 1 (Г) 1 1 1 1 I 1

1

1 1

0О

11

1 1

1111

1111

1 1

0О

1

1 1

© 1

1 1 I 1

О 1

1 X О

X

1

10000010

2

1 о X о

X о X о X -4 10 10 10 10 10 10

Фиг. 2

.J

172

Г7г

10

фиг. 4

Фиг.5

Составитель А. Афанасьев Редактор Ю. Середа ТехреД Л.Олейник Корректор Л. Пилипенко

Заказ 7718/52 . Тираж 694Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

18

| название | год | авторы | номер документа |

|---|---|---|---|

| Процессор программируемого контроллера | 1988 |

|

SU1550515A2 |

| Устройство для вычисления функций | 1989 |

|

SU1705822A1 |

| Устройство генерации тестовых последовательностей для контроля оперативных накопителей | 1989 |

|

SU1636858A1 |

| Микропрограммное устройство управления | 1987 |

|

SU1522203A1 |

| Устройство микропрограммного управления | 1988 |

|

SU1536380A1 |

| Устройство для сопряжения центрального процессора с группой арифметических процессоров | 1984 |

|

SU1254495A1 |

| Арифметическое устройство с микропрограммным управлением | 1988 |

|

SU1541594A1 |

| Устройство для сопряжения ЦВМ с внешним устройством | 1989 |

|

SU1661779A1 |

| Устройство для поиска информации в памяти | 1985 |

|

SU1352494A1 |

| Процессор программируемого контроллера | 1985 |

|

SU1406595A1 |

Изобретение относится к области . вычислительной техники и может быть использовано для выборки многоиндексных данных, в частности, для формирования адресов при выполнении быстрого преобразования Фурье. Цель изобретения - сокращение оборудования устройства при обработке индексированных данных путем совмещения оборудования для счета состояний и формирования и запоминания адресов возвратов. Устройство содержит блок памяти адресов возвратов, блок памяти микрокоманд, сумматор, три ре- , гистра, дешифратор адреса, группу п триггеров, два коммутатора, блок формирования адреса микрокоманды, шифратор смещения возврата, блок сдвига, инкрементор, группу элементов И, элемент ИЛИ - НЕ, дешифратор микрокоманд. Введение трех регистров, дешифратора нулевого смещения, группы элементов И, блока формирования адреса микрокоманды, дешифратора микрокоманд, формирователя смещения возврата и блока сдвига обеспечивает достижение цели. 5 ил,, 5 табл. (5 (Л ю сх ел 05

| Микропрограммное устройство управ-лЕНия | 1978 |

|

SU807290A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство микропрограммного управления | 1984 |

|

SU1239715A1 |

Авторы

Даты

1987-01-30—Публикация

1985-06-17—Подача