Изобретение относится к вычислительной технике и может быть использовано в устройствах управления ЭВМ, в частности при проектировании дисплейных процессоров.

Целью изобретения является повышение быстродействия устройства.

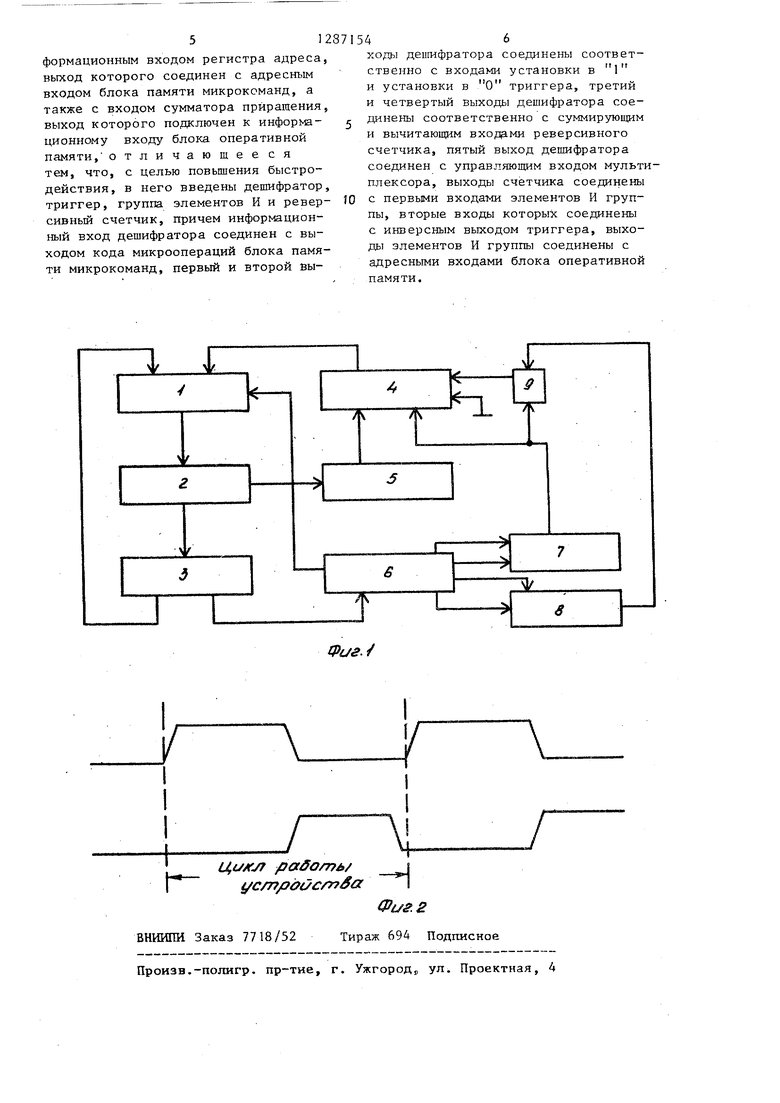

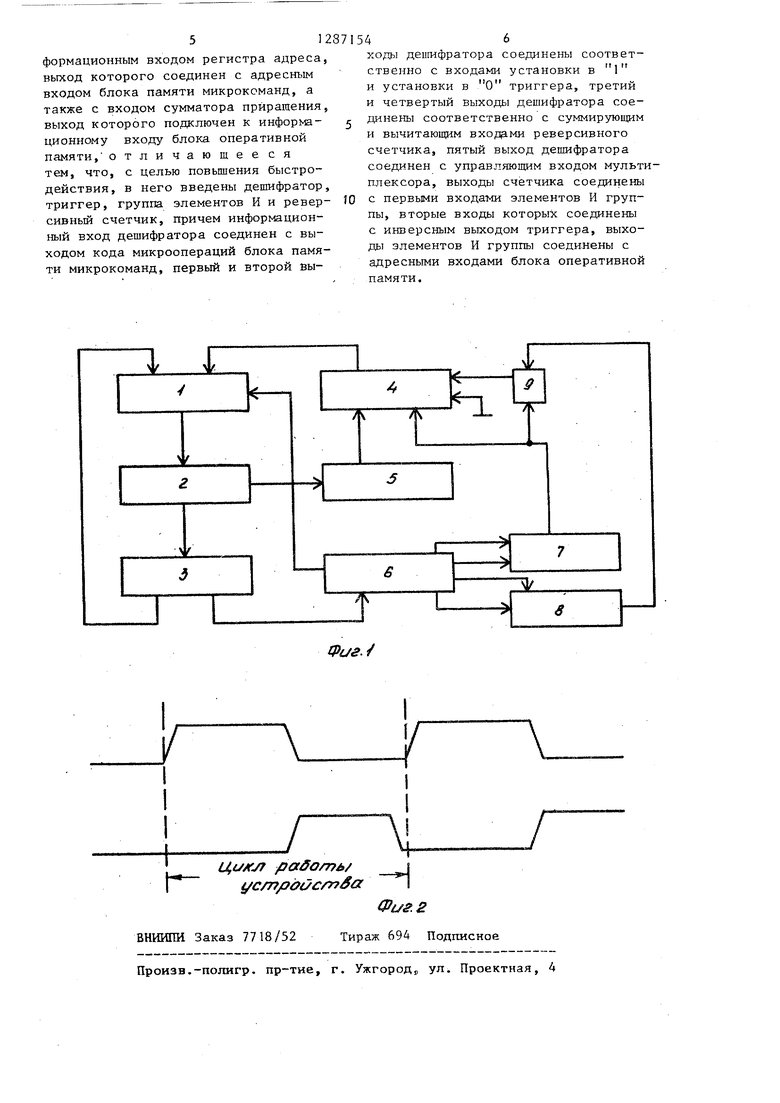

На фиг.1 представлена структурная схема предлагаемого устройства; на фиг.2 - последовательность синхроимпульсов, необходимая для синхронизации устройства.

Устройство содержит мультиплексор 1, регистр 2 адреса, блок 3 памяти микрокоманд, блок 4 оперативной памяти, сумматор 5 приращения, дешифратор 6, триггер 7, реверсивный счетчик 8, группу элементов И 9. Сумматор 5 приращения представляет собой схему, реализующую функцию увеличения входной информации на постоянную величину.

Синхронизация устройства осуществляется от двухфазного генератсэра, вырабатывающего две синхропоследова- тельности Т и Т..

Устройство работает следзпощим образом.

В набор микрокоманд устройства кроме микрокоманд Переход к ПОДПРО- грамме и Возврат из подпрограммы вводятся микрокоманды Переход в главную программу и Возврат в программу, для обработки которых, собственно, и предназначены дешифратор 6, триггер 7, реверсивный счетчик 8 и группа элементов И 9.

Цикл работы устройства начинается с появлением переднего фронта фазы Т.( . По переднему фронту Т производится запись в регистр 2 адреса очередной микрокоманды. С некоторой задержкой от переднего фронта Т, с выходов блока 3 памяти микрокоманд появляется код микрокоманды, который поступает на дешифратор 6 и первый вход мультиплексора Г, Фаза Т служит для задания режима работы блока 4 оперативной памяти и управления реверсивным счетчиком 8 и триггером 7. На всем протяжении положительного импульса фазы Т блока 4 находятся в режиме записи и переписывают со- , держимое регистра 2, увеличенное на единицу, все остальное время блок 4 находится в режиме считывания. Запись и чтение осуществляются в ячейке, адрес которой задается реверсивным счетчиком 8, если триггер 7 сбро

шен в О и в ячейке с адресом О, если триггер 7 установлен в 1.

Увеличение и уменьшение содержимого реверсивного счетчика 8, а также установка и сброс триггера 7 осуществляются задним фронтом фазы Т , т.е. их состояние изменяется в конце цикла работы устройства после записи в блок 4 оперативной памяти.

Рассмотрим работу устройства при переходе к подпрограмме. Микрокоманда Переход к подпрограмме занимает в блоке памяти микрокоманд одно слово и содержит код микрооперации и 5 адрес первой микрокоманды подпрограммы. Допустим содержимое регистра 2 равно А, это - адрес микрокоманды Переход к подпрограмме. Адрес первой микрокоманды подпрограммы В. При этом содержимое реверсивного счетчика 8 равно О и триггер 7 также обнулен, что соответствует выбору в блоке 4 ячейки с адресом 0.

Сумматор ,5 приращения производит приращение содержимого регистра 2 и, на информационный первый вход блока 4 поступит код А+1. По фазе Т этот

0

5

0

код запишется в нулевую ячейку блока 4, что соответствует запоминанию

адреса возврата. С выхода кода микроопераций блока 3 памяти микрокоманд на вход дешифратора 6 поступает комбинация, соответствующая разрешению приращения реверсивного счетчика 8 5 на единицу.

По заднему фронту фазы Т, содержимое счетчика В становится равным единице, а в ячейке с адресом О за0 поминается адрес возврата. С появлением на выходе блока 3 памяти микрокоманд микрокоманды Переход к подпрограмме мультиплексор 1 переключает вход регистра 2 с выхо5 да блока 4 на адресный выход блока

3памяти микрокоманд. Тогда в следующем цикле в регистре 2 по переднему фронту фазу Т будет загружен код Б. В первую ячейку блока 4 запишется код В+1 и произойдет обратное переключение мультиплексора 1.

Таким образом, за один цикл работы устройства произоишо запоминание адреса возврата в ячейке блока

4и переход к первой микрокоманде подпрограммы. Переход из этой подпрограммы в следующую реализуется аналогично. Адреса возврата будут храниться в нулевой и перясл ячейке0

5

блока 4, а содержимое реверсивного счетчика 8 станет равным двум.

Возврат из подпрограммы происходит по микрокоманде Возврат из подпрограммы, являющейся последней микрокомандой подпрограммы.

Допустим, обрабатьшается подпрограмма первого уровня вложенности, начальный адрес которой равен В, по адресу В+3 находится Возврат, содержимое реверсивного счетчика 8 равно единице, адрес возврата хранится в ячейке блока 4 с адресом 0. По переднему фронту фазы Т адрес микрокоманды Возврат В+3 заносится в регистр 2 и с некоторой задержкой на выходе блока 3 памяти микрокоманд появляется, код микрокоманды Возврат, На вход деишфратора 6 поступает кодовая комбинация, соответствующая разрешению уменьшения содержимого реверсивного счетЧика 8 на единицу, и к началу следующего такта из блока 4 будет считываться ячейка с адресом О, в которой хранится адрес возврата, для нашего примера равный А+1, который в следующем цикле по переднему фронту (1йзы И запишется в регистр 2, При отработке микрокоманды Возврат из подпрограммы по фазе Т в первую ячейку блока 4 был занесен код В+4, это свойство используется в дальнейшем для обработки микрокоманд Переход в главную программу и Возврат в подпрограмму.

Дпя реализации микрокоманд Переход в главную программу и Возврат в подпрограмму служит триггер 7, который коммутирует адресные блока 4 через группу элементов И 9 с выходами счетчика 8, Если триггер 7 сброшен, на адресный вход подается содержимое реверсивного счетчика 8, при ; .тановке триггера 7 адрес становится равным О, что соответствует обращению к ячейке блока 4, в которой хранится адрес возврата в главную программу. Вставив в подпрограмму любого уровня вложености микрокоманду Переход в главную программу, можно временно прервать ее выполнение и вернуться в главную программу, при этом содержимое реверсивного счетчика 8 не изменится, а в ячейке блока 4 с адресом, на который указывает реверсив1гый счетчик 8, сохранится адрес микрокомандь1, следуюпцтй за j HCTpyKUHei) Переход в главную nporpaMNfy, что позволяет в свою очередь передать управление из главной программы в подпрограм- 2 му, из которой произошел переход.

Допустим, выполняется подпрограмма второго уровня вложенности по адресу С в этой подпрограмме находится микрокоманда Переход в главO ную программу. По переднему фронту фазы Т адрес С заносится в регистр 2, и с некоторой задержкой на выходе блока 3 памяти появится код микрокоманды Переход в главную программу

5 При этом на вход дешифратора 6 поступает кодовая комбинация, разрешая установку триггера 7 в единичное состояние. Установка триггера производится по заднему фронту фазы

0 Т.. Заметим, что в ячейке блока 4, на которую указывает реверсивный счетчик 8, после окончания фазы Т будет храниться код, равный C+I, т.е. адрес следующей микрокоманды

5 подпрограммы. Установка триггера 7 в единичное состояние приводит к поступлению на адресные входы блока 4 логического нуля. Таким образом, по окончании фазы, в которой хранит0 Сея адрес возврата в главную программу. В след- тоще цикле этот адрес по переднему фронту фазы Т, запишется в регистр 2.

После выполнения некоторых дейст5 ВИЙ в главной программе (как правило это передача переменных параметров в устройство) можно вернуться обратно в подпрограмму на адрес С Это происходит по микрокоманде Воз0 врат в подпрогра1 му, при выполнении которой производится установка триггера в нулевое состояние, что ведет к поступлению на адресные входы блока 4 содержимого реверсивного счетчи5 ка 8 через группу элементов Н 9,

Формула изобретения

Устройство микропрограммного уп- 0 равления, содержащее мультиплексор, регистр адреса, блок памяти микрокоманд, блок оперативной памяти и сумматор приращения, причем первый информационный вход мультиплексора 5 соединен с адресным выходом блока памяти микрокоманд, второй информационный вход мультиплексора соединен с выходом блока оперативной памяти, выход мультиплексора сое.цинен с ин512

формационным входом регистра адреса, выход которого соединен с адресным входом блока памяти микрокоманд, а также с входом сумматора приращения, выход которого подключен к информа- ционному входу блока оперативной памяти, отличающееся тем, что, с целью повышения быстродействия, в него введены дешифратор, триггер, группа элементов И и ревер- сивньш счетчик, причем инфop и.циoн- ный вход дешифратора соединен с выходом кода микроопераций блока памяти микрокоманд, первый и второй выФаг./

J/

t/c/rtpoacrrfSa

Цс/ЛГУ p XSO/T7&/ I

ВНИИПИ Заказ 7718/52 Тираж 694 Подписное Произв.-полигр. пр-тие, г. Ужгород ул. Проектная, 4

46

ходы дешифратора соединены соответственно с входами установки в 1 и установки в О триггера, третий и четвертый выходы дешифратора соединены соответственно с суммируюшим и вычитающим входами реверсивного счетчика, пятый выход дешифратора соединен с управляющим входом мультиплексора, выходы счетчика соединены с первыми входами элементов И группы, вторые входы которых соединены с инверсным выходом триггера, выходы элементов И группы соединены с адресными входами блока оперативной памяти.

У

Фаг 2

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство микропрограммного управления | 1988 |

|

SU1536380A1 |

| Микропрограммное устройство управления | 1981 |

|

SU1062701A1 |

| Многоканальное устройство для сопряжения ЭВМ | 1988 |

|

SU1695311A1 |

| Устройство для контроля цифровых блоков | 1988 |

|

SU1661768A1 |

| Процессор для мультипроцессорной системы | 1985 |

|

SU1295410A1 |

| Процессор с микропрограммным управлением | 1983 |

|

SU1149273A1 |

| Устройство для сопряжения центрального процессора с группой арифметических процессоров | 1984 |

|

SU1254495A1 |

| Процессор программируемого контроллера | 1988 |

|

SU1550515A2 |

| Микропрограммное устройство управления | 1987 |

|

SU1490676A1 |

| КОНТРОЛЛЕР | 1991 |

|

RU2012043C1 |

Изобретение относится к вычислительной технике и может быть использовано в устройствах управления ЭВМ. Целью изобретения является повышение быстродействия устройства. Устройство содержит нультиплексор, регистр адреса, блок памяти микрокоманд, блок оперативной памяти, блок приращения, депшфратор, триггер, реверсивный счетчик, группу элементов И. Поставленная цель достигается за счет обеспечения перехода из подпрограммы любого уровня сложности в главную программу с дальнейшим возвратом в подпрограмму. 2 ил. с S (Л N9 СХ) СП

| Устройство для управления подпрограммами | 1973 |

|

SU477411A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для управления обращением к стандартным подпрограммам | 1974 |

|

SU544965A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| УСТРОЙСТВО для ВКЛЮЧЕНИЯ МУФТЫ ПРЕССА | 0 |

|

SU390979A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-01-30—Публикация

1985-01-24—Подача