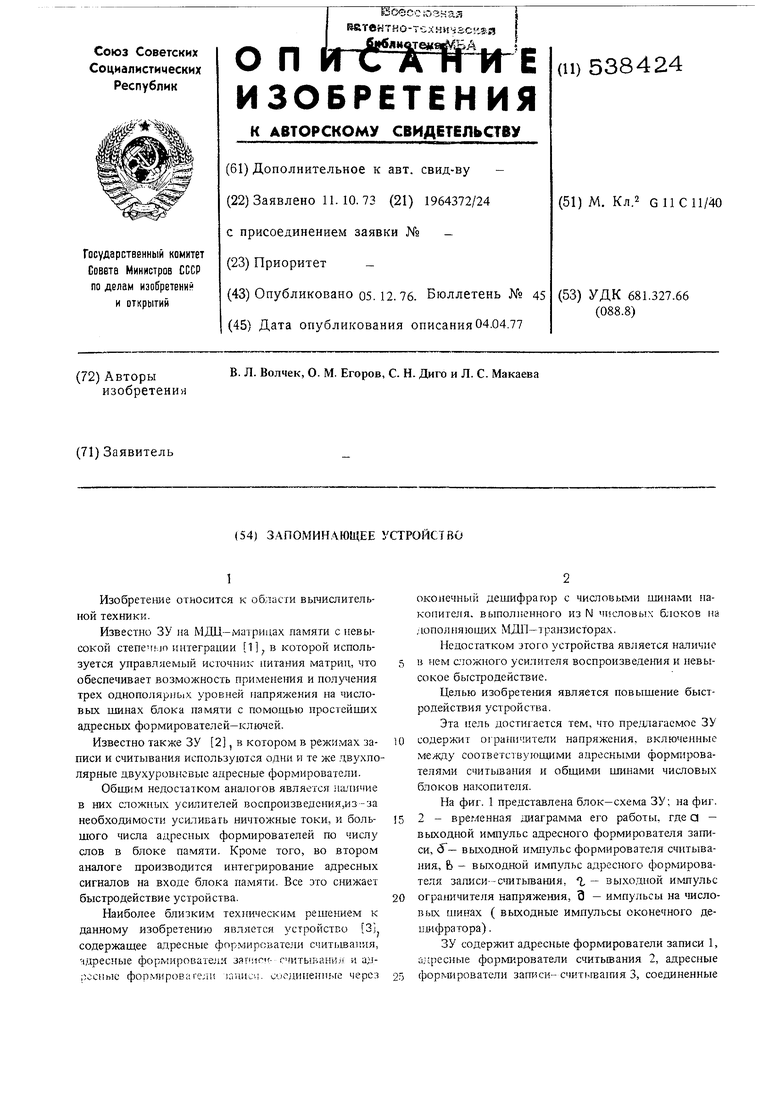

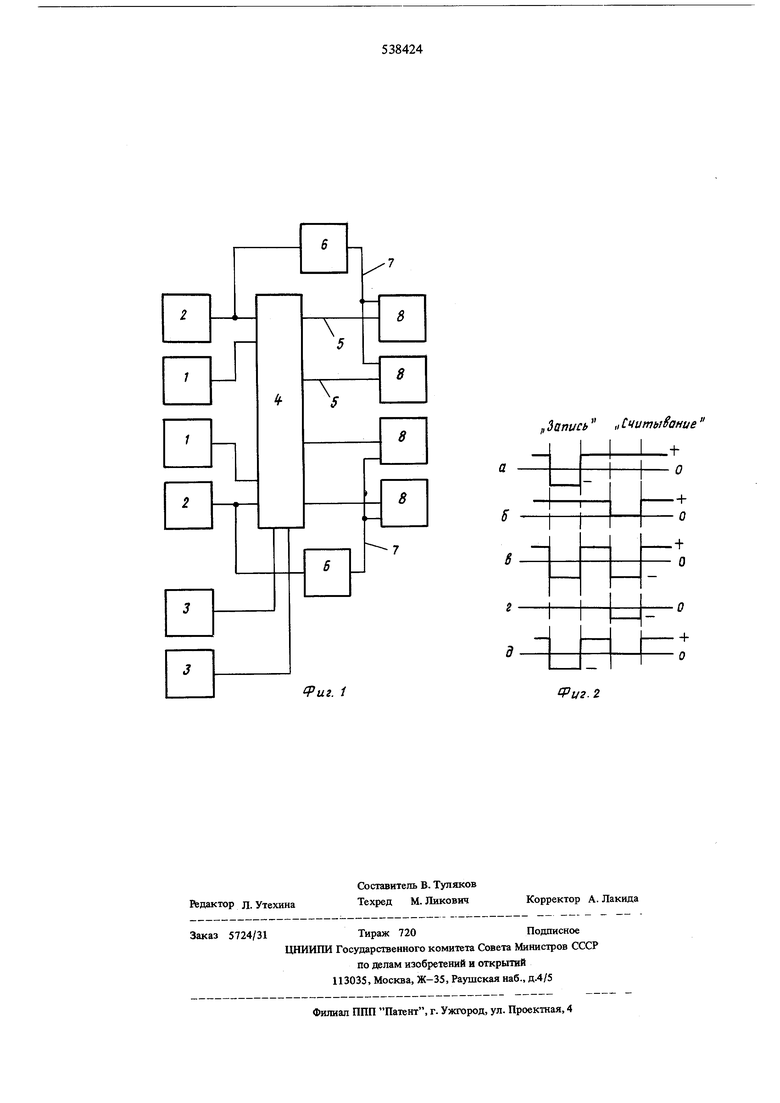

(54) ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО выходами со входагж оконечного дешифратора 4, выходы которого подсоединены к числовым шинам 5, и ограничители напряжения б, через которые адресные формирователи считьшания подсоединены к общим шинам 7 числовых блоков накопителя 8. Устройство работает следуюшим образом. В режиме на выходах всех адресных формирователей 1-3, а, следовательно, и на числовых шинах 5 поддерживается высокий положительный потенциал, обеспечивающий хранение информации в числовых блоках 8, а на выходе ограничителей напряжения 6 - нулевой уровень. В режиме записи срабатывает один из формирователей записи 1 и один из формирователей записи- считьшания 3. От воздействия этих сигналов на выбранной шине 5 устанавливается отрицательньш потенш1ал Э, обеспечивающий запись информации ячейки памяти при номинальном напряжении питания. В режиме считывания срабатьтает один из формирователей считьтания 2 и один из формирователей записи-считьтания 3, которые обеспечивают на своих выходах соответственно сигналы 5 и В . От воздействия этих сигналов на выбранной шине 5 устанавливается меньший, чем при записи, отрицательньш потенциал, обеспечивающий считывание информации без разрушения. Одновременно соответствующий ограничитель напряжения 6 понижает потенциал общей шины 7 числовых блоков накопителя 8 до определенной величины. Кратковременное возрастание напряжения питания во время считьшания приводит к возрастанию величины считанного тока и существенно увеличивает надежность считьшания без разрущения информации. Это позволяет еще более понизить потенциал на выбранной числовой шине накопителя во время считьшания, т.е. вызвать дальнейшее значительное величение считанного тока. В результате схема силителя воспроизведения существенно упрощается, перезаряд паразитной емкости разрядной шины лока накопителя возросшим током считывания быстряется и быстродействие ЗУ в режиме считыания резко возрастает. Технико-экономический эффект от использоваия изобретения достигается за счет повышения надежности и быстродействия работы устройства и упрощения схем управления. Формула изобретения Запоминающее устройство, содержащее адресные формирователи считьшания, адресные формирователи записи-считьтания и адресные формирователи записи, соединенные через оконечный дешифратор с числовыми шинами накопителя, вьшолненного из N числовых блоков на дополняющих МДП-транзисторах, отличающееся тем, что, с целью повышения быстродействия устройства, оно содержит ограничители напряжения, включенные между соответствующими адресными формирователями считьшания и общими щинами числовых блоков накопителя. Источники информации, принятые во внимание при экспертизе: 1.Белов В. М. и др. Быстродействующее ОЗУ на интегральных микросхемах Автометрия, 1973 г, № 3. 2.Гордонов А.Ю. и др. Схемотехника полупроводниковых ЗУ на комплементарных МДП-структурах. Сб. статей Запоминающие устройства под ред. Л. П. Крайзмера, изд. Энергия, 1974 г, вьш. 4. 3.Волчек В. Л. и др., заявка на изобретение № 1891977, 1972 г, по которой принято решение о вьщаче авторского свидетельства 18.1.74г.

иг. 1

,, Запись ,1 Считывание

Риг.2

| название | год | авторы | номер документа |

|---|---|---|---|

| Логическое запоминающее устройство | 1979 |

|

SU864336A1 |

| Полупроводниковое запоминающее устройство | 1988 |

|

SU1674261A1 |

| Запоминающее устройство | 1983 |

|

SU1115105A1 |

| Полупроводниковое запоминающее устройство | 1978 |

|

SU748508A1 |

| Программируемое постоянное запоминающее устройство | 1980 |

|

SU886055A1 |

| Буферное запоминающее устройство | 1981 |

|

SU993333A1 |

| Запоминающее устройство | 1976 |

|

SU690564A1 |

| Запоминающее устройство | 1980 |

|

SU911614A1 |

| Буферное запоминающее устройство | 1984 |

|

SU1226530A1 |

| Запоминающее устройство системы 2д с неразрушающим считыванием информации на многоотверстных ферритовых элементах | 1977 |

|

SU693438A1 |

Авторы

Даты

1976-12-05—Публикация

1973-10-11—Подача