В основу действия регистра сдвига положена способность триггер БОй ячейки сохранить информацию в течение некоторого ер-ем ени при выключенном источнике пнтания и не разрушать -ее при его включении. При этом одновременно используются свойства как триггериой, так и динамической памяти.

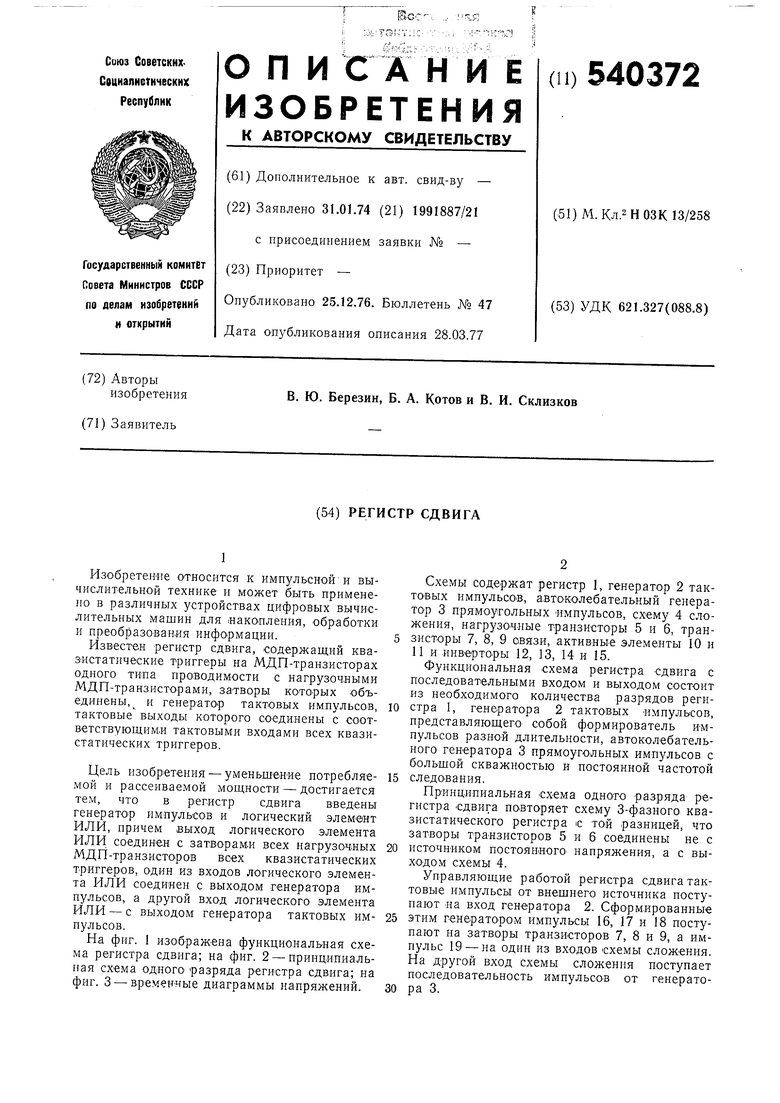

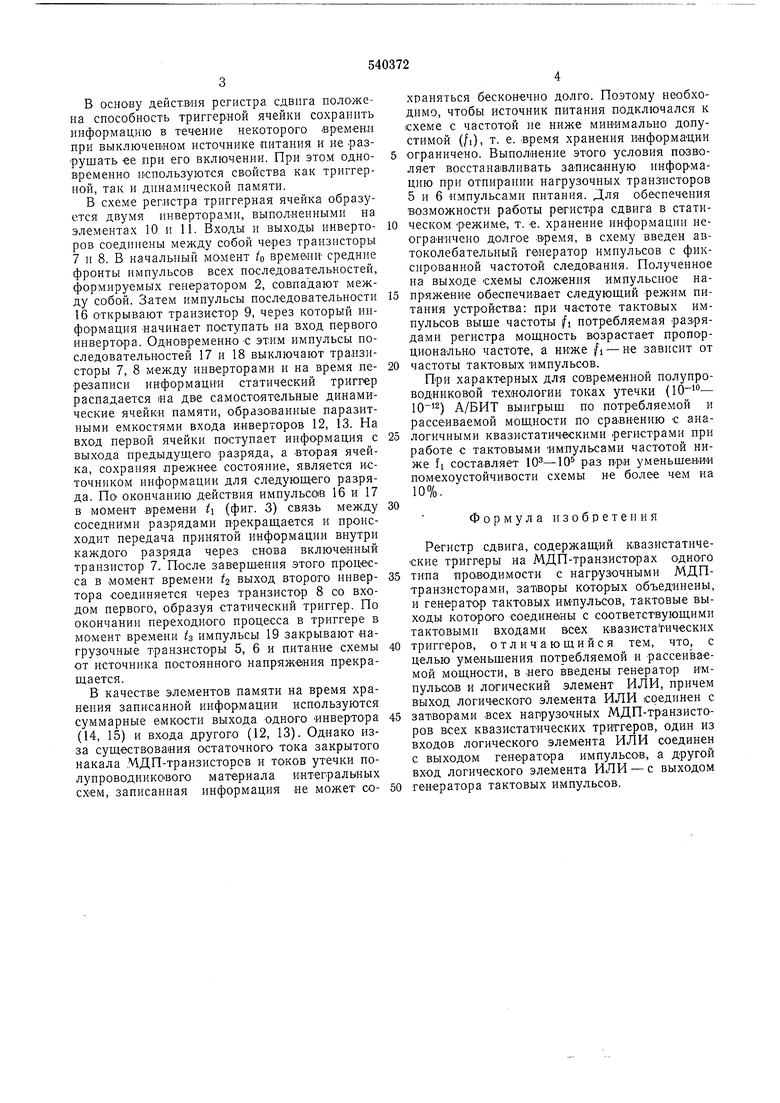

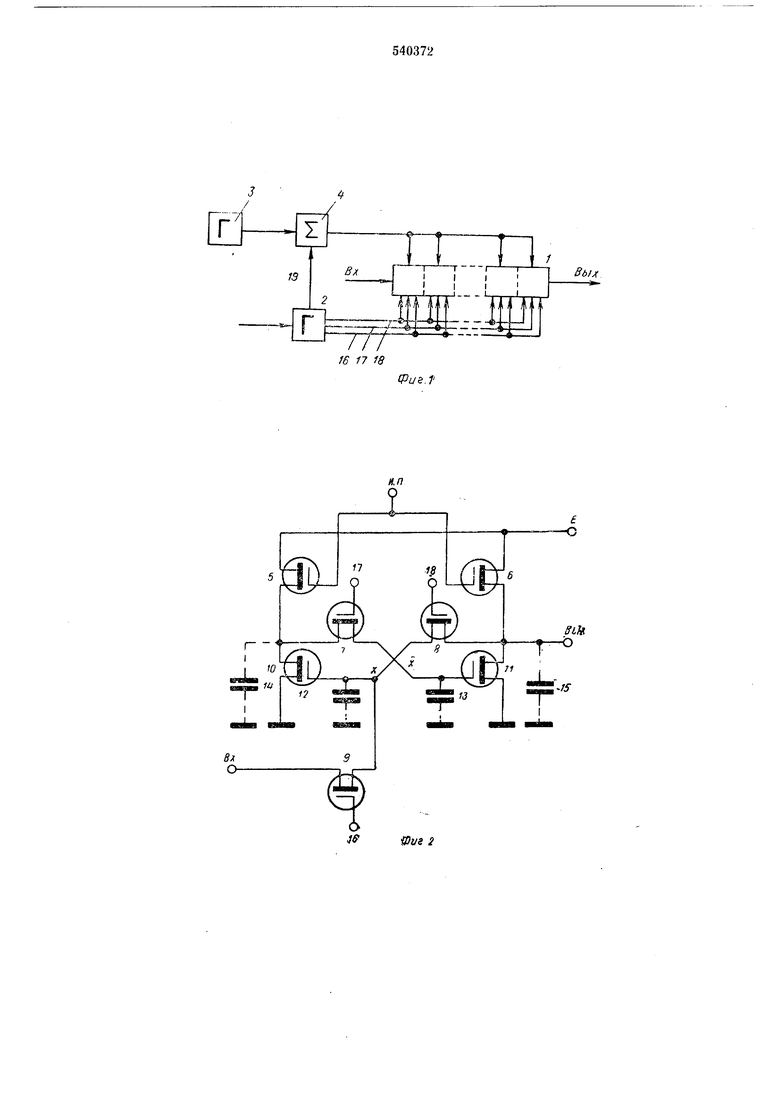

В схеме регистра триггерная ячейка образуется двумя инверторами, выполненными на элементах 10 и 11. Входы и выходы инверторов соединены между собой через транзисторы 7 и 8. В начальный момент to времени средние фронты импульсов всех последовательностей, формируемых генератором 2, совпадают между собой. Затем импульсы последовательности 16 открывают транзистор 9, через который информация «ачинает поступать на вход первого инвертора. Одновременно е этим импульсы последовательностей 17 и 18 выключают тра-нзисторы 7, 8 между инверторами и на время перезаписи ин-формациИ статический триггер распадается иа две самостоятельные динамические ячейки памяти, образованные паразитными емкостями входа инверторов 12, 13. На вход первой ячейки поступает информация с выхода предыдущего разряда, а вторая ячейка, сохраняя прежнее состояние, является источником информации для следующего разряда. По окончанию действия импульсов 16 и 17 в момент времени t (фиг. 3) связь между соседними разрядами прекращается и происходит передача принятой информации внутри каждого разр-яда через снова включенный транзистор 7. После заверщения этого процесса в момент времени 2 выход второго инвертора соединяется через транзистор 8 со входом первого, образуя статический триггер. По окончании переходного процесса в триггере в момент времени ts импульсы 19 закрывают иагрузочные транзисторы 5, 6 и питание схемы от источника постоянного напряжения прекращается.

В качестве элементов памяти на время хранения записанной информации используются суммарные емкости выхода одно-го инвертора (14, 15) и входа другого (12, 13). Однако изза существования остаточного тока закрытото накала МДП-транзисторов и токов утечки полупроводникового материала интегральных схем, записанная информация не может сохраняться бесконечно долго. Поэтому необходимо, чтобы источник питания подключался к схеме с частотой не ниже минимально допустимой (|i), т. е. время хранения информации ограничено. Выполнение этого условия позволяет восстанавливать записанную информацию при отпирании нагрузочных транзисторов 5 и 6 импульсами питания. Для о-беспечения возможности работы регистра сдвига в статическом режиме, т. е. хранение информации неограничено долгое время, в схему введен автоколебательный генератор импульсов с фиксированной частотой следования. Полученное на выходе схемы сложения импульсное напряжение обеспечивает следующий режим питания устройства: при частоте тактовых импульсов выще частоты i потребляемая разрядами регистра мощность возрастает пропорционально частоте, а ниже fi - не зависит от

частоты тактовых импульсов.

При характерных для современной полупроводниковой технологии токах утечки ( ) А/БИТ выигрыщ по потребляемой и рассеиваемой мощности по сравнению с аналогичными квазистатическими регистрами при работе с тактовыми импульсами частотой ниже fi составляет раз при уменьщевии помехоустойчивости схемы не более чем на 10%.

Формула изобретения

Регистр сдвига, содержащий квазистатические триггеры на МДП-транзисторах одного

типа проводимости с нагрузочными МДПтранзисторами, затворы которых объединены, и генератор тактовых им-пульсов, тактовые выходы которого соединаны с соответствующими тактовыми входами всех квазистатических

триггеров, отличающийся тем, что, с целью уменьшения потребляемой и рассеиваемой мощности, в него введены генератор ИМпульоов и логический элемент ИЛИ, причем выход логического элемента ИЛИ соединен с

затвор-ами всех нагрузочных МДП-транзисторов всех квазистатических триггеров, один из входов логического элемента ИЛИ соединен с выходом генератора импульсов, а другой вход логического элемента ИЛИ - с выходом

генератора тактовых импульсов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Элемент памяти для регистра сдвига | 1979 |

|

SU832600A1 |

| ДВУХКАСКАДНЫЙ ДИНАМИЧЕСКИЙ СДВИГОВЫЙ РЕГИСТР | 2014 |

|

RU2542898C1 |

| Ячейка памяти для регистра сдвига | 1977 |

|

SU680055A2 |

| ДВУХТАКТНЫЙ ДИНАМИЧЕСКИЙ РЕГИСТР СДВИГА | 2014 |

|

RU2556437C1 |

| Двухтактный сдвигающий регистр | 1968 |

|

SU736172A1 |

| Элемент памяти для динамического регистра сдвига | 1977 |

|

SU684617A1 |

| ДВУХТАКТНЫЙ СДВИГАЮЩИЙ РЕГИСТР | 2014 |

|

RU2549136C1 |

| Ячейка памяти для регистра сдвига | 1972 |

|

SU503295A1 |

| АССОЦИАТИВНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО НА МДП-ТРАНЗИСТОРАХ | 1973 |

|

SU408374A1 |

| СДВИГОВЫЙ РЕГИСТР | 2013 |

|

RU2522306C1 |

1Ь

17

Авторы

Даты

1976-12-25—Публикация

1974-01-31—Подача