(54) ЭЛЕМЕНТ ПАМЯТИ ДЛЯ РЕГИСТРА СДВИГА

| название | год | авторы | номер документа |

|---|---|---|---|

| Регистр сдвига | 1976 |

|

SU587507A1 |

| Ячейка памяти для регистра сдвига | 1977 |

|

SU680055A2 |

| Элемент памяти для регистра сдвига | 1978 |

|

SU706880A1 |

| Ячейка памяти для регистра сдвига | 1975 |

|

SU570108A1 |

| Регистр сдвига | 1974 |

|

SU540372A1 |

| Квазистатическое счетное устройство на МДП-транзисторах | 1986 |

|

SU1319255A1 |

| Регистр сдвига | 1987 |

|

SU1476535A1 |

| Ячейка памяти для регистра сдвига | 1983 |

|

SU1125655A1 |

| Ячейка памяти | 1979 |

|

SU1022222A1 |

| Ячейка памяти для регистра сдвига | 1980 |

|

SU902075A1 |

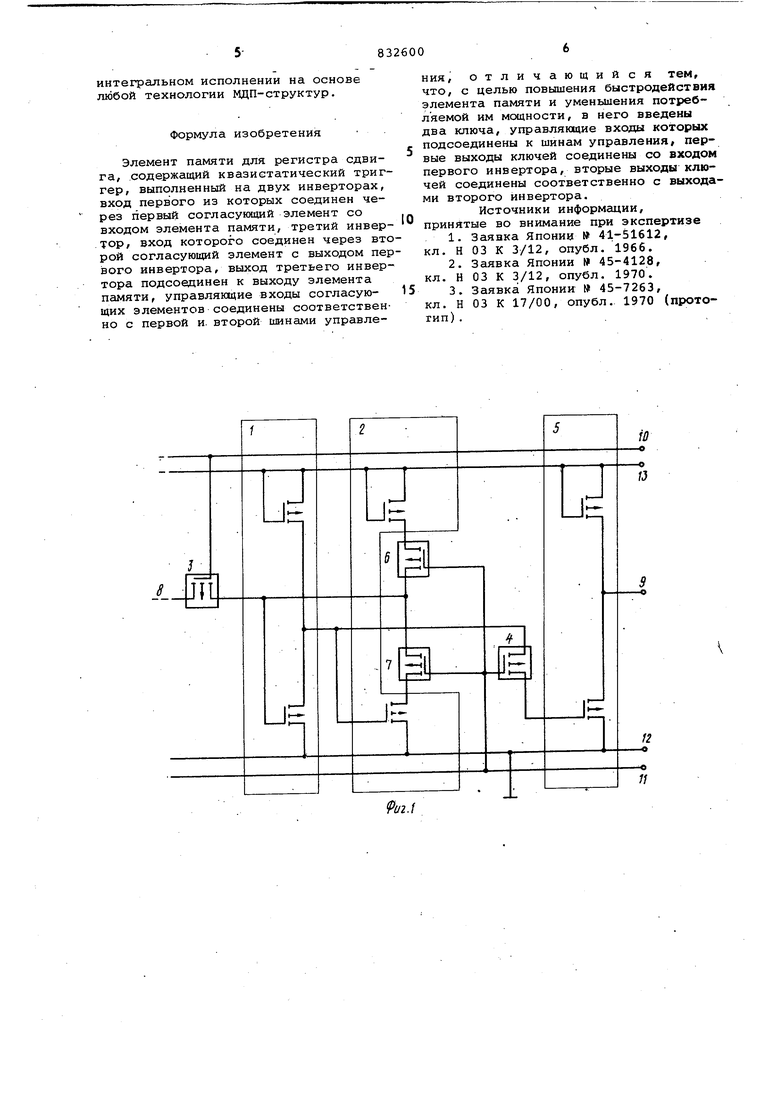

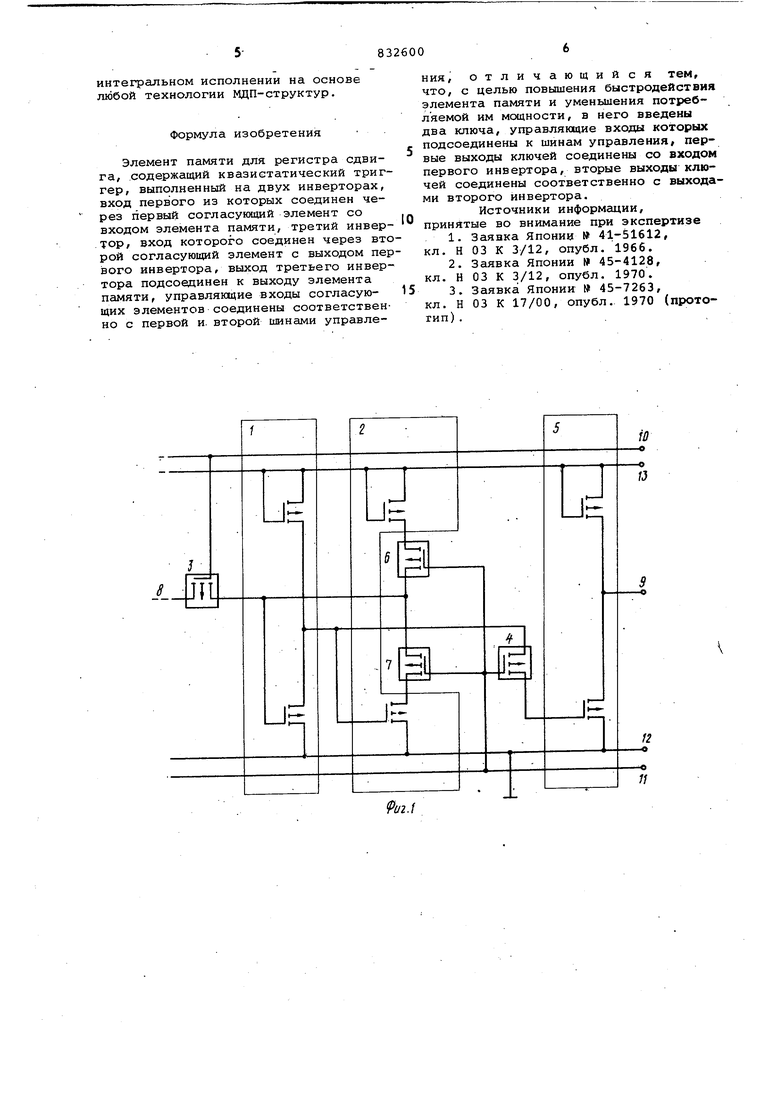

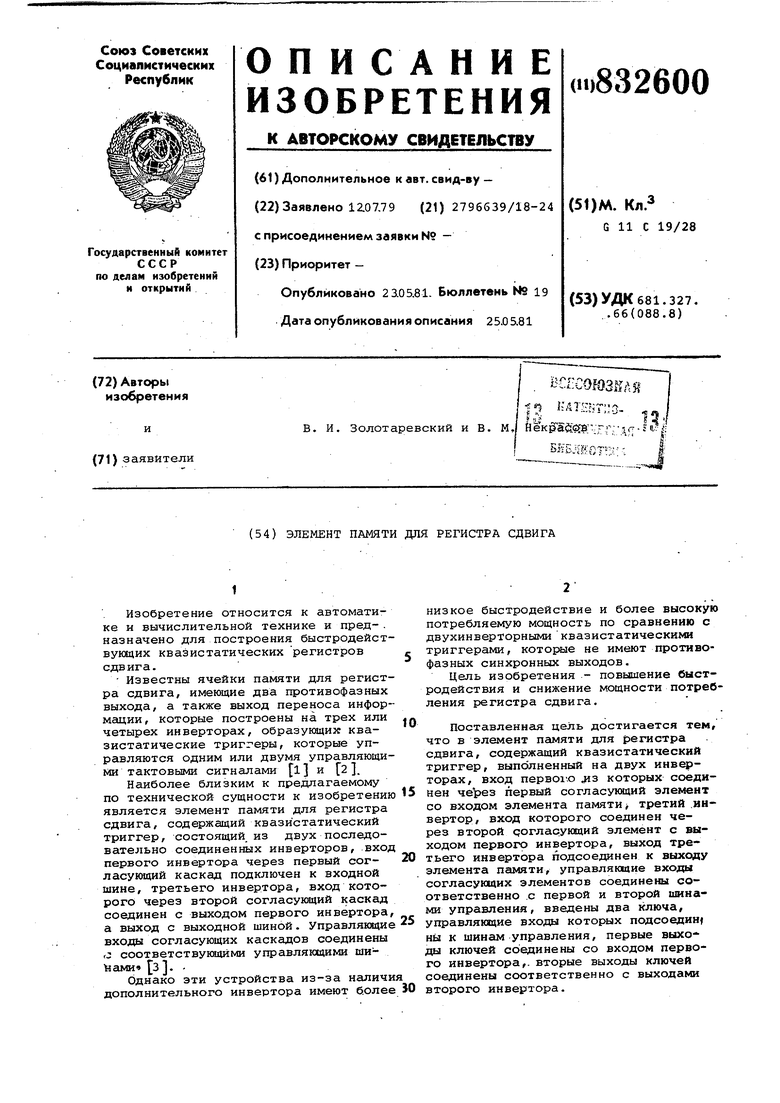

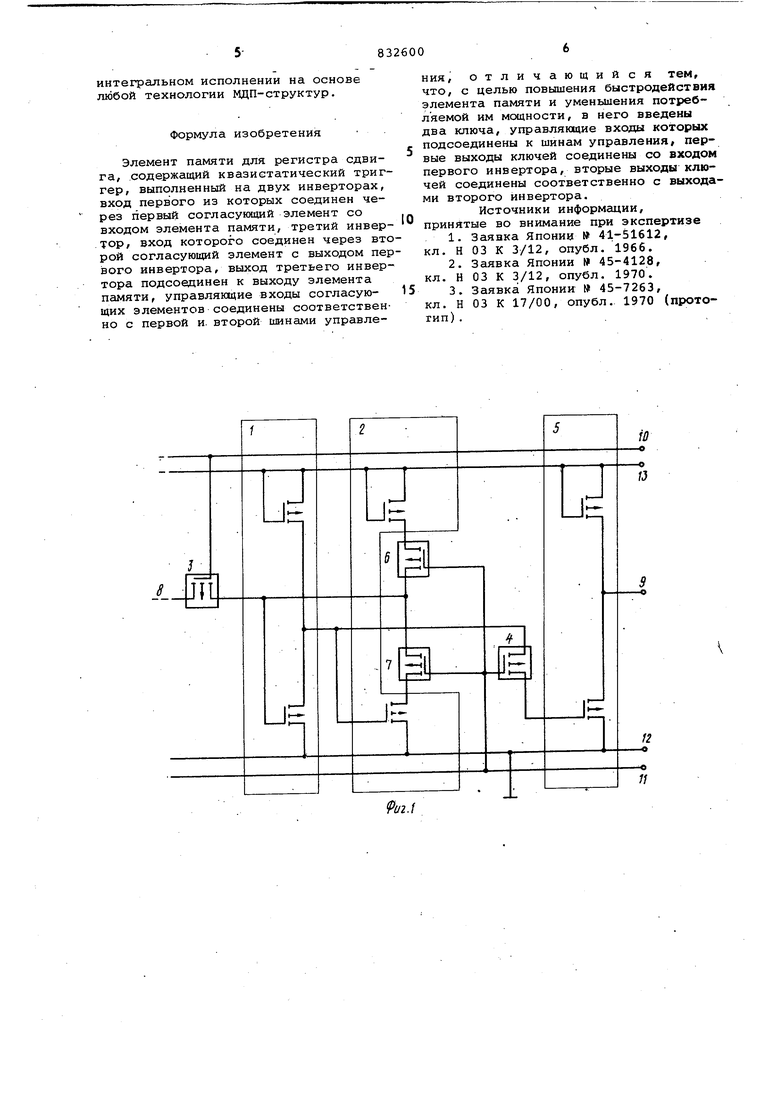

Изобретение относится к автоматике и вычислительной технике и пред-. назначено для построения быстродействующих квазистатических регистров сдвига. - Известны ячейки памяти для регистра сдвига, имеющие два противофазных выхода, а также выход переноса информации , которые построены на трех или четырех инверторах, образующих квазистатические триггеры, которые управляются одним или двумя управляющими тактовыми сигналами l и 2. Наиболее близким к предлагаемому по технической сущности к изобретению является элемент памяти для регистра сдвига, содержащий квазистатический триггер, состоящий из двух последовательно соединенных инверторов, вход первого инвертора через первый согласующий каскад подключен к входной шине, третьего инвертора, вход которого через второй согласующий каскад соединен с выходом первого инвертора а выход с выходной шиной. Управляющие входы согласующих каскадов соединены (.; соответствующими управляющими шинами з. Однако эти устройства из-за наличи дополнительного инвертора имеют б.олее низкое быстродействие и более высокую потребляемую мощность по сравнению с двухинверторнымиквазистатическими триггерами, которые не имеют противофазных синхронных выходов. Цель изобретения - повышение быстродействия и снижение мощности потребления регистра сдвига. Поставленная цель достигается тем, что в элемент памяти для регистра сдвига, содержащий квазистатический триггер, выполненный на двух инвед торах, вход перво1.о лз которых соединен первый согласующий элемент со входом элемента памяти j третий .инвертор, вход которого соединен через второй согласующий элемент с выходом первого инвертора, выход третьего инвертора подсоединен к выходу элемента памяти, управлякшие входы согласующих элементов соединены соответственно .с первой и второй шинами управления, введены два ключа, управляющие входы которых подсоеяин| ны к шинам управления, первые выходы ключей соединены со входом первого инвертора,, вторые выходы ключей соединены соответственно с выходами второго инвертора. На фиг. 1 изображена функциональная схема предложенного устройства выполненного на МДП-транэисторах одного типа проводимости; на фиг. 2 - вариант.выполнения предложенного устройства, выполненного на дополнякяцих МДП-транэисторах. Устройство .содержит первый и второй инверторы: и 2, первый и второй согласукщий элементы 3 и 4 третий инвертор 5, ключи б и 7, вход 8 и вы ход 9 элемента памяти,, шины 1р. и 11 управления, шину 12 нулевого потенци ала и шину 13 питания. Устройство работает следующим образом. На шины 10 и 11 подаются противофазные управляклцие сигналы. Рассмотрим работу регистра сдвига, выполненного на р-канальных МДПтранзисторах (фиг. 1). Питание регистра сдвига осуществл ется от источника напряжения отрицательной полярности (источник подклЮчен к шине 13 питания), В режиме хранения информации на вторую шину 11 управления подается отрицательное напряжение,поддерживающее в открытом состоянии второй согласующий элемент 4 и ключи 6 и 7 а на первую шину 10 управления подается напряжение, величина которого близка к нулю, удерживающее первый согласующий элемент 3 в закрытом состояний. При этом второй инвертор 2 находится в рабочем состоянии и образует с первым инвертором 1 триггер с непосредственными связями, а,выход третьего инвертора 5 подключ е з к, вь(,ходу первого HHBejpTopa 1.. С приходом управлякдцих сигналов на первую и вторую шины 10 и 11 уп-равления (на первую шину 10 поступает импульс отрицательной полярнос а на вторую шину 11 - нулевой сигнал), согласующий элемент 4 закрыва е.тся и отключает вход третьего ин- . вертора 5 от выхода первого инверто ра 1 , ключи 6 и 7 также закрываются и отключают соответственно управ ляющий и нагрузочный транзисторы второго инвертора 2 от входа первого инвертора 1, а согласукадий элемент 3 включается. При этом через открытый согласукщий элемент 3 вход ное напряжение поступает на вход первого инвертора 1 и переводит его в новое логическое .состояние или подтверждает его предыдущее состояние. Так как управляющий -и нагрузоч ный транзисторы второго инвертора 2 отключены, то напряжение на выходе второго.инвертора 2 устанавливается равным напряжению на входе первого инвертора 1 раньше, чем у известного устройства на величину задержки Ма его втором инверторе 2. При снятии управляющих сигналов с шин 10 и 11 управления, первый согласующий элемент 3 закрывается, а второй согласующий элемент 4 и ключи б и 7 открываются и квазистатический триггер, выполненный на инверторах 1 и 2 переходит в режим хранения информации. При построении регистра сдвига на допрлняквдих МДП-транзисторах,в квазистатическом триггере, выполненном на инверторах 1 и 2, нагрузочные транзисторы инверторов 1 и 2 выполняются п-канальными, а их затворы соединяют с соответствующими.затворами управляющих транзисторов своих инверторов (фиг. 2), При использовании в качестве ключей 6 и 7 МДП-транзисторов с одинаковым типом проводимости канала, например с каналом р-типа, максимальное напряжение на выходе второго инвертора 1 по абсолютной величине ниже величины напряжения источника питания на величину порогового напряжения МДП-транзистора на котором выполнен ключ б. Это исключает возможность использования регистра сдвига при низких питающих напряжениях. Для обеспечения возможности исе пользования реги.стра сдвига, выполненного на дополняющих МДП-транзисторах, при низких питающих напряжениях ключ б выполнен на п-канальном МДПтранзисторе (фиг. 2), а его затвор подключается к первой шине 10 управления . При таком включении ключи б и 7 одновременно открываются и закрываются, обеспечивая функционирование устройства подобно квазистатическому триггеру на транзисторах одного типа проводимости. Электронные устройства выполненные на дополняющих МДП-транзисторах, в статическом состоянии мощности почти не потребляют.-Основное потребление мощности имеет место только в диНс1мическом режиме при переходе инверторов из одного состояния в другое за счет протекания сквозных токов. В предложенном элементе памяти для регистра сдвига второй инвертор 2 во время действия управляющих (тактовых) сигналов отключается. Таким образом, в каждом квазистатическом триггере регистра сдвига мощность в основном потребляется только первым 1 и третьим инверторами 3, что дает в экономию в мощности потребления около 30% по сравнению с известным устройством, выполненным на дополнякндих МДП-транзисторахВремя установления квазистатического элемента памяти для регистра сдвига меньше, чем у известного устройства, на величину задержки на его втором инверторе, что соответствует повышению быстродействия почти в 1,4 раза. Предложенный элемент пе1мяти для Jэeгиcтpa сдвига можно реализовать я интегральном исполнении на основе любой технологии МДП-структур. Формула изобретения Элемент памяти для регистра сдвига, содержащий квазистатический триггер, выпсэлненный на двух инверторах, вход первого из которых соединен через первый согласующий элемент со входом элемента памяти, третий инвертор, вход которого соединен через вто рой согласующий элемент с выходом пер вого инвертора, выход третьего инвертора подсоединен к выходу элемента памяти, управляющие входы согласующих элементов соединены соответственно с первой и. второй шинами управления, отличающийся тем, что, с целью повышения быстродействия элемента памяти и уменьшения потребляемой им мощности, в него введены два ключа, управляющие входы которых подсоединены к шинам управления, первые выходы ключей соединены со входом первого инвертора, вторые выходы ключей соединены соответственно с выходами второго инвертора. Источники информации, принятые во внимание при экспертизе 1.Заявка Японии № 41-51612, кл, Н 03 К 3/12, опубл. 1966. 2.Заявка Японии № 45-4128, кл. Н 03 К 3/12, опубл. 1970. 3.Заявка Японии 45-7263, кл. Н 03 К 17/00, опубл. 1970 (прототип) .

Фиг. 2

Авторы

Даты

1981-05-23—Публикация

1979-07-12—Подача