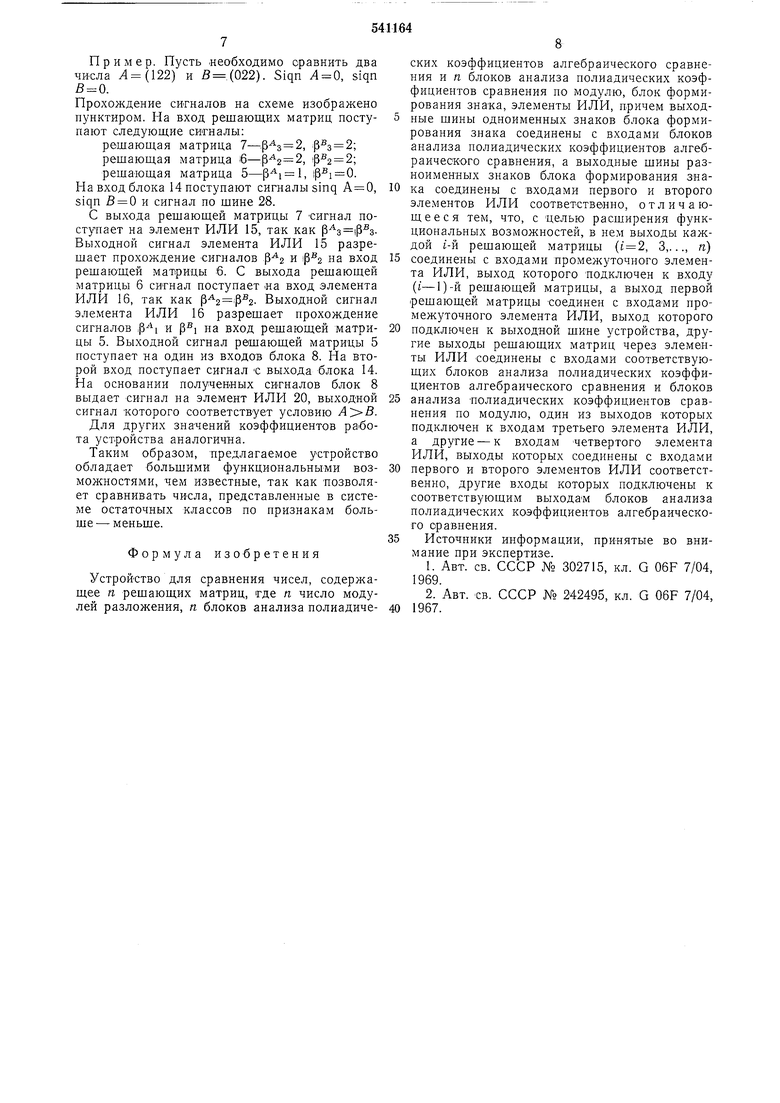

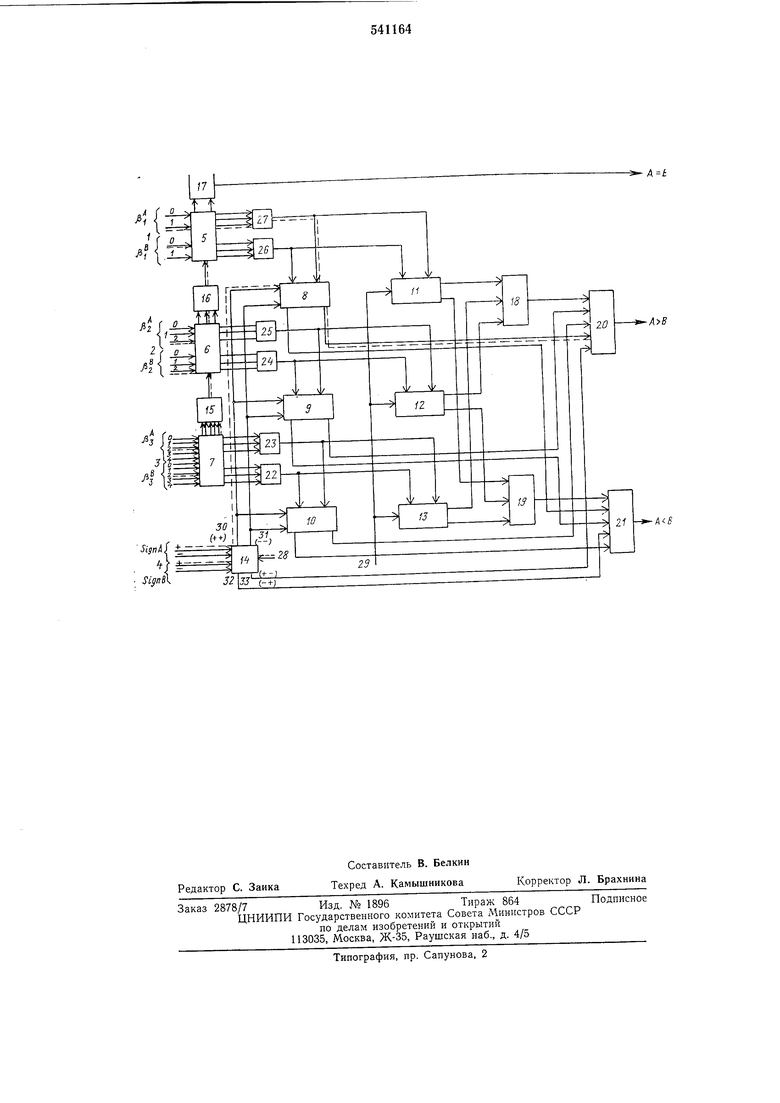

Устройство содержит входные ши«ы 1-4 для представления остатков чисел по модулям /31 2, , решающие матрицы 5, 6, 7; блоки анализа 8, 9, 10 полиадических коэффициентов алгебраического сравнения; блоки анализа И, 12, 13 полиадических коэффициентов сравнения по модулю; блок 14 формирования знака; элементы ИЛИ 15-27; шину 28 алгебраического сравнения; шину 29 сравнения по модулю; выходные шины 30-33. Устройство работает следуюш,им образом. На входы решающих матриц 5, 6, 7 поступают коэффициенты полиадического представления чисел Л и В (р1, РЗ, , Р, Р2, РЗ), а сигналы знаков siqn А и sign В поступают на вход блока 14 формирования знака. В случае алгебраического сравнения чисел по шине 28 поступает сигнал. Символы знаков кодируются следующим образом. Если число положительное, то знак кодируется О, а если число отрицательное-1. Закон функционирования блока 14 формирования знака может быть описан таблицей истинности (табл. 1). На шинах 30-33 результат представлен однопозиционным кодом. Таблица 1 Логические функции, описывающие работу блока 14 формирования знака, имеют вид: Аsiqn В; 31 :siqn Аsiqn В; Лsiqn В; Аsiqn В. Сигнал по шине 32 поступает на вход элемента ИЛИ 21, выходной Сигнал которого указывает на то, что число А 5, а сигнал по шине 33 Поступает на вход элемента ИЛИ 20, выходной сигнал которого указывает, что число . В случае, если числа А и В имеют одинаковые знаки, то сигнал по шине 30 или 31 поступает на один из входов блоков анализа 8, 9, 10. На вторые входы этих блоков поступают сигналы с выхода решающих матриц 5, 6, 7 через элементы ИЛИ 27, 26, 25, 24, 23, 22 при неравенстве коэффициентов полиадического представления чисел Л и б. Функционирование решающих матриц описывается таблицами истинности (табл. 2, 3 и 4 соответственно для решающих матриц 7, 6, 5). Сигналы Рз и РЗ поступают непосредственно на входы решающей матрицы 7. Если то выходной сигнал решающей матрицы 7 поступает на входы блоков 10, 13 через элементы ИЛИ 22, 23. В зависимости от значений сигнал с выхода блока 10 поступает на вход элемента ИЛИ 20 () или на вход элемента ИЛИ 21 (А.В). Если , то факт неравенства установить невозможно. В этом случае сигнал равенства поступает на вход элемента ИЛИ 15. Выходной сигнал элемента ИЛИ 15 разрешает подачи сигналов на вход решающей матрицы 6. Сигналы , подаются непосредственно на входрешающей матрицы 6. Если , то выходной сигнал решающей матрицы 6 поступает на вход блоков 9, 12 через элементы ИЛИ 24, 25. Анализ коэффициентов Р2 и Р2 в блоке 9 происходит аналогично анализу коэффициентов рз и Рз в блоке 10. В случае неравенства коэффициентов и сигнал с выхода блока 9 поступает на вход элементов ИЛИ 20 или 21. В случае равенства сигнал с выхода рещающей матрицы 6 поступает на вход элемента ИЛИ 16, выходной сигнал которого дает разрешение на подачу коэффициентов и на вход решающей матрицы 5. Ири неравенстве и выходной сигнал решающей матрицы 5 поступает на вход блоков 8, И через элементы ИЛИ 26, 27. Анализ и P-SI происходит аналогично анализу коэффициентов Рз, РЗ и рг, Рз. В случае равенства коэффициентов сигнал с выхода решающей матрицы 5 поступает .на вход элемента ИЛИ 17, выходная ина которого выдает сигнал равенства чисел А В. При сравнении чисел Л и Б по моулю на шину 29 поступает сигнал «Сравнение по модулю.

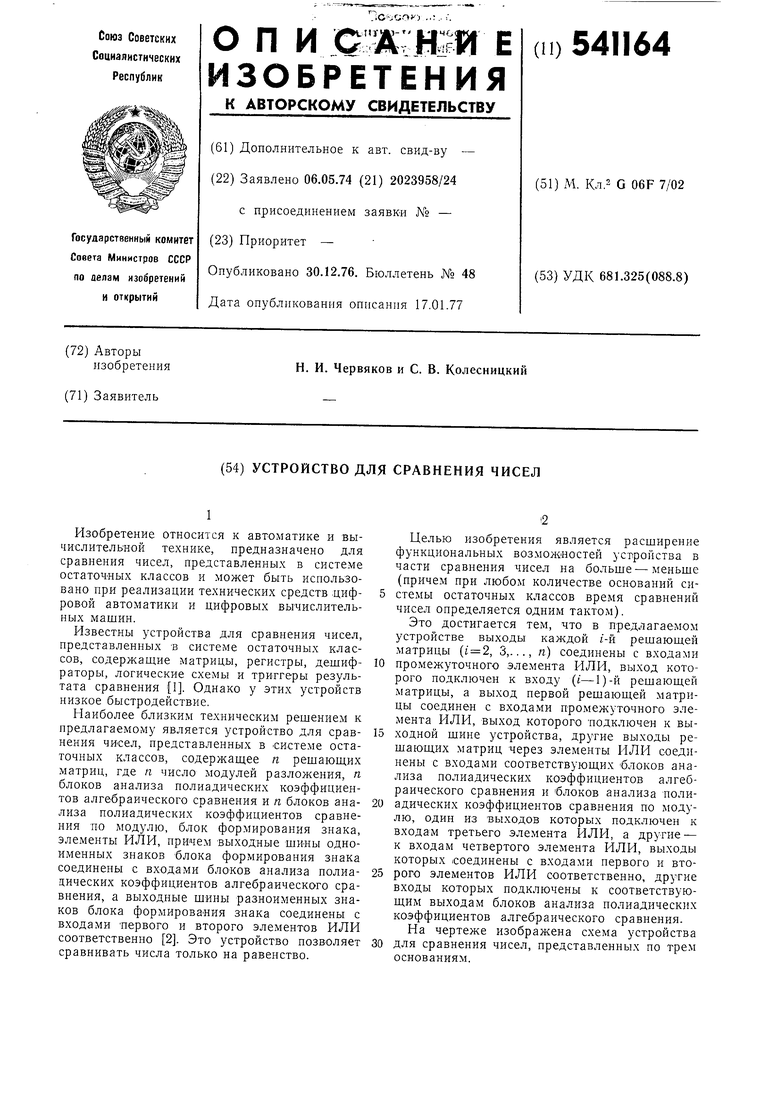

Таблица 2

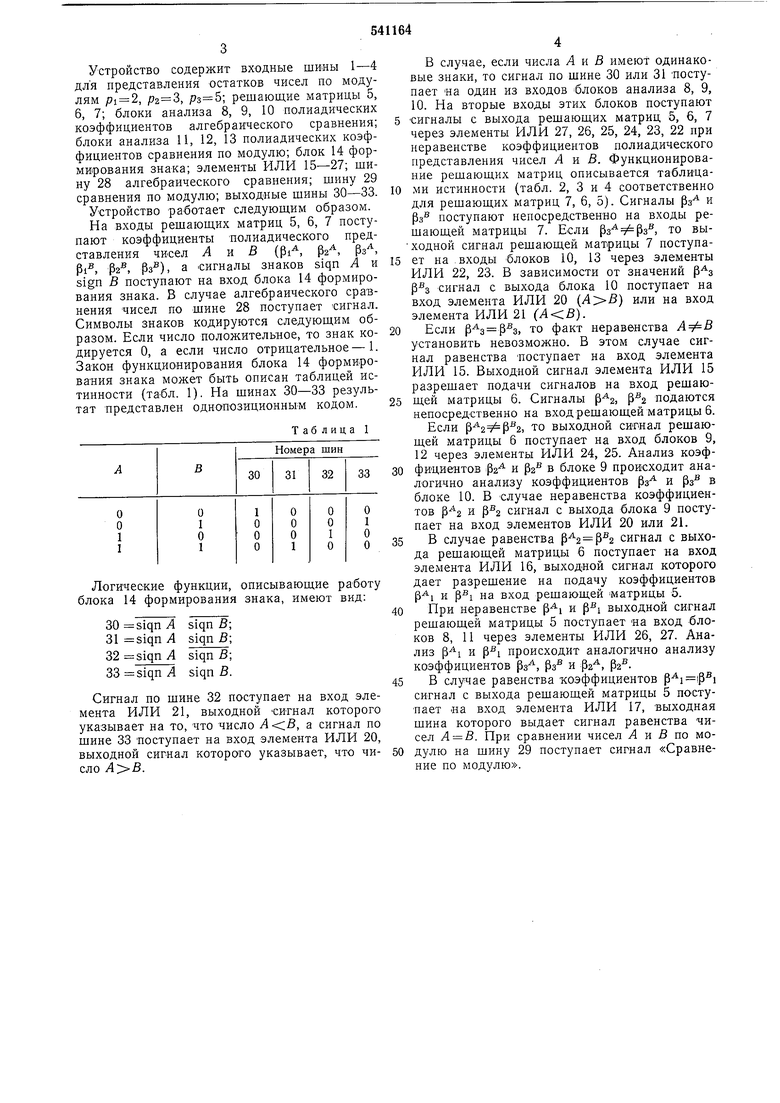

Таблица 4

Этот сигнал поступает на один из выходов блоков анализа 13, 12, И полиадических коэффициентов сравнения по модулю. На вторые входы этих блоков поступают сигналы с выхода решающих матриц 7, 6, 5 через элеменщ ИЛИ 22-27 при условии неравенства

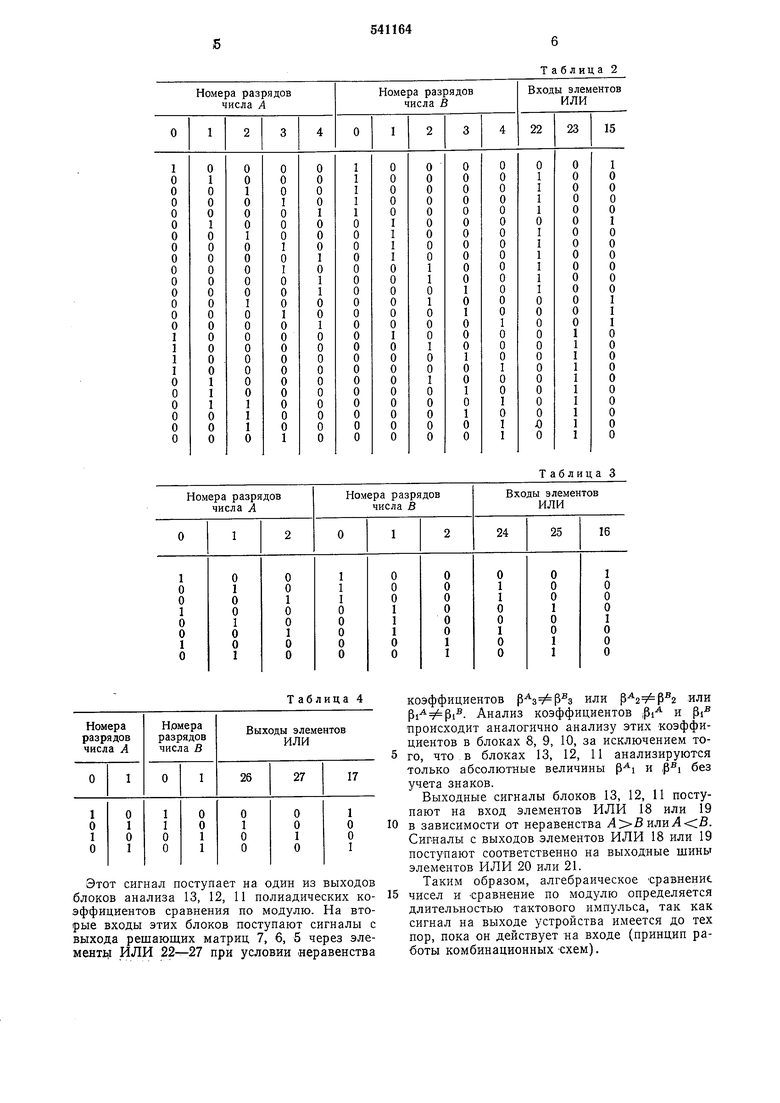

Таблица 3

коэффициентов или или . Анализ коэффициентов ;pi и piпроисходит аналогично анализу этих коэффициентов в блоках 8, 9, 10, за исключением того, что в блоках 13, 12, 11 анализируются только абсолютные величины и . без учета знаков.

Выходные сигналы блоков 13, 12, 11 поступают на вход элементов ИЛИ 18 или 19

в зависимости от неравенства Л ВилиЛ В.

Сигналы с выходов элементов ИЛИ 18 или 19

поступают соответственно на выходные шины

элементов ИЛИ 20 или 21.

Таким образом, алгебраическое сравнение

чисел и сравнение по модулю определяется длительностью тактового импульса, так как сигнал на выходе устройства имеется до тех пор, пока он действует на входе (принцип работы комбинационныхСхем).

Пример. Пусть -необходимо сравнить два числа Л(122) и В(022). Siqn Л 0, siqn В 0.

Прохождение си-гналов на схеме изображено пунктиром. На вход решающих матриц поступают следующие сигналы:

решающая матрица 7-,, z 2,

решающая матрица , (2 2;

решающая матрица l, 0.

На вход блока 14 поступают сигналы sinq А 0,

siqn В 0 и сигнал по шине 28.

С выхода решающей матрицы 7 сигнал поступает на элемент ИЛИ 15, так как р з |р зВыходной сигнал элемента ИЛИ 15 разрешает прохождение сигналов и на вход решающей матрицы 6. С выхода решающей матрицы 6 сигнал поступает «а вход элемента ИЛИ 16, так как . Выходной сигнал элемента ИЛИ 16 разрещает прохождение сигналов , и на вход решающей матрицы 5. Выходной сигнал решающей матрицы 5 поступает на один из входов блока 8. На второй вход поступает сигнал С выхода блока 14. На основании полученных сигналов блок 8 выдает сигнал на элемент ИЛИ 20, выходной сигнал которого соответствует условию .

Для других значений коэффициентов работа устройства аналогична.

Таким образом, предлагаемое устройство обладает большими функциональными возможностями, чем известные, так как позволяет сравнивать числа, представленные в системе остаточных классов по признакам больше- меньше.

Формула изобретения

Устройство для сравнения чисел, содержащее п решающих матриц, где п число модулей разложения, п блоков анализа полиадических коэффициентов алгебраического сравнения и п блоков анализа полиадических коэффициентов сравнения но модулю, блок формирования знака, элементы ИЛИ, причем выходные шины одноименных знаков блока формирования знака соединены с входами блоков анализа полиадических коэффициентов алгебраического сравнения, а выходные шины разноименных знаков блока формирования знака соединены с входами первого и второго элементов ИЛИ соответственно, отличающееся тем, что, с целью расширения функциональных возможностей, в нем выходы каждой t-й решающей матрицы (, 3,..., п)

соединены с входами промежуточного элемента ИЛИ, выход которого подключен к входу (i-1)-й решающей матрицы, а выход первой решающей матрицы соединен с входами промежуточного элемента ИЛИ, выход которого

подключен к выходной шине устройства, другие выходы решающих матриц через элементы ИЛИ соединены с входами соответствующих блоков анализа полиадических коэффициентов алгебраического сравнения и блоков

анализа полиадических коэффициентов сравнения но модулю, один из выходов которых подключен к входам третьего элемента ИЛИ, а другие - к входам четвертого элемента ИЛИ, выходы которых соединены с входами

первого и второго элементов ИЛИ соответственно, другие входы которых подключены к соответствующим выходам блоков анализа полиадических коэффициентов алгебраического сравнения.

Источники информации, принятые во внимание при экспертизе.

Авторы

Даты

1976-12-30—Публикация

1974-05-06—Подача