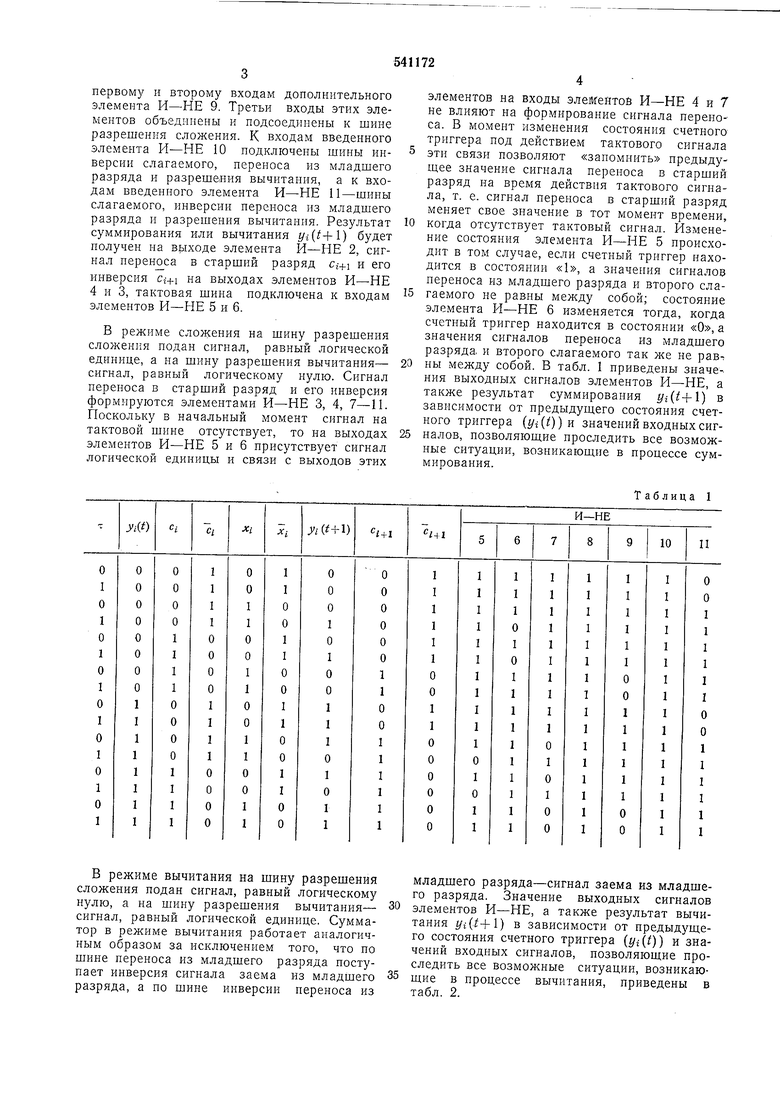

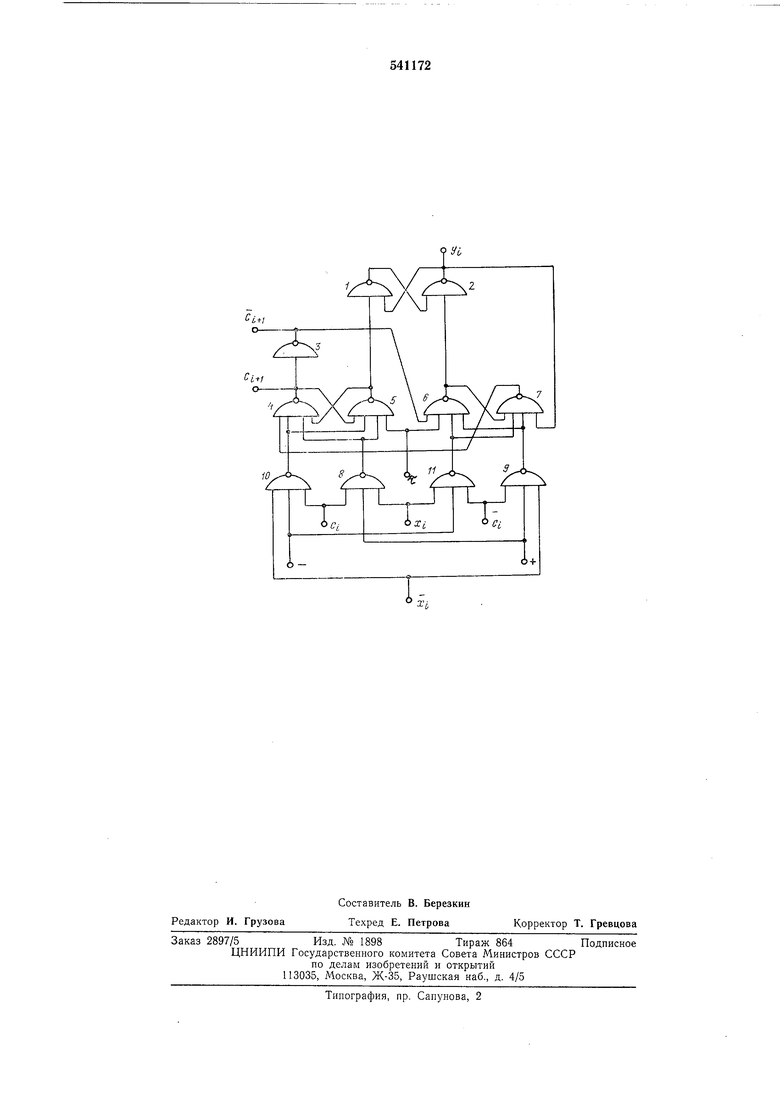

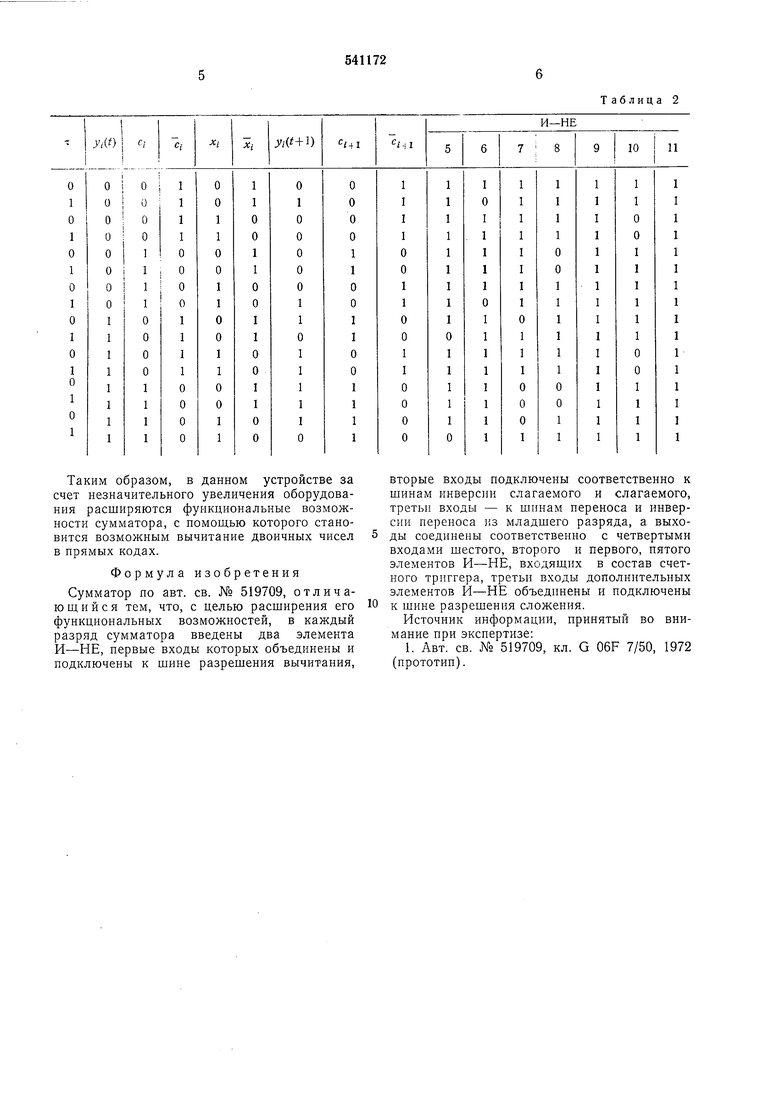

первому и второму входам дополнительного элемеита И-НЕ 9. Третьи входы этих элементов объединены и подсоединены к шиие разрешения сложения. К входам введенного элемента И-НЕ 10 подключены шины ий-5 версии слагаемого, переноса из младшего разряда и разрешения вычитания, а к входам введенного элемента И-НЕ 11-шины слагаемого, инверсии переиоса из младшего разряда и разрешения вычитания. Результат10 суммирования или вычитания yi(t+l) будет иолучен на выходе элемента И-НЕ 2, сигнал иереиоса в старший разряд Cj+j и его инверсия й+1 иа выходах элементов И-НЕ 4 и 3, тактовая шина подключена к входам5 элементов ИНЕ 5 и 6. В режиме сложения на шину разрешения сложения подан сигнал, равный логической единице, а иа шину разрешения вычитания-20 сигнал, равный логическому нулю. Сигнал переноса в старший разряд и его инверсия формируются элементами И-НЕ 3, 4, 7-11. Поскольку в начальный момент сигнал на тактовой шине отсутствует, то на выходах25 элемеитов И-НЕ 5 и 6 присутствует сигнал логической единицы и связи с выходов этих элементов на входы элемейтой И-НЕ 4 и 7 не влияют на формирование сигнала переноса. В момент изменения состояния счетного триггера под действием тактового сигнала эти связи позволяют «запомнить предыдущее значение сигнала переноса в старший разряд на время действия тактового сигнала, т. е. сигнал переноса в старший разряд меняет свое значение в тот момент времени. когда отсутствует тактовый сигнал. Йзменение состояния элемеита И-НЕ 5 происходит в том случае, если счетный триггер иаходится в состояиии «1, а зиачения сигналов переноса из младшего разряда и второго слагаемого ие равны между собой; состояние элемента И-НЕ 6 изменяется тогда, когда счетный триггер находится в состоянии «О, а значения сигналов переноса из младшего разряда, и второго слагаемого так же не рав-; ны между собой. В табл. 1 приведены значения выходных сигналов элементов И-НЕ, а также результат суммирования yi{t+l) в зависимости от предыдущего состояиия счетного триггера (t/i(t)) и значений входных сигналов, позволяющие проследить все возможные ситуации, возникающие в процессе суммирования. Таблица 1

| название | год | авторы | номер документа |

|---|---|---|---|

| ДВОИЧНО-ДЕСЯТИЧНЫЙ НАКАПЛИВАЮЩИЙ СУММАТОР | 1971 |

|

SU293241A1 |

| Сумматор | 1974 |

|

SU541173A2 |

| ПАРАЛЛЕЛЬНЫЙ СУММАТОР-ВЫЧИТАТЕЛЬ НА НЕЙРОНАХ СО СКВОЗНЫМ ПЕРЕНОСОМ | 2012 |

|

RU2523942C2 |

| СУММАТОР-ВЫЧИТАТЕЛЬ СТАРШИМИ РАЗРЯДАМИ ВПЕРЕД НА НЕЙРОНАХ | 2002 |

|

RU2205444C1 |

| ПОСЛЕДОВАТЕЛЬНЫЙ ДЕЛИТЕЛЬ ТРОИЧНЫХ ЦЕЛЫХ ЧИСЕЛ | 2023 |

|

RU2810609C1 |

| ПАРАЛЛЕЛЬНЫЙ СУММАТОР | 1972 |

|

SU342186A1 |

| Устройство для суммирования с услов-НыМ пЕРЕНОСОМ | 1979 |

|

SU824196A1 |

| Фазоимпульсный сумматор | 1980 |

|

SU885996A1 |

| НАКАПЛИВАЮЩИЙ СУММАТОР | 1970 |

|

SU273519A1 |

| Сумматор параллельного действия | 1974 |

|

SU531157A1 |

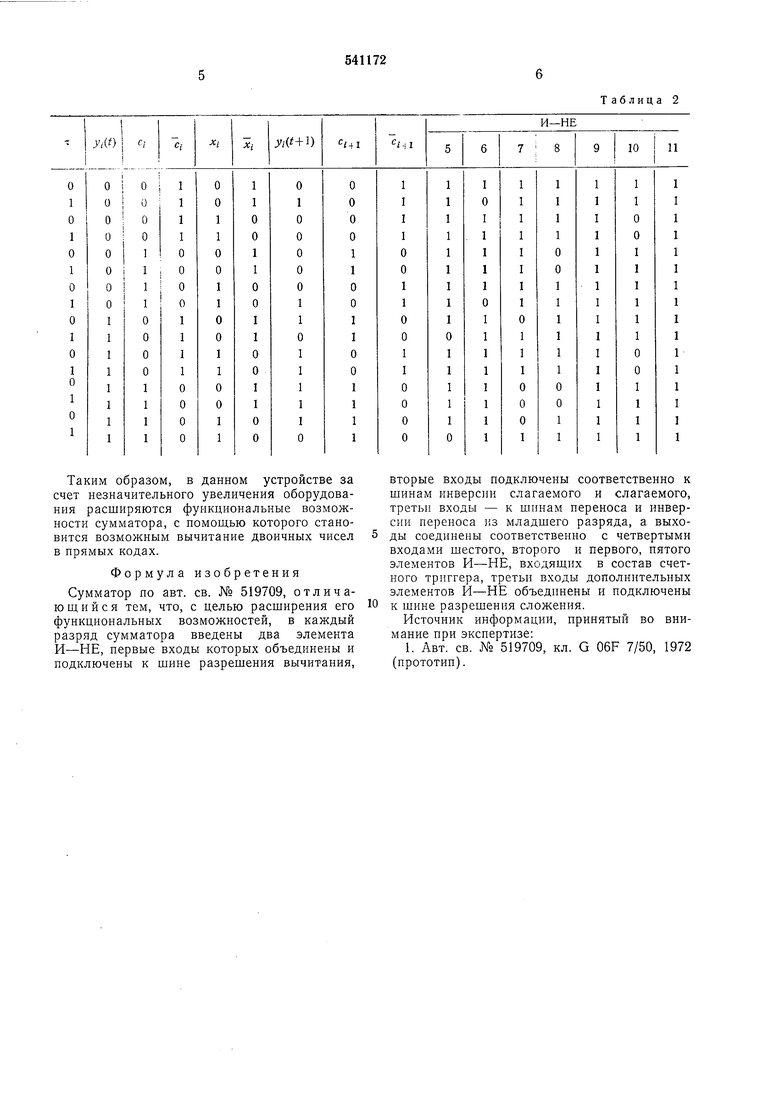

В режиме вычитания на шину разрешения сложения подан сигнал, равный логическому нулю, а на шину разрещения вычитания- сигнал, равный логической единице. Сумматор в режиме вычитания работает аналогичным образом за исключением того, что по шине переноса из младшего разряда поступает инверсия сигнала заема из младшего разряда, а по шине инверсии переиоса из

младшего разряда-сигнал заема из младшего разряда. Значение выходных сигналов элементов И-НЕ, а также результат вычитания yi{t+) в зависимости от предыдущего состояния счетного триггера (г/г(0) и значений входных сигналов, позволяющие проследить все возможные ситуации, возникающие в процессе вычитания, приведены в табл. 2.

Таким образом, в данном устройстве за счет незначительного увеличения оборудования расширяются функциональные возможности сумматора, с номощью которого становится возможным вычитание двоичных чисел в прямых кодах.

Формула изобретения

Сумматор по авт. св. № 519709, отличающийся тем, что, с целью расширения его функциональных возможностей, в каждый разряд сумматора введены два элемента И-НЕ, первые входы которых объединены и подключены к шине разрешения вычитания.

Таблица 2

вторые входы цодключены соответственно к шинам инверсии слагаемого и слагаемого, третьи входы - к шинам переноса и инверсии переноса из младшего разряда, а выходы соединены соответственно с четвертыми входами шестого, второго и первого, пятого элементов И-НЕ, входящих в состав счетного триггера, третьи входы дополнительных элементов И-НЕ объединены и подключены к шине разрешения сложения.

Источник информации, принятый во внимание цри экспертизе:

i+/

Авторы

Даты

1976-12-30—Публикация

1974-04-05—Подача